Panasonic KV-S5055C (serv.man2) Service Manual ▷ View online

121

10.3. Requirement After Parts Replacement

Replaced circuit board assembly or part

Required adjustment

Remarks

IC0007 (Flash memory on CONTROL Board) or

CONTROL Board

CONTROL Board

1. Adjust Shading.

IC0004 (EEPROM on CONTROL Board) or CONTROL

Board

Board

1. Adjust Shading.

2. Adjust Individual position manually, as required.

3. Execute Double Feed (See 9.3.7) to adjust double

feed sensitivity.

2. Adjust Individual position manually, as required.

3. Execute Double Feed (See 9.3.7) to adjust double

feed sensitivity.

4. Execute Bent Paper Sensor (See 9.3.7.) to adjust

sensor level.

5. Set USB ID. (See 9.3.7.)

5. Set USB ID. (See 9.3.7.)

Note:

When the initial settings to this product are other than

the default (factory setting), this scanner will require

the resetting.

the default (factory setting), this scanner will require

the resetting.

(Item) (Default (Factory Setting))

Sleep Mode 15 minutes

Caution Setting (Roller Cleaning Timing) 20,000

Caution Setting (Roller Replacement Timing) 350,000

Feed Speed 100 %

Caution Setting (Roller Cleaning Timing) 20,000

Caution Setting (Roller Replacement Timing) 350,000

Feed Speed 100 %

Starting Sensor or STARTING SENSOR Board

1. Adjust Vertical Position (for Front and Back) and

Length in individual Position or adjust All Position

Length in individual Position or adjust All Position

USS Waiting Board

1. Execute Double Feed (See 9.3.7) to adjust double

feed sensitivity.

feed sensitivity.

USR Board

1. Execute Double Feed (See 9.3.7) to adjust double

feed sensitivity.

feed sensitivity.

Optical Unit Front

1. Adjust Shading.

2. Adjust All Position or the following adjustment should

be needed.

2. Adjust All Position or the following adjustment should

be needed.

a. Adjust Front Vertical Position in Individual

Position.

b. Adjust Front Horizontal Position in Individual

Position.

Optical Unit Back

1. Adjust Shading.

2. Adjust All Position or the following adjustment should

be needed.

a. Adjust Back Vertical Position in Individual Position.

b. Adjust Back Horizontal Position in Individual

2. Adjust All Position or the following adjustment should

be needed.

a. Adjust Back Vertical Position in Individual Position.

b. Adjust Back Horizontal Position in Individual

Position.

Reference Plate (F)

1. Adjust Shading.

Reference Plate (B)

1. Adjust Shading.

Drive Roller

1. Adjust Vertical Position (for Front and Back) and

Length in individual Position or adjust All Position.

Length in individual Position or adjust All Position.

Exit Roller

1. Adjust Vertical Position (for Front and Back) and

Length in individual Position or adjust All Position

Length in individual Position or adjust All Position

Others (when assembling or disassembling parts which

will affect the scanning positions.)

will affect the scanning positions.)

1. Adjust the following adjustment or All Position.

a. Adjust Front Vertical Position in Individual

Position.

b. Adjust Front Horizontal Position in Individual

Position.

c. Adjust Back Vertical Position in Individual

Position.

d. Adjust Back Horizontal Position in Individual

Position.

BENT PAPER S(L) SENSOR Board

BENT PAPER S(R) SENSOR Board

BENT PAPER R(L) SENSOR Board

BENT PAPER R(R) SENSOR Board

BENT PAPER S(R) SENSOR Board

BENT PAPER R(L) SENSOR Board

BENT PAPER R(R) SENSOR Board

1. Execute “Bent Paper Sensor” (See 9.3.7.) to adjust

sensor level.

sensor level.

122

11 CIRCUIT DESCRIPTION

11.1. Block Diagram-1 (Image Processing)

On this system, the CPU (IC0006) controls the operation of the USB Controller (IC0010), the Gate Arrays (ASICs: IC0035 and

IC0038), the Sensors (Paper Sensor and others), and the Motors (Paper Feed, Conveyor, DFP Pressure).

Motor pulse signals for conveying paper (Conveyor Motor) are provided from the Gate Array (ASIC: IC0035).

On the other hand, motor pulse signals for the other motors are provided from the CPU (IC0006).

IC0038), the Sensors (Paper Sensor and others), and the Motors (Paper Feed, Conveyor, DFP Pressure).

Motor pulse signals for conveying paper (Conveyor Motor) are provided from the Gate Array (ASIC: IC0035).

On the other hand, motor pulse signals for the other motors are provided from the CPU (IC0006).

The FPGA (IC0030) requires SDRAM (IC0033) as the buffer memory.

The Gate Array (IC0035) requires SDRAM (IC0040 and IC0041) to store and output pre-processed and post-processed image data

for the front side. An additional memory (SO-DIMM) can be installed in CN0017 for image data output.

The FPGA (IC0031) requires SDRAM (IC0034) as the buffer memory.

The Gate Array (IC0038) requires SDRAM (IC0042 and IC0043) to store and output pre-processed and post-processed image data

for the back side. An additional memory (SO-DIMM) can be installed in CN0018 for image data output.

The Gate Array (IC0035) requires SDRAM (IC0040 and IC0041) to store and output pre-processed and post-processed image data

for the front side. An additional memory (SO-DIMM) can be installed in CN0017 for image data output.

The FPGA (IC0031) requires SDRAM (IC0034) as the buffer memory.

The Gate Array (IC0038) requires SDRAM (IC0042 and IC0043) to store and output pre-processed and post-processed image data

for the back side. An additional memory (SO-DIMM) can be installed in CN0018 for image data output.

In order to perform duplex scanning, this scanner has 2 CCDs (CCD (F), CCF (B)) to scan image signals for the front and back

sides.

The FPGA (ASIC: IC0030) receives front image signals from the AD converters (IC5007) on the CCD (F) Board, and then performs

the line correction for them. After that, the Gate Array (IC0035) pre-processes them.

The FPGA (ASIC: IC0031) receives back image signals from the AD converters (IC5007) on the CCD (B) Board, and then performs

the line correction for them. After that, the Gate Array (IC0038) pre-processes them.

(Pre-process means shading correction and dpi transformation)

sides.

The FPGA (ASIC: IC0030) receives front image signals from the AD converters (IC5007) on the CCD (F) Board, and then performs

the line correction for them. After that, the Gate Array (IC0035) pre-processes them.

The FPGA (ASIC: IC0031) receives back image signals from the AD converters (IC5007) on the CCD (B) Board, and then performs

the line correction for them. After that, the Gate Array (IC0038) pre-processes them.

(Pre-process means shading correction and dpi transformation)

After finishing pre-processing, the Gate Arrays (IC0035 and IC0038) post-process the data into binary or compressed data to be

sent to a PC via the USB Interface.

(Post-process means binary processing (simple binary, auto binary, dither, error diffusion), color, and gray scale

image processing (MTF, Color Correction, Gamma Correction, etc.).)

sent to a PC via the USB Interface.

(Post-process means binary processing (simple binary, auto binary, dither, error diffusion), color, and gray scale

image processing (MTF, Color Correction, Gamma Correction, etc.).)

123

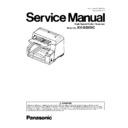

11.2. Block Diagram-2 (Board)

0

0

1

C

C

A

㨪㨪

5.

0/

V

0

4

2

㨪

0.

1A

h

cti

w

S

r

e

w

o

P

t

el

nI

C

C

A

F

a

n

Door Switch

r

e

p

a

P

d

e

e

F

r

ot

o

M

r

o

y

e

v

n

o

C

r

ot

o

M

dr

a

o

B

L

E

N

A

P

dr

a

o

B

Y

Y

A

L

E

R

R

R

S

U

R

O

S

N

E

S

G

G

NI

T

R

A

T

S

dr

a

o

B

/

S

S

S

U

R

O

S

N

E

S

G

G

NI

TI

A

W

W

dr

a

o

B

dr

a

o

B

L

O

R

T

N

O

C

R

E

Z

Z

U

B

dr

a

o

B

Y

Y

A

L

E

R

S

S

S

U

D

E

L

S

/

S

3

0

0

3

N

C

8

0

0

3

N

C

7

0

0

2

N

C

6

0

0

2

N

C

5

0

0

2

N

C

2

0

0

2

N

C

1

0

0

2

N

C

6

0

0

4

N

C

3

0

0

4

N

C

7

0

0

1

N

C

8

0

0

1

N

C

r

et

ni

r

p

mi

-

er

P

ti

n

U

㧔

)

n

oi

t

p

O

1

0

0

3

N

C

B

S

U

1

0

8

N

C

CN842

1

0

0

1

K

J

0

1

0

1

N

C

r

o

s

n

e

S

r

e

p

a

P

R

S

U

R

O

S

N

E

S

dr

a

o

B

dr

a

o

B

E

E

VI

R

D

D

E

L

eti

h

W-

W-

o

d

u

e

s

P

dr

a

o

B

)

F(

D

D

C

C

3

0

0

5

N

C

)

6

1

7

2

D

C

T(

D

C

C

E

F

A

dr

a

o

B

)

B(

D

D

C

C

3

0

0

5

N

C

)

6

1

7

2

D

C

T(

D

C

C

E

F

A

4

0

0

1

N

C

6

0

0

1

N

C

5

0

0

3

N

C

0

1

0

3

N

C

CN3014

CN3011

6

0

0

3

N

C

T

N

E

B

R

E

P

A

P

R

O

S

N

E

S

)

R(

S

dr

a

o

B

T

N

E

B

R

E

P

A

P

R

O

S

N

E

S

)

L(

R

dr

a

o

B

T

N

E

B

R

E

P

A

P

R

O

S

N

E

S

)

L(

S

dr

a

o

B

T

N

E

B

R

E

P

A

P

R

O

S

N

E

S

)

R(

R

dr

a

o

B

CN4002

CN4001

CN1002

CN1001

4

0

0

2

N

C

r Board

e

zi

n

oI

e

zi

n

oI

r

t

e

k

c

o

S

M

M

MI

D

O

S

t

e

k

c

o

S

M

M

MI

D

O

S

X

S

8

H

0

5

6

1

)

1

5

6

1:

E

CI

(

CN1014

CN1015

l

air

e

s

P

F

D

er

u

s

s

er

P

r

ot

o

M

2

F

P

2

F

P

M

A

R

D

S

i

b

M

4

6

t

M

A

R

D

S

i

b

M

4

6

t

M

A

R

D

S

i

b

M

4

6

t

M

A

R

D

S

i

b

M

4

6

t

A

G

P

F

e

vi

e

c

e

R

S

S

D

V

L

r

e

vi

e

c

e

R

S

S

D

V

L

r

A

G

P

F

DDR2

DDR2

C

B

S

U

2

1

0

1

N

C

3

1

0

1

N

C

2

0

0

5

N

C

3

0

0

1

N

C

2

0

0

5

N

C

5

0

0

1

N

C

2

1

0

3

N

C

CN3015

CN3013

l

e

c

n

a

C

OI

A

G

D

L

P

D

E

L

eti

h

W-

W-

o

d

u

e

s

P

2

0

0

3

N

C

3

0

0

2

N

C

E

M

O

H

P

P

F

D

R

O

S

N

E

S

dr

a

o

B

T

C

E

T

E

D

PI

PI

L

S

dr

a

o

B

R

R

O

S

N

E

S

D

E

E

F

R

R

E

P

A

P

R

O

S

N

E

S

T

C

E

L

E

S

dr

a

o

B

CN1016

G

A

T

J

A

A

G

P

F

87831

6

1

0

1

N

C

P

O

W

E

R

B

o

a

rd

A4

es

u

F

A3.

6

es

u

F

V4

2

ot

tr

ev

no

C

10

8

F

14

8

F

r

ot

o

M

r

e

vir

D

A4

C

D-

C

D

A3/

V3.

3

4

0

0

4

N

C

5

0

0

4

N

C

9

0

0

4

N

C

A4

A4

A4

r

ot

o

M

r

e

vir

D

r

ot

o

M

r

e

vir

D

D

E

L

r

e

vir

D

8

0

0

4

N

C

D

E

L

r

e

vir

D

7

0

0

4

N

C

C

D-

C

D

A5.

3/

V4

1

A4

57.

0

57.

0

N

A-

P

E

EL

S

X

A4

U

P

C

V3.

3

C

D-

C

D

A5.

3/

V3.

3

G

OL

-

P

E

EL

S

X

C

D-

C

D

A

5.

1/

V

5

A4

A4

A4

1.

0

PL

S

V3.

3

E

CI

M

O

R

r

of

dr

a

o

B

U

P

C

3.

3

H

S

A

L

F

ti

b

M

8

M

A

R

S

ti

b

M

1

M

O

R

P

E

E

U

P

C

V3.

3

PL

S

V3.

3

es

u

F

hct

i

ws

yl

o

P

V5

A1.

1

PL

S

V5

9

0

0

1

N

C

PL

S

V5

PL

S

V5

V4

2_

SJ

V4

1

A5.

0/

V2

1

sei

re

S

V2

1

V4

2_

SJ

V4

1

A5.

0

PL

S

V3.

3

V2

1

V4

2_

SJ

PL

S

V3.

3

V2

1

PL

S

V3.

3

V5

V2

1

PL

S

V3.

3

V5

V2

1

A1

3-

H

E

1

N

C

dr

a

o

B

Y

Y

A

L

E

R

T

N

E

B

0

1

0

2

N

C

CN2011

CN3009

7

0

0

3

N

C

CN2009

CN3004

CN2014

CN2013

CN2008

V5.

2

sei

re

S

V8.

1

sei

re

S

V2.

1

sei

re

S

V9.

0

sei

re

S

V8.

1

sei

re

S

V

8.

1

sei

re

S

dr

a

o

B

D

D

E

L

dr

a

o

B

D

D

E

L

G

NI

D

N

E

R

O

S

N

E

S

dr

a

o

B

10

04

F

10

04

F

C

40

04

F

30

04

F

C

20

04

F

C

V4

2_

SJ

C

D-

C

D

V7.

21

CN841

6

0

0

4

N

C

3

0

0

4

N

C

dr

a

o

B

E

E

VI

R

D

CN4002

CN4001

r

ot

o

M

r

e

vir

D

4

A

C

D-

C

D

4

0

0

4

N

C

5

0

0

4

N

C

9

0

0

4

N

C

4A

4

A

4

A

r

ot

o

M

r

e

vir

D

r

ot

o

M

r

e

vir

D

D

E

L

r

e

vir

D

8

0

0

4

N

C

D

E

L

r

e

vir

D

7

0

0

4

N

C

C

D-

C

D

14V/3.5A

4

A

4

A

-AN

P

E

E

L

S

X

4

A

U

P

C

V

3.

3

C

D-

C

D

G

O

L-

P

E

E

L

S

X

C

D-

C

D

A

5.

1/

V

5

4

A

4

A

4A

1.

0

P

L

S

V

3.

3

1

A

01

0

4

F

2

1

0

4

F

10

0

4

F

03

0

4

F

02

0

4

F

06

0

4

F

05

0

4

F

07

0

4

F

08

0

4

F

09

0

4

F

C

D-

C

D

5.

3/

V

0

1

A

01

0

4

F

C

3.3V/3.5A

3.3V/3A

124

11.3. Explanation of Connector

CN1003 (CONTROL Board) - CN5002 (CCD (F) Board)

Pin No.

Signal Name

Description

CN1003

CN5002

1

1

RCLK_F

LVDS RCLK+

2

2

*RCLK_F

LVDS RCLK-

3

3

RB_F

LVDS RB+

4

4

*RB_F

LVDS RB-

5

5

RA_F

LVDS RA+

6

6

*RA_F

LVDS RA-

7

7

RE_F

LVDS RE+

8

8

*RE_F

LVDS RE-

9

9

RD_F

LVDS RD+

10

10

*RD_F

LVDS RD-

11

11

RC_F

LVDS RC+

12

12

*RC_F

LVDS RC-

13

13

GND

Ground

14

14

GND

Ground

CN1004 (CONTROL Board) - CN5003 (CCD (F) Board)

Pin No.

Signal Name

Description

CN1004

CN5003

1

13

12V

12V supply

2

12

GND

Ground

3

11

5V

5V supply

4

10

GND

Ground

5

9

3.3V

3.3V supply

6

8

GND

Ground

7

7

AFE_CLK

AFE serial clock

8

6

AFE_SDI

AFE serial data in

9

5

AFE_SENF

AFE serial enable

10

4

LSYNC_F

Line sync

11

3

*SRES

Reset

12

2

AFE_SDOF

AFE serial data out

13

1

CCD_REVF

CCD_AFE Board revision

CN1005 (CONTROL Board) - CN5002 (CCD (B) Board)

Pin No.

Signal Name

Description

CN1005

CN5002

1

1

RCLK_B

LVDS RCLK+

2

2

*RCLK_B

LVDS RCLK-

3

3

RB_B

LVDS RB+

4

4

*RB_B

LVDS RB-

5

5

RA_B

LVDS RA+

6

6

*RA_B

LVDS RA-

7

7

RE_B

LVDS RE+

8

8

*RE_B

LVDS RE-

9

9

RD_B

LVDS RD+

10

10

*RD_B

LVDS RD-

11

11

RC_B

LVDS RC+

12

12

*RC_B

LVDS RC-

13

13

GND

Ground

14

14

GND

Ground

15

—

N.C.

N.C.

16

—

N.C.

N.C.

Click on the first or last page to see other KV-S5055C (serv.man2) service manuals if exist.