Sharp SD-CX1 (serv.man5) Service Manual ▷ View online

SD-CX1H

– 16 –

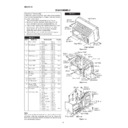

Figure 16-1

How to remove the MD spindle motor

(See Fig. 16-1)

(See Fig. 16-1)

1. Remove the screws (D1) x 3 pcs., and remove the MD

spindle motor.

Caution:

Be careful so that the gear is not damaged.

(The damaged gear emits noise during searching.)

(The damaged gear emits noise during searching.)

CD MECHANISM SECTION

Perform steps 1 to 11 of the disassembly method to remove

the CD mechanism. (See page 13.)

the CD mechanism. (See page 13.)

Note:

After removing the connector for the optical pickup from the

connector, wrap the conductive aluminium foil around the

front end of connector remove to protect the optical pickup

from electrostatic damage.

After removing the connector for the optical pickup from the

connector, wrap the conductive aluminium foil around the

front end of connector remove to protect the optical pickup

from electrostatic damage.

Figure 16-2

Figure 16-3

How to Remove the CD lid motor

(See Fig. 16-3.)

(See Fig. 16-3.)

1. Remove the front panel.

(Refer to the disassembly method on page 12.)

2. Remove the screws (B1) x 4 pcs.

3. Remove the CD lid gear unit from the front panel.

4. Remove the screws (B2) x 5 pcs. to remove the gear box

3. Remove the CD lid gear unit from the front panel.

4. Remove the screws (B2) x 5 pcs. to remove the gear box

B.

5. Remove the gear (B3) x 1 pc.

6. Remove the screws (B4) x 2 pcs. to remove the CD lid

6. Remove the screws (B4) x 2 pcs. to remove the CD lid

motor.

(D1)x3

ø1.4x 3mm

MD Spindle Motor

(A2) x2

ø2.6 x6mm

ø2.6 x6mm

(A1) x4

Shaft

(A3) x1

(A3) x1

Gear

(A5) x1

(A5) x1

Stop Washer

(A4) x1

(A4) x1

CD Mechanism Cover

CD Mechanism

Pickup

How to remove the pickup (See Fig. 16-2)

1. Remove the mechanism cover, paying attention to the

pawls (A1) x 4 pcs.

2. Remove the screws (A2) x 2 pcs., to remove the shaft

(A3) x 1 pc.

3. Remove the stop washer (A4) x 1 pc., to remove the

gear (A5) x 1 pc.

4. Remove the pickup.

Caution:

Be careful not to damage the gear.

(If the gear is damaged, noise is heard when searching.)

(If the gear is damaged, noise is heard when searching.)

Gear Box A

CD Lid Motor

(B4)x2

ø2x5mm

ø2x5mm

Gear

(B3)x1

(B3)x1

Gear Box B

(B2)x5

ø2x10mm

ø2x10mm

(B1)x4

ø3x10mm

ø3x10mm

CD Lid Gear Unit

CD Lid

Motor

Motor

Front Panel

– 17 –

SD-CX1H

DESCRIPTION OF CIRCUIT FOR 1-BIT AMP. UNIT

(SEE THE WIRING DIAGRAMS ON PAGES 52 AND 53.)

Input

Signals over certain level input from BIA106 are sliced into waveforms by RA173 (RA174), DA126, and DA127 (DA128, DA129).

The slice levels depend on the output of the unit.

In case of 25 W output setting, the level is set to gain distortion of approx. 10 % during output.

The level on the positive side is determined by RA175, RA177 and RA179 and that on the negative side by RA176, RA178, and

RA180, respectively.

After DC cut by CA108, the signals are input to AD conversion IC.

Signals over certain level input from BIA106 are sliced into waveforms by RA173 (RA174), DA126, and DA127 (DA128, DA129).

The slice levels depend on the output of the unit.

In case of 25 W output setting, the level is set to gain distortion of approx. 10 % during output.

The level on the positive side is determined by RA175, RA177 and RA179 and that on the negative side by RA176, RA178, and

RA180, respectively.

After DC cut by CA108, the signals are input to AD conversion IC.

modulation 1-bit conversion

The signals input to the AD conversion IC are converted into 1-bit signals for differential output.

For detailed technical description of 1-bit signal conversion, refer the technical manual for SM-SX100 already published.

The signals input to the AD conversion IC are converted into 1-bit signals for differential output.

For detailed technical description of 1-bit signal conversion, refer the technical manual for SM-SX100 already published.

Dead time and level shift

When the 1-bit signals are output from the AD conversion IC, the leading edge of the waveform is delayed for 20 to 25 nsec by

DA103 (DA102, DA101, and DA100), RA115 (RA114, RA113, and RA112), and CA155 (CA154, CA153, and CA152), compared

with the trailing edge.

As mentioned below, this operation is for reducing switching circuit loss in the final stage.

The signals are input to the buffer IC (AND gate IC) for the waveform format and are output.

Then the DC level is shifted by CA115 (CA114, CA113, and CA112), DA107 (DA106, DA105, and DA104) and RA120 (RA119,

RA118, and RA117). This is because the buffer IC operates between ground and + 5 V, while the next stage IC, gate driver (ICA101

to ICA 104), operates between the negative power source and + 9 V.

The shift quantity is output with amplitude of 5 V, based on the voltage raised by DA108 and DA109 from the bottom by approx.

2 V.

When the 1-bit signals are output from the AD conversion IC, the leading edge of the waveform is delayed for 20 to 25 nsec by

DA103 (DA102, DA101, and DA100), RA115 (RA114, RA113, and RA112), and CA155 (CA154, CA153, and CA152), compared

with the trailing edge.

As mentioned below, this operation is for reducing switching circuit loss in the final stage.

The signals are input to the buffer IC (AND gate IC) for the waveform format and are output.

Then the DC level is shifted by CA115 (CA114, CA113, and CA112), DA107 (DA106, DA105, and DA104) and RA120 (RA119,

RA118, and RA117). This is because the buffer IC operates between ground and + 5 V, while the next stage IC, gate driver (ICA101

to ICA 104), operates between the negative power source and + 9 V.

The shift quantity is output with amplitude of 5 V, based on the voltage raised by DA108 and DA109 from the bottom by approx.

2 V.

Output of gate driver

The level-shifted signals are input to the gate driver IC (HIP2100).

Since the final stage FET array is H bridge, two gate drivers are used for 1 CH.

At this time, + and - of differential signals are input by crossing diagonally for the two gate drivers.

(Positive output to ICA101 (ICA103) Hin and ICA102 (ICA104) Lin, and negative output to ICA102 (ICA104) Hin and ICA101

(ICA103) Lin.)

Output of the gate driver drives the gate of FET array connected to H bridge.

FET consists of the lower stage where source is connected to the negative power and the upper stage where drain is connected

to the positive power. Lout and Hout are connected to the gate, respectively.

The lower stage FET is driven with 9 V amplitude based on the negative power because the reference voltage is same as in the

gate driver. The upper stage FET does not operate as it is because it is based on the positive power. Therefore this gate drive IC

(HIP2100) makes up bootstrap, by feeding back from FET output.

As a result, amplitude of Hout is approx. + 6V of the positive power, based on the negative power.

The level-shifted signals are input to the gate driver IC (HIP2100).

Since the final stage FET array is H bridge, two gate drivers are used for 1 CH.

At this time, + and - of differential signals are input by crossing diagonally for the two gate drivers.

(Positive output to ICA101 (ICA103) Hin and ICA102 (ICA104) Lin, and negative output to ICA102 (ICA104) Hin and ICA101

(ICA103) Lin.)

Output of the gate driver drives the gate of FET array connected to H bridge.

FET consists of the lower stage where source is connected to the negative power and the upper stage where drain is connected

to the positive power. Lout and Hout are connected to the gate, respectively.

The lower stage FET is driven with 9 V amplitude based on the negative power because the reference voltage is same as in the

gate driver. The upper stage FET does not operate as it is because it is based on the positive power. Therefore this gate drive IC

(HIP2100) makes up bootstrap, by feeding back from FET output.

As a result, amplitude of Hout is approx. + 6V of the positive power, based on the negative power.

Low-pass filter circuit

1-bit signals switched at FET are converted into analog signals via the low-pass filter consisting of LA100 (LA102, LA104, and

LA106) and CA142 (CA143, CA150, and CA151).

Property of the low-pass filter is flat up to 20 kHz and then is attenuated by approx. 3 dB at around 30 kHz.

1-bit signals switched at FET are converted into analog signals via the low-pass filter consisting of LA100 (LA102, LA104, and

LA106) and CA142 (CA143, CA150, and CA151).

Property of the low-pass filter is flat up to 20 kHz and then is attenuated by approx. 3 dB at around 30 kHz.

Dynamic feedback circuit

1-bit signals switched at FET of output stage are amplified between the positive and negative power sources.

With resistance divided, 1-bit signals are fed back to AD conversion IC, via NF resistance 75 kohms.

P-P voltage, which becomes approx. 4 to 7V, is determined by the regulation property of the transformer depending on the output

level.

1-bit signals switched at FET of output stage are amplified between the positive and negative power sources.

With resistance divided, 1-bit signals are fed back to AD conversion IC, via NF resistance 75 kohms.

P-P voltage, which becomes approx. 4 to 7V, is determined by the regulation property of the transformer depending on the output

level.

SD-CX1H

– 18 –

TO CHECK AND CANCEL PROTECT CIRCUIT DETECTION LINE

1. After power supply, the microcomputer (ICD01) built in this model consecutively monitors the following errors 1 to 4. If any error

occurs, 'Er_AP00' is displayed and all power supply except for the one to drive the microcomputer is interrupted.

1 Abnormal output voltage drop of each regulator

1 Abnormal output voltage drop of each regulator

(below approx. 3 V)

2 Excessive output offset of 1-bit amplifier

(over approx. 2 V of DC potential)

3 Excessive main supply current of 1-bit amplifier

(over DC approx. 5.5 A)

4 Abnormalities of cooling fan motor and its driving circuit

(stop, etc.)

2. Criteria for judging errors of built-in microcomputer and checking/cancelling detection line

Condition: The voltage of microcomputer pin 7 (PROTECT) lowering below 3.5 V is regarded as an error.

(In the demonstration mode to stop cooling fan, the voltage of 1.5 V is regarded as an error.)

(In the demonstration mode to stop cooling fan, the voltage of 1.5 V is regarded as an error.)

Checking/Cancelling

Caution: When interrupting the PROTECT detection line, the microcomputer does not operate protectively. In case of an error

caused by output short-circuit of each regulator, components and board on the spot may be burnt. Do not interrupt the

PROTECT detection line of the microcomputer, if any cause other than the above mentioned is not identified.

(For approx. 0.5 seconds after error detection, power is supplied; power supply can be checked with an oscilloscope,

etc. As leading and trailing edges of the voltage are so steep that the power supply cannot be checked by the tester.)

PROTECT detection line of the microcomputer, if any cause other than the above mentioned is not identified.

(For approx. 0.5 seconds after error detection, power is supplied; power supply can be checked with an oscilloscope,

etc. As leading and trailing edges of the voltage are so steep that the power supply cannot be checked by the tester.)

1. Abnormal output voltage drop of each regulator

Connect the measuring apparatus (oscilloscope, etc.) to the stabilized output of the regulator to turn on the unit power switch.

If the stabilized output is far smaller (below approx. 3 V) than that shown in the circuit diagram, the regulator and the circuit

to be supplied with the power may be defective.

If the stabilized output is far smaller (below approx. 3 V) than that shown in the circuit diagram, the regulator and the circuit

to be supplied with the power may be defective.

2. Excessive output offset of 1-bit amplifier

After disconnecting the CNPV99 (speaker output connector of 1-bit amplifier), turn on the unit power for the normal operation.

(No sound is heard from the speaker.)

(No sound is heard from the speaker.)

* After repairing, adjust the output offset voltage of 1-bit amplifier as shown on page 24.

If the protective operation is observed even after disconnecting the CNPV99, circuits QV95 to 98 (DC voltage detection of

speaker output) may be defective.

speaker output) may be defective.

3. Excessive main supply current of 1-bit amplifier

After disconnecting the CNP801 (main power source connector of 1-bit amplifier), turn on the unit power for the normal

operation. (No sound is heard from the speaker.)

operation. (No sound is heard from the speaker.)

* After repairing, adjust the output offset voltage of 1-bit amplifier as shown in page 30.

If the protective operation is observed even after disconnecting the CNP801, the circuit of ICV98/ICV99 (supply current

detection circuit) may be defective.

detection circuit) may be defective.

4. Abnormalities of cooling fan motor and its driving circuit (stop, etc.)

Turn on the unit to visually inspect the cooling fan motor till the protective operation starts.

* If the fan is rotating forcefully;

QV94, contact of the CNPV97 (connector for fan motor), or fan may be defective. (CNPV97 pin 3 potential during normal

fan operation is approx. 0 V.)

fan operation is approx. 0 V.)

* When the fan is not rotating or seems to be stopping.

If it is checked that the CNPV97 (connector for fan motor) is not defective and it is also checked by oscilloscope, etc that

voltage of pin 1 (red line of fan) is approx. 6 V, the fan may be defective.

voltage of pin 1 (red line of fan) is approx. 6 V, the fan may be defective.

When the voltage of the CNPV97 pin (1) is far lower than 6 V, and base voltage of QV93 is almost the same as that shown

in the circuit diagram, the fan or the circuit consisting of PSV801, QV85, QV87, and QV93 may be defective.

in the circuit diagram, the fan or the circuit consisting of PSV801, QV85, QV87, and QV93 may be defective.

When the base voltage of QV85 is 0 V or extremely lower than the value shown in the circuit diagram (3.5 V), the system

control terminal of SOV90 may be defective.

control terminal of SOV90 may be defective.

– 19 –

SD-CX1H

1-BIT AMP. SECTION

Wiring diagram of the 1-bit Amp. unit

Figure 19

Core

Core

Core

1 Bit Amp. Unit

Nylon Band

Nylon Band

Nylon Band

After the wires from the 1-bit amp PWB are wound around the

cores as shown in Fig. 19, secure them to the chassis of amp

unit with nylon bands (4 pcs).

cores as shown in Fig. 19, secure them to the chassis of amp

unit with nylon bands (4 pcs).

TEST MODE

From power off state to TEST mode

Press the +10 Track Up button (+10) and MD REC LEVEL/MD Fast Forward button (

Press the +10 Track Up button (+10) and MD REC LEVEL/MD Fast Forward button (

) simultaneously while the POWER

button of the main unit is on to obtain the TEST mode. Initially, the version is displayed.

Thereafter press the MD REC LEVEL/MD Fast Forward button (

Thereafter press the MD REC LEVEL/MD Fast Forward button (

) to select the TEST mode and then press the +10 Track

Up button (+10) to determine it.

Press the DIRECT key during version display to obtain the designated TEST mode directly.

Press the DIRECT key during version display to obtain the designated TEST mode directly.

TEST MODE

No.

TEST MODE

DIRECT KEY

DISPLAY

1

CD TEST

CD PLAY (CD

)

CD MENU

2

MD TEST

MD PLAY (MD

)

MD MENU

*3

MD DISP TEST

ERASE

MD DIS MENU

*4

REC AGING

MD REC (

REC)

REC MENU

5

AUX TEST

AUX (DEMO)

AUX MENU

*6

CALENDAR TEST

CD STOP (CD

)

DATE MENU

7

KEY TEST

VOLUME UP (VOLUME

)

KEY MENU

8

TUNER TEST

TUNER/BAND

TUN MENU

*9

LINE TEST

MD STOP (MD

)

MD-LINE MENU

*10

R/P AGING

REC MODE

AGING MENU

*11

CD LID TEST

CD-OP/CL( )

OP/CL MENU

The TEST modes 3, 4, 6, 9, 10, and 11 marked with * are under technical examination; their descriptions are omitted.

Cancelling the TEST mode

In each TEST mode, press the POWER button to display COMPLETE for 1 second and then cancel the TEST mode.

In the MD TEST mode, press the POWER button again.

In the MD TEST mode, press the POWER button again.

Click on the first or last page to see other SD-CX1 (serv.man5) service manuals if exist.