Sharp LC-65XS1E (serv.man5) Service Manual ▷ View online

LC-52XS1E/RU/LC-65XS1E/RU

5 – 9

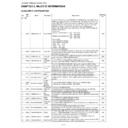

10.IC6608 (VHiBR24L64F-1Y)

This is an EEPROM, in which the portion of the data processed by the IC6201 is stored.

11.IC6651 (VHi29GL064N-1Q)

This is a 64Mb NOR flash, in which the software of IC6201 is stored.

64M FLASH MEMORY

12.IC6652 (RH-iXC623WJQZQ)

This is a 1Gb NAND flash, in which the IC6201’s data and the preinstalled pictures of the wall picture function are stored.

1Gb FLASH MEMORY

B9

SD

O

Front end shutdown signal

Positive logic

B7

TXD

O

The transmitting data signal of UART

Positive logic

B8

RXD

I

The receiving data signal of UART

Positive logic

H9

TEST

I

Test Mode

Usual '0' Fixation

C8, G2,

G8

VDDIO

-

I/O Power Supply (1.8-3.3v)

B2, E8, H3

VDDCORE

-

Core power supply (1.8V)

B6, C2,

D8, F2,

D8, F2,

H2, H8

VSS

-

Ground

Pin No.

Pin Name

I/O

Pin Function

3-12,15, 18-26,

31,54

A21-A0

I

22 Address inputs

35-42, 44-50

DQ14-DQ0

O

15 Data input/output

51

DQ15/A-1

O

DQ15 (Data input/output, at LSB word mode), A-1(LSB-Address Input, at byte mode)

32

CE#

I

Chip Enable input

34

OE#

I

Output Enable input

13

WE#

I

Write Enable input

16

WP#/ACC

I

Hardware Write Protect input/Programming Acceleration input

14

RESET#

I

Hardware Reset Pin input

17

RY/BY#

I

Ready output ; indicates the status of the Burst read./Busy output

53

BYTE#

I

Selects 8-bit or 16-bit mode

43

VCC

-

Device Power supply (3.0V)

33, 52

VSS

-

Device Ground

1, 2, 27, 28, 30,

55, 56

NC

-

Pin Not Connected Internally

29

VIO

-

Output Buffer Power

Pin No.

Pin Name

I/O

Pin Function

29-32, 41-44

IO7 - IO0

O

Data Inputs / Outputs

The IO pins allow to input command, address and data and to output data during read / pro-

gram operations. The inputs are latched on the rising edge of Write Enable (WE). The I/O

buffer float to High-Z when the device is deselected or the outputs are disabled.

The IO pins allow to input command, address and data and to output data during read / pro-

gram operations. The inputs are latched on the rising edge of Write Enable (WE). The I/O

buffer float to High-Z when the device is deselected or the outputs are disabled.

16

CLE

O

COMMAND LATCH ENABLE

This input activates the latching of the IO inputs inside the Command Register on the Rising

edge of Write Enable (WE).

This input activates the latching of the IO inputs inside the Command Register on the Rising

edge of Write Enable (WE).

17

ALE

ADDRESS LATCH ENABLE

This input activates the latching of the IO inputs inside the Address Register on the Rising

edge of Write Enable (WE).

This input activates the latching of the IO inputs inside the Address Register on the Rising

edge of Write Enable (WE).

9

CE#

I

CHIP ENABLE

This input controls the selection of the device. When the device is busy CE low does not dese-

lect the memory.

This input controls the selection of the device. When the device is busy CE low does not dese-

lect the memory.

8

WE#

I

WRITE ENABLE

This input acts as clock to latch Command, Address and Data. The IO inputs are latched on

the rise edge of WE.

This input acts as clock to latch Command, Address and Data. The IO inputs are latched on

the rise edge of WE.

18

RE#

I

READ ENABLE

The RE input is the serial data-out control, and when active drives the data onto the I/O bus.

Data is valid tREA after the falling edge of RE which also increments the internal column

address counter by one.

The RE input is the serial data-out control, and when active drives the data onto the I/O bus.

Data is valid tREA after the falling edge of RE which also increments the internal column

address counter by one.

19

WP#

I

WRITE PROTECT

The WP pin, when Low, provides an Hardware protection against undesired modify (program /

erase) operations.

The WP pin, when Low, provides an Hardware protection against undesired modify (program /

erase) operations.

Pin No.

Pin Name

I/O

Pin Function

Remarks

LC-52XS1E/RU/LC-65XS1E/RU

5 – 10

13.IC6702 (RH-iXC588WJN1Q)

This is a CPLD. By the SLOW BUS control, the extension I/O port for the reset signal and control signal sent to each device is created, and the

light control signal is generated.

light control signal is generated.

14.IC6804 (VHiAK7770EQ-1Q)

This is an audio DSP, which implements the audio delay processing for the delay of the pictures of IC6201, the analog 2.1ch processing and the

SRS TruSurroundXT processing according to the I2S signal input from IC7103.

SRS TruSurroundXT processing according to the I2S signal input from IC7103.

AUDIO-DSP

7

R/B#

I

READY BUSY

The Ready/Busy output is an Open Drain pin that signals the state of the memory.

The Ready/Busy output is an Open Drain pin that signals the state of the memory.

12, 37

VCC

-

SUPPLY VOLTAGE

The VCC supplies the power for all the operations (Read, Write, Erase).

The VCC supplies the power for all the operations (Read, Write, Erase).

13,36

VSS

-

GROUND

1-6, 10-11, 14-15,

20-28, 33-35, 39-

40,45-48

NC

-

NO CONNECTION

Pin No.

Pin Name

I/O

Pin Function

1

FRIR1

I

Rch feedback resistance input pin for ADC1

2

FRIL1

I

Lch feedback resistance input pin for ADC1

3

FROL1

O

Lch feedback resistance input pin for ADC1

4

LFLT

-

C connecting pin for PLL (10

µF)

5

AVDD

-

Analog part power supply pin 3.3V

6

VSS1

-

Analog part ground pin 0V

7

TESTI

I

Test pin (with pull down resistance)

8

CKM[0]

I

Clock mode select pin

9

HMUTEN

I

Headphone amplifier mute pin

10

INITRSTN

I

Initial reset pin (for initialization)

11

SETROM

I

The pin for ROM boot

12

DVDD18

-

Digital part power supply pin 1.8V

13

VSS3

-

Digital part grand pin 0V

14

DVDD18

-

Digital part power supply pin 3.3V

15

LRCLKO

O

LR channel selection output pin

16

CLKO

O

Clock output pin

17

BITCLKO

O

Serial bit clock output pin

18

SDOUT1

O

Serial-data output 1 pin

19

SDOUT2

O

Serial-data output 2 pin

20

SDOUT3

O

Serial-data output 3 pin

21

XTO

O

Oscillating circuit output pin

22

XTI

I

Oscillating circuit input pin

23

DVDD

-

Digital part power supply pin 3.3V

24

VSS3

-

Digital part ground pin 0V

25

DVDD18

-

Digital part power supply pin 1.8V

26

LRCLK1

I

LR channel selection input pin

27

CLK1

I

Serial master clock 1 pin

28

BITCLK1

I

Serial bit clock 1 pin

29

SDIN1

I

Serial-data input 1 pin

30

LRCLK2

I

LR channel selection input 2 pin

31

CLK2

I

Serial master clock 2 pin

32

BITCLK2

I

Serial bit clock 2 pin

33

SDIN2

I

Serial-data input 2 pin

34

CAD1

I

I2 C-bus address 1 pin

35

CAD0

I

I2 C-bus address 0 pin

36

SCL

I

SCL I2C Clock pin

37

DVDD

-

Digital part power supply pin 3.3V

38

VSS3

-

Digital part ground pin 0V

39

DVDD18

-

Digital part power supply pin 1.8V

40

SDA

I/O

SDA I2C Bus interface

41

HPEN

O

The pin for headphone detection

42

STO

O

Status output pin

43

TX

O

S/PDIF Transmitter output pin

44

DVDD

-

Digital part power supply pin 3.3V

Pin No.

Pin Name

I/O

Pin Function

LC-52XS1E/RU/LC-65XS1E/RU

5 – 11

15.IC6902 (VHiADAU1592-1Y)

This is a 1-bit amplifier. The sampling frequency is 12.288MHz. The 52” and 65” models are driven with 7.5W + 7.5W.

1bit-A-POWERAMP

45

VSS3

-

Digital part ground pin 0V

46

DVDD18

-

Digital part power supply pin 1.8V

47

SDIN3

I

Serial-data input 3 pin

48

BITCLK3

I

Serial bit clock 3 pin

49

CLK3

I

Serial master clock 3 pin

50

LRCLK3

I

LR channel selection input 3 pin

51

CKM[1]

I

Clock mode select pin

52

I2CSEL

I

I2CBUS selection pin

53

HDT

I

The pin for headphone detection

54

HPR

O

Headphone Rch output pin

55

HVDD

-

Headphone part power supply pin 3.3V

56

HVCOM

O

Headphone part common voltage output pin

57

VSS2

-

Headphone part ground pin 0V

58

HPL

O

Headphone Lch output pin

59

AOUTR2

O

DAC2 Rch output pin

60

AOUTL2

O

DAC2 Lch output pin

61

AOUTR1

O

DAC1 Rch output pin

62

AOUTL1

O

DAC1 Lch output pin

63

VSS1

-

Analog part ground pin 0V

64

AVDD

-

Analog part power supply pin 3.3V

65

FRIR2

I

ADC2 Rch feedback resistance input pin

66

FROR2

O

ADC2 Rch feedback resistance output pin

67

FROL2

O

ADC2 Lch feedback resistance output pin

68

FRIL2

I

ADC2 Lch feedback resistance input pin

69

AINR1

I

ADC Rch Single end input 1 pin

70

AINL1

I

ADC Lch Single end input 1 pin

71

AINR2

I

ADC Rch Single end input 2 pin

72

AINL2

I

ADC Lch Single end input 2 pin

73

AINR3

I

ADC Rch Single end input 3 pin

74

AINL3

I

ADC Lch Single end input 3 pin

75

AINR4

I

ADC Rch Single end input 4 pin

76

AINL4

I

ADC Lch Single end input 4 pin

77

VSS1

-

Analog part power supply pin 0.0V

78

VCOM

O

Analog part common voltage output pin

79

AVDD

-

Analog part power supply pin 3.3V

80

FROR1

O

Rch feedback resistance output pin for ADC1

Pin No.

Pin Name

I/O

Pin Function

1, 2, 3

OUTL-

O

Output of High Power Transistors, Left Channel Negative Polarity.

4, 5, 6

OUTL+

O

Output of High Power Transistors, Left Channel Positive Polarity.

7

TEST1

I

Reserved for Internal Use. Connect to DGND.

8

TEST0

I

Reserved for Internal Use. Connect to DGND.

9

ERR#

O

Error Indicator (Active Low, Open-Drain Output).

10

OTW#

O

Over temperature Warning Indicator (Active Low, Open-Drain Output).

11

MO/ST#

I

Mono/Stereo Mode Setting Pin for Stereo. Connect to DGND (for mono mode, connect to DVDD).

12

TEST3

I

Reserved for Internal Use. Connect to DVDD.

13

PGA1

I

Programmable Gain Amplifier Select, MSB.

14

PGA0

I

Programmable Gain Amplifier Select, LSB.

15

MUTE#

I

Mute (Active Low Input).

16

STDN#

I

Shutdown/Reset Input (Active Low Input).

17

XTI

I

Quartz Crystal Connection/External Clock Input.

18

XTO

O

Quartz Crystal Connection/Clock Output.

19

DGND

-

Digital Ground for Digital Circuitry. Internally connected to exposed pad (ePAD).

20

DVDD

-

Positive Supply for Digital Circuitry.

21

AVDD

-

Positive Supply for Analog Circuitry. (Can be tied to DVDD.)

22

AGND

-

Analog Ground for Analog Circuitry.

23

VREF

I

AVDD/2 Voltage Reference Connection for External Filter.

24

SLC_TH

I

Slicer Threshold Adjust. (Connect to AGND via a resistor for slicer operation.)

25

TEST8

I

Reserved for Internal Use. Connect to DGND.

26

TEST9

I

Reserved for Internal Use. Connect to DGND.

Pin No.

Pin Name

I/O

Pin Function

LC-52XS1E/RU/LC-65XS1E/RU

5 – 12

16.IC6951 (VHiYDA147SZ-1Y)

This is a digital amplifier. The 52” and 65” models are driven with 15W.

AUDIO POWER AMPLIFIER

17.IC7103 (RH-iXC582WJQZQ)

This is an FPGA, which receives the 10-bit LVDS signal from IC6201, implements the color gamut conversion and skin color correction, and out-

puts via the 10-bit RGBs of LVTTL. Also, while the I2S signal is input from IC6102, it implements the audio delay processing for the delay of the

pictures generated on the LCD TCON+A3C and subsequent PWBs.

puts via the 10-bit RGBs of LVTTL. Also, while the I2S signal is input from IC6102, it implements the audio delay processing for the delay of the

pictures generated on the LCD TCON+A3C and subsequent PWBs.

18.IC7502 (VHiTLVD1023-1Q)

This is an LVDS Tx, which converts the 10-bit RGBs of LVTTL from IC7103 into the LVDS signals.

LVDS Transmitter.

27

AINL

I

Analog Input Left Channel.

28

AINR

I

Analog Input Right Channel.

29

TEST12

I

Reserved for Internal Use. Connect to DGND.

30

TEST13

I

Reserved for Internal Use. Connect to DGND.

31, 32, 33

OUTR+

O

Output of High Power Transistors, Right Channel Positive Polarity.

34, 35, 36

OUTR-

O

Output of High Power Transistors, Right Channel Negative Polarity.

37, 38, 47,

48

PGND

-

Power Ground for High Power Transistors. Internally connected to exposed pad (ePAD).

39, 40, 41,

42, 43, 44,

42, 43, 44,

45, 46

PVDD

-

Positive Power Supply for High Power Transistors.

Pin No.

Pin Name

I/O

Pin Function

1, 2, 12, 25,

35, 36

NC

-

No Connection

3

PVDDREG

-

The power supply terminal for regulators (PVDD).

4

AVDD

-

The output terminal for 3.3V regulators

5

INLP

I

Analog input terminal (Lch+)

6

INLM

I

Analog input terminal (Lch-)

7

VREF

-

VREF Terminal

8

INRM

I

Analog input terminal (Rch-)

9

INRP

I

Analog input terminal (Rch+)

10

AVSS

-

Analog ground terminal

11

PLIMIT

I

Power limit setting terminal

13, 14

PVDDPR

-

The power supply terminal for a digital amplifier output (Rch+)

15, 16, 17

OUTPR

O

Digital amplifier output terminal (Rch+)

18, 19

PVSSR

-

The ground terminal for a digital amplifier output (Rch)

20, 21, 22

OUTMR

O

Digital amplifier output terminal (Rch-)

23, 24

PVDDMR

-

The power supply terminal for a digital amplifier output (Rch-)

26

SLEEPN

I

Sleep control terminal

27

PROTN

O

Error flag output terminal

28

MUTEN

I

Mute control terminal

29

CKOUT

O

The clock output terminal for a synchronization

30

CKIN

I

External clock input terminal

31

NCDRC0

I

Non clip / DRC1/DRC2 mode-select terminal 0

32

NCDRC1

I

Non clip / DRC1/DRC2 mode-select terminal 1

33

GAIN0

I

GAIN setting terminal 0

34

GAIN1

I

GAIN setting terminal 1

37, 38

PVDDML

-

The power supply terminal for a digital amplifier output (Lch-)

39, 40, 41

OUTML

O

Digital amplifier output terminal (Lch-)

42, 43

PVSSL

-

The ground terminal for a digital amplifier output (Lch)

44, 45, 46

OUTPL

O

Digital amplifier output terminal (Lch+)

47, 48

PVDDPL

-

The power supply terminal for a digital amplifier output (Lch+)

Pin No.

Pin Name

I/O

Pin Function

Click on the first or last page to see other LC-65XS1E (serv.man5) service manuals if exist.