Sharp LC-65XS1E (serv.man5) Service Manual ▷ View online

LC-52XS1E/RU/LC-65XS1E/RU

5 – 5

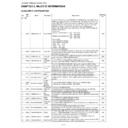

4. IC6052 (VHiTLVD1023-1Q)

This is an LVDS Tx, which converts the 8-bit RGBs of LVTTL sent from IC6102 into LVDS signals.

LVDS Transmitter.

93

DGND

---

Audio clock regeneration PLL analog ground.

96

XTALVCC

---

Audio clock regeneration PLL crystal oscillator power. 3.3V

97

REGVCC

---

Audio clock regeneration PLL crystal regulator power. 3.3V

Pin No.

Pin Name

I/O

Pin Function

70, 71

TA1+, TA1-

O

The 1st Link.

The 1st pixel output data when Dual-Link.

The 1st pixel output data when Dual-Link.

68, 69

TB1+, TB1-

64, 65

TC1+, TC1-

58, 59

TD1+, TD1-

56, 57

TE1+, TE1-

62, 63

TCLK1+, TCLK1-

O

LVDS Clock Out for 1st and 2nd Link.

52, 53

TA2+, TA2-

O

The 2nd Link.

These pins are disabled when Single Link.

These pins are disabled when Single Link.

50, 51

TB2+, TB2-

46, 47

TC2+, TC2-

40, 41

TD2+, TD2-

38, 39

TE2+, TE2-

44, 45

TCLK2+, TCLK2-

O

Additional LVDS Clock Out. Identical to TCLK1+,-. No connect if not used.

87 - 84,

81 - 76

R19 ~R10

I

The 1st Pixel Data Inputs.

R1 [9 : 0]

R1 [9 : 0]

99 - 95,

92 - 88

G19 ~G10

G1 [9 :0]

112 -110,

108 -106,

103 - 100

103 - 100

B19 ~B10

B1 [9 :0]

124 - 115

R29 ~R20

I

The 2nd Pixel Data Inputs.

R2 [9 : 0]

R2 [9 : 0]

136 - 127

G29 ~G20

G2 [9 : 0]

6, 5, 2, 1,

144 - 139

144 - 139

B29 ~B20

B2 [9 : 0]

17, 18

CONT11,CONT12

I

CONTROL Data Inputs.

19, 20

CONT21,CONT22

9

DE

I

Data Enable Input.

8

VSYNC

I

Vsync Input.

7

HSYNC

I

Hsync Input.

15

CLKIN

I

Clock Input.

21

R/F

I

Input Clock Triggering Edge Select.

H: Rising edge, L: Falling edge

H: Rising edge, L: Falling edge

22

RS

I

The use of these multi-function depends on input voltage of RS pin.

24

MAP

I

LVDS mapping table select.

H: Mapping Mode1

L: Mapping Mode2

H: Mapping Mode1

L: Mapping Mode2

Pin No.

Pin Name

I/O

Pin Function

Input voltage

of RS pin

of RS pin

VCC

0.6~1.4V

GND

LVDS output

Swing Control

Swing Control

Normal Swing

VOD=350mV(typ)

VOD=350mV(typ)

Reduced Swing

VOD=200mV(typ)

VOD=200mV(typ)

TTL/CMOS Input

VIH/VIL Control for

Small Swing Input

VIH/VIL Control for

Small Swing Input

VIH/VIL is fixed

Support Small Swing Input

VIH/VIL depends on

input voltage of RS pin

See VIH/VIL Spec

VIH/VIL depends on

input voltage of RS pin

See VIH/VIL Spec

VIH/VIL is fixed

LC-52XS1E/RU/LC-65XS1E/RU

5 – 6

5. IC6201 (RH-iXC068WJQZQ)

This is a main CPU. The output from the STB is 1080p. However, if the 480p and 1080i signals are directly connected to the display, this IC con-

verts the 480p and 1080i signals into 1080p signals.

verts the 480p and 1080i signals into 1080p signals.

Also, the OSD of the display is created here and added to the picture signals.

As the wall picture function, reading and processing operations of the data from the USB terminal are implemented here.

6. IC6301 (RH-iXB800WJQZY)

This is a clock generator, which generates 48MHz for SCC, 54MHz for STC and 74.25MHz for PWM from the crystal oscillator of 27MHz.

CLOCK-GENERATOR

25, 26

MODE1, MODE0

I

Pixel Data Mode.

27

MODE2

I

Distribution, DDR function enable.

The use of these multi-function depends on the setting of MODE<1:0>.

MODE<1:0>=HH(Single-in/Single-out Mode)

H: Distribution function enable.

L: Distribution function disable.

MODE<1:0>=HL(Single-in/Single-out Mode)

H: DDR (Double Edge input) function enable.

L: DDR (Double Edge input) function disable.

The use of these multi-function depends on the setting of MODE<1:0>.

MODE<1:0>=HH(Single-in/Single-out Mode)

H: Distribution function enable.

L: Distribution function disable.

MODE<1:0>=HL(Single-in/Single-out Mode)

H: DDR (Double Edge input) function enable.

L: DDR (Double Edge input) function disable.

30

/PDWN

I

H: Normal operation,

L: Power down (all outputs are Hi-Z)

L: Power down (all outputs are Hi-Z)

31

PRBS

I

PRBS generator is active when MODE <1:0> = LL (Dual-in/Dual-out mode)

H: PRBS generator is enable. Pattern is PRBS-23.

L: Normal Operation

H: PRBS generator is enable. Pattern is PRBS-23.

L: Normal Operation

10, 11, 12, 16,

28, 32

Reserved

I

Must be tied to GND.

23

Reserved

I

Must be Open.

29, 33, 109

N/C

Must be Open.

3, 13, 82, 93,

104, 113, 125,

137

VCC

-

Power Supply Pins for TTL inputs, output and digital circuitry.

4, 14, 83, 94,

105, 114, 126,

138

GND

-

Ground Pins for TTL inputs, outputs and digital circuitry.

43, 49, 55, 61,

67

LVCC

-

Power Supply Pins for LVDS Outputs.

37, 42, 48, 54,

60, 66, 72

LGND

-

Ground Pins for LVDS Outputs.

35, 74

PVCC

-

Power Supply for PLL circuitry.

34, 36, 73, 75

PGND

-

Ground Pin for PLL circuitry.

Pin No.

Pin Name

I/O

Pin Function

1

XI

I

Crystal connection. Connect to a 27MHz fundamental mode pullable crystal.

2, 6, 13

GND

-

Connect to ground.

3, 5, 10, 14,

15

VDD

-

Connect to +3.3V.

4

VIN

I

VCXO Voltage Input. Zero to 3.3v analog control voltage for VCXO.

7

54M

O

54MHz reference clock output.

8

NC

-

No connect. Do not connect this pin to anything.

9

74.175824M

O

74.175824 MHz clock output.

11

83.57M

O

83.57MHz clock output.

12

48.000M

O

48.000MHz clock output.

16

X2

I

Crystal connection. Connect to a 27MHz fundamental mode pullable crystal.

Pin No.

Pin Name

I/O

Pin Function

MODE 1

MODE 2

MODE

L

L

H

L

L

H

H

H

Dual Link (Dual-in/Dual-out)

Dual Link (Single-in/Dual-out)

Single Link (Dual-in/Single-out)

Single Link (Single-in/Single-out)

LC-52XS1E/RU/LC-65XS1E/RU

5 – 7

7. IC6302 (RH-iXB801WJQZY)

This is a clock generator, which generates 54MHz for STC, 33MHz for CPLD, 33MHz for FPGA and 33MHz for PCI from the crystal oscillator of

27MHz.

27MHz.

CLOCK-GENERATOR

8. IC6402~6405 (RH-iXC511WJQZQ)

This is a 512Mb DDR2 SDRAM, which operates as the memory for IC6201.

512Mb DDR SDRAM

Pin No.

Pin Name

I/O

Pin Function

1

XI

I

Crystal connection. Connect to a 27MHz fundamental mode pullable crystal.

2, 6, 13

GND

-

Connect to ground.

3, 5, 10, 14,

15

VDD

-

Connect to +3.3V.

4

VIN

I

VCXO Voltage Input. Zero to 3.3v analog control voltage for VCXO.

7

54M

O

54.000MHz reference clock output.

8, 9, 11, 12

33M

O

33.000MHz clock output.

16

X2

I

Crystal connection. Connect to a 27MHz fundamental mode pullable crystal.

Pin No.

Pin Name

I/O

Pin Function

J8, K8

CK, CK

I

Clock : CK and CK are differential clock inputs.

All address and control input signals are sampled on the crossing of the positive edge of CK and neg-

ative edge of CK.

Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).

All address and control input signals are sampled on the crossing of the positive edge of CK and neg-

ative edge of CK.

Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).

K2

CKE

I

Clock Enable : CKE HIGH activates, and CKE LOW deactivates internal clock signals,

and device input buffers and output drivers.

Taking CKE Low provides PRECHARGE POWER DOWN and SELF REFRESH

operation (all bank idle), or ACTIVE POWER DOWN (row ACTIVE in any bank).

CKE is synchronous for POWER-DOWN entry and exit, and for SELF REFRESH entry.

CKE is asynchronous for SELF REFRESH exit.

After VREF has become stable during the power on and initialization sequence, it must be maintained

for proper operation of the CKE receiver. For proper self-refresh entry and exit, VREF must be main-

tained to this input.

CKE must be maintained high throughput READ and WRITE accesses.

Input buffers, excluding CK, CK and CKE are disabled during POWER-DOWN.

Input buffers, excluding CKE are disabled during SELF REFRESH.

and device input buffers and output drivers.

Taking CKE Low provides PRECHARGE POWER DOWN and SELF REFRESH

operation (all bank idle), or ACTIVE POWER DOWN (row ACTIVE in any bank).

CKE is synchronous for POWER-DOWN entry and exit, and for SELF REFRESH entry.

CKE is asynchronous for SELF REFRESH exit.

After VREF has become stable during the power on and initialization sequence, it must be maintained

for proper operation of the CKE receiver. For proper self-refresh entry and exit, VREF must be main-

tained to this input.

CKE must be maintained high throughput READ and WRITE accesses.

Input buffers, excluding CK, CK and CKE are disabled during POWER-DOWN.

Input buffers, excluding CKE are disabled during SELF REFRESH.

L8

CS

I

Chip Select : All commands are masked when CS is registered HIGH.

CS provides for external bank selection on systems with multiple banks.

CS is considered part of the command code.

CS provides for external bank selection on systems with multiple banks.

CS is considered part of the command code.

K9

ODT

I

On Die Termination Control : ODT (registered HIGH) enables on die termination resistance internal to

the DDR2 SDRAM.

For x16 configuration ODT is applied to each DQ, UDQS/UDQS. LDQS/LDQS, UDM and

LDM signal.

The ODT pin will be ignored if the Extended Mode Register(EMRS(1)) is

programmed to disable ODT.

the DDR2 SDRAM.

For x16 configuration ODT is applied to each DQ, UDQS/UDQS. LDQS/LDQS, UDM and

LDM signal.

The ODT pin will be ignored if the Extended Mode Register(EMRS(1)) is

programmed to disable ODT.

K7, L7, K3

RAS, CAS, WE

I

Command Inputs : RAS, CAS and WE (along with CS) define the command being

entered.

entered.

F3, B3

DM

(LDM,UDM)

I

Input Data Mask : DM is an input mask signal for write data.

Input data is masked when DM is sampled HIGH coincident along with that input data during a

WRITE access.

DM is sampled on both edges of DQS.

Although DM pins are input only, the DM loading matches the DQ and DQS loading.

Input data is masked when DM is sampled HIGH coincident along with that input data during a

WRITE access.

DM is sampled on both edges of DQS.

Although DM pins are input only, the DM loading matches the DQ and DQS loading.

L2, L3

BA0, BA1

I

Bank Address Inputs : BA0 and BA1 define to which bank an ACTIVE, Read, Write

or PRECHARGE command is being applied.

Bank address also determines if the mode register

or extended mode register is to be accessed during a MRS or EMRS cycle.

or PRECHARGE command is being applied.

Bank address also determines if the mode register

or extended mode register is to be accessed during a MRS or EMRS cycle.

M8, M3, M7, N2,

N8, N3, N7, P2,

P8, P3, M2, P7,

P8, P3, M2, P7,

R2

A [0 : 12]

I

Address Inputs : Provide the row address for ACTIVE commands, and the column

address and AUTO PRECHARGE bit for READ/WRITE commands to select one

location out of the memory array in the respective bank.

A10 is sampled during a precharge command to determine whether the

PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH).

If only one bank is to be precharged, the bank is selected by BA0, BA1.

The address inputs also provide the op-code during a MODE REGISTER SET

command.

address and AUTO PRECHARGE bit for READ/WRITE commands to select one

location out of the memory array in the respective bank.

A10 is sampled during a precharge command to determine whether the

PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH).

If only one bank is to be precharged, the bank is selected by BA0, BA1.

The address inputs also provide the op-code during a MODE REGISTER SET

command.

G8, G2, H7, H3,

H1, H9, F1, F9,

C8, C2, D7, D3,

D1, D9, B1, B9

DQ[0:15]

I/O

Data Input/Output : Bi-directional data bus.

LC-52XS1E/RU/LC-65XS1E/RU

5 – 8

9. IC6351 (RH-iXC012WJQZQ)

This is an IC for IrSS encoding, which receives the signals from the IrSS light receiving section located on the RC/LED PWB, encode them and

transfer the data to IC6201 via the SLOW BUS.

transfer the data to IC6201 via the SLOW BUS.

Ir communication controller

B7, A8, F7, E8

UDQS, UDQS

LDQS, LDQS

I/O

Data Strobe : Output with read data, input with write data.

Edge-aligned with read data, centered in write data.

For the x16, LDQS corresponds to the data on DQ0~DQ7 ; UDQS corresponds to

the data on DQ8~DQ15

The data strobes DQS, LDQS and UDQS may be used in single ended mode or paired with optional

complementary signals DQS, LDQS and UDQS to provide differential pair signaling to the system dur-

ing both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe

signals.

Edge-aligned with read data, centered in write data.

For the x16, LDQS corresponds to the data on DQ0~DQ7 ; UDQS corresponds to

the data on DQ8~DQ15

The data strobes DQS, LDQS and UDQS may be used in single ended mode or paired with optional

complementary signals DQS, LDQS and UDQS to provide differential pair signaling to the system dur-

ing both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe

signals.

A2, E2, L1, R3,

R7, R8

NC

-

No Connect : No internal electrical connection is present.

A9, C1, C3, C7,

C9, E9, G1, G3,

G7, G9

VDDQ

-

DQ Power Supply : +1.8V

±0.1V.

A7, B2, B8, D2,

D8, E7, F2, F8,

H2, H8

VSSQ

-

DQ Ground.

J1

VDDL

-

DLL Power Supply : +1.8V

± 0.1V.

J7

VSSDL

-

DLL Ground.

A1, E1, J9, M9,

R1

VDD

-

Power Supply : +1.8V

±0.1V.

A3, E3, J3, N1,

P9

VSS

-

Ground.

J2

VREF

I

Reference voltage for inputs for SSTL interface.

Pin No.

Pin Name

I/O

Pin Function

Remarks

J8

CI

I

Oscillation buffer input

Duty 40-60%

J9

CO

O

Oscillation buffer output

H7,J7

CLKSEL[1:0]

I

Clock selection

00-16MHz 01-24MHz 10-32MHz 11-48MHz

00-16MHz 01-24MHz 10-32MHz 11-48MHz

A9

XRESET

I

Reset signal

Negative logic

H6, J6,

H5, J5,

H5, J5,

H4, J4, J3,

J2, J1, H1,

J2, J1, H1,

G1, F1,

E2, E1,

E2, E1,

D2, D1

D[15:0]

I/O

System Data Bus

C1, B1,

A1, A2,

A1, A2,

A3, B3

A[5:0]

I

System Address Bus

A5

XCS

I

System Chip Select

Negative logic

A6

XRD

I

System Read signal

Negative logic

A7

XWR

I

System Wright signal

Negative logic

A4

BYTE

I

System 8bit access

Positive logic

A8

INT

O

System Interrupt request signal

Logic is a register setup.

B5

DREQ

O

System DMA Transmission demand signal

Logic is a register setup.

B4

XDACK

I

System DMA Transmission bitter taste knowledge signal

Negative logic

E9

IRTXA

O

Front end Channel A transmission signal

Positive logic

D9

IRRXA

I

Front end Channel A received signal

Logic is a register setup.

G9

IRTXB

O

Front end Channel B transmission signal

Positive logic

F9

IRRXB

I

Front end Channel B received signal

Logic is a register setup.

F8

IRRX2

I

Front end Channel received signal

Logic is a register setup.

C9

IRRC

O

Front end Ir remote control signal

Positive logic

Pin No.

Pin Name

I/O

Pin Function

BYTE

A[0]

D[15:8]

D[7:0]

0

0

Effective

Effective

0

1

Effective

Invalid

1

0

Invalid

Effective

1

1

Effective

Invalid

Click on the first or last page to see other LC-65XS1E (serv.man5) service manuals if exist.