Panasonic WV-NM100 Service Manual ▷ View online

– 10 –

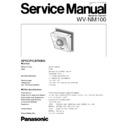

OVERALL BLOCK DIAGRAM

FLASH ROM

RTC

(16M-BIT)

SDRAM

(128M-BIT)

SDRAM

(128M-BIT)

LED

DRIVER

LED

DRIVER

SETTING

RESET

SWITCH

RESET

SWITCH

HTML

DOCUMENT

INITIALIZA-

TION

SWITCH

DOCUMENT

INITIALIZA-

TION

SWITCH

ETHERNET

CONTROLLER

FOR RTC (IC201)

POWER SUPPLY

POWER SUPPLY

EEPROM

FOR

POWER SUPPLY

POWER SUPPLY

SYSTEM RESET

MOTOR

DRIVER

VOLTAGE DET.

PAN/TILT

MECHANICAL

ASS'Y

(M1)

MECHANICAL

ASS'Y

(M1)

CAMERA

MODULE

ASS'Y

(EU1)

MODULE

ASS'Y

(EU1)

VOLTAGE DETECTOR

AC

ADAPTER

(PS1)

ADAPTER

(PS1)

LITHIUM

BATTERY

(BAT1)

BATTERY

(BAT1)

JK201

ETHERNET

CONNECTOR

(BUILT-IN

ACCESS LED,

LINK LED)

ETHERNET

CONNECTOR

(BUILT-IN

ACCESS LED,

LINK LED)

E1

ALARM

CONNECTOR

ALARM

CONNECTOR

JK1

POWER PLUG

CONNECTOR

POWER PLUG

CONNECTOR

PLD

DSP

TO CAMERA

TO BATTERY

TO PLD

TO POWER

TO PAN

TO TILT

TO RS232C

TO JTAG

POWER

LED

LED

E

D

F

YUV7

1

2

8

7

6

5

4

3

1

2

4

3

1

2

TXD2

RXD2

1

4

7

MR

SW106

RESET

5

R2

P1

N5

RESET

SDR_CS0

SDR_WE

SDR_CAS

SDR_RAS

SDR_CLK

SDR_CKE

SDR_DQMLH

SDR_DQMLL

SDR_DQMHL

SDR_DQMHH

SDR_CS0

SDR_WE

SDR_CAS

SDR_RAS

SDR_CLK

(75MHz)

SDR_CKE

SDR_DQMLH

SDR_DQMLL

SDR_DQMHL

SDR_DQMHH

P15

R17

T19

T18

C15

N14

N15

P19

P17

R19

GIO2/

INT2

INT2

GIO0/

INT0

INT0

2

WDTN

IC107

IC104

SW103

RESET3307N

1

2

3

7

5

14

FILTER

CN101

CN104

CN402

CN401

V3D

13

9,11

TMS

TRSTN

TDI

TDO

V3D

EMU1

EMU0

TCK

22

18

16

14

15

9,10

12,13

11

17

19

20

25

21

CN500

YUV6

YUV5

YUV4

YUV3

YUV2

YUV1

YUV0

YUV7

RESETN

YUV6

YUV5

YUV4

YUV3

YUV2

YUV1

YUV0

R12

IC102

W13

V13

U13

P13

W14

V14

R13

YIN7

ARM_A0-20

ARM_D0-15

EM_CS0

EM_CS3

EM_CS1

EM_CS4

A12

C11

A11

E11

A10

F10

J5

M6

N3

M5

K5

L5

A13

L3

L6

EM_WEN

EM_OEN

FLS_RYBY

INT7N_RTC

INT4N_ETHER

INT6N_ALM

ARMCK_O (37.5MHz)

RST_ETHER

ETHER_RDYN

ALM_O

AUX_O

EM_CS0N

EM_CS3N

EM_CS1N

EM_CS4N

EM_WE

EM_OE

GIO20

GIO7/INT7

GIO4/INT4

GIO6/INT6

GIO16/CLKOUT1

GIO10/DSP_BDR2

GIO12/DSP_BLCKX2

GIO11/DSP_BFSX2

SDR_A0-14

K14,K15,K18

K19,L14,L15,

L17,L18,L19,

M19,M17,M15,

N18,N17,M14,

K19,L14,L15,

L17,L18,L19,

M19,M17,M15,

N18,N17,M14,

SDR_A0-14

SDR_DQ0-15,

SDR_DQ16-31/

ARM_D16-31

SDR_DQ0-31

A0-11,NC1,

BA0,1

BA0,1

19

16

17

18

38

37

39

15

CS

WE

CAS

RAS

CLK

CKE

UDQM

LDQM

DQ0-15

A0-11,NC1,

BA0,1

BA0,1

DQ0-15

IC105

23-26,

29-34,

22,35,36,

20,21

29-34,

22,35,36,

20,21

2,4,5,7,

8,10,11,13,

42,44,45,47,

48,50,51,53

8,10,11,13,

42,44,45,47,

48,50,51,53

SDR_A0-14

SDR_DQ0-15

SDR_DQ16-31

SDR_A0-14

A16,B16,A17,B17,

C17,A18,B18,B19,

C18,D17,C19,D18,

D19,E17,F15,E18,

E19,F17,G15,F19,

G14,G17,G18,G19,

H14,H17,H18,H19,

J15,J14,J17,J18

C17,A18,B18,B19,

C18,D17,C19,D18,

D19,E17,F15,E18,

E19,F17,G15,F19,

G14,G17,G18,G19,

H14,H17,H18,H19,

J15,J14,J17,J18

EM_WAIT

H6,F1,G5,F2,

F3,E1,E2,G6

F5,D1,D2,C2,

D3,B1,B2,C3

F3,E1,E2,G6

F5,D1,D2,C2,

D3,B1,B2,C3

EA0-20

25-18,

8-1,48,

17,16,9

8-1,48,

17,16,9

29,31,33,35,

38,40,42,44,

30,32,34,36,

39,41,43,45

38,40,42,44,

30,32,34,36,

39,41,43,45

EA0-19

CE

WE

OE

RY

/B

Y

RESET

RESETN

ED0-15

EA0-3

ED0-3

RESETN

EA0-15

A0-19

26

11

28

15

12

1

11

9

16

18

X201

(32.768KHz)

19

3

IC204

IC201

IC202

DQ0-14,

DQ15/A1

DQ15/A1

A0-3

D0-3

CE

5-8

12-15

DATA BUS

RESETN

38

35

V3D

FILTER

CN204

JK201

SW203

SW204

(Bit 1) : Fix to pin 6 side.

V3D

Q209

D214

Q210

Q211

L209

L208

LINE

FILTER

FILTER

L12

LINE

FILTER

FILTER

LINE

FILTER

FILTER

1

RESET3307N

EA0-2,19

23-20

34-31

ED0-4

EM_CS1N

EM_WEN

EM_OEN

INT4N_ETHER

INT6N_ALM

ARMCK_O

RST_ETHER

E_RESET

ALM_I

2

43

42

3

47

18

41

46

40

39

25

11

2

3

5

7

1

10

11

CN201

E1

1

3

A1

B1

B1

A2

B2

B2

A3

B3

B3

1

2

7

3

8

ACCESS LED_GREEN

LINK LED_YELLOW

TD+

TD-

CT

RD+

BAT+

BAT-

ALARM IN

ALARM OUT

AUX OUT

RD-

TDO

TMS

TDI

TCK

VCC

7

8

4

5

6

1

2

3

9

10

45

44

4

B12

TDO

TDI

TMS

TCK

A8

A9

A10

A11

A11

A1

A7

A0/GOE0

ETHER_LED

ETHER_IRQ

B13

B3-0

A5

CLK0/I

CLK3/I

A6

A3

CLK1/I

B15/GOE1

A2

B14

RESET

IRO/IRQ

I_ACT

I_LINK

TPOP

TPON

ZVREG

TPIP

TPIN

EECS

EECK

EEDI

EEDO

LCLK/

XTALIN

XTALIN

XTALOUT

(25MHz)

(25MHz)

V5D

Q204,D204,205

VBAT

ALARM INPUT

CN105

E2

3

2

1

5,6

7,8

ALARM OUTPUT

AUX OUTPUT

FILTER

+5V REG.

IC1,Q4,D5

IC2,Q2,D6

+3.3V REG.

R1

2A

JK1

FILTER

ALM_I

ALM_I

ALM_O

ALM_O

AUX_O

AUX_O

V5A

V5A

V3A

V3A

Q1,D2

Q5,D3

Q6,D4

FILTER

V5D

V3D

VOUT

VIN

VOUT

VIN

VOUT

VIN

4

4

4

6

6

6

IC304

IC305

IC306

V3A

V18D

BATTERY

CONTROLLER

CONTROLLER

IC208

SA[0-9]

EA0-9

ED0-15

EM_CS4N

EM_WEN

EM_OEN

ETHER_RDYN

128

18

19

2

SD[0-15]

CS

R/W/IOWR

NC3/IORD

DTACK/RDY

3

16

62

60

88

87

70

92

71

51

50

49

48

3

CS

SK

DI

DO

X202

(25MHz)

IC209

4

5

6

79

80

4-12,

15

15

42,41,

39-35,

33-29,

26-23

39-35,

33-29,

26-23

B11-8

ADDRESS BUS

SDRAM DATA BUS

SDRAM ADDRESS BUS

2

B3,C4,A3,

B4,A4,C5,

E6,B5,A5,

C6,E7,B6,

A6,F7,C7,

B7,F8,C8,

B8,A8,E9,

B4,A4,C5,

E6,B5,A5,

C6,E7,B6,

A6,F7,C7,

B7,F8,C8,

B8,A8,E9,

YIN6

YIN5

YIN4

YIN3

YIN2

YIN1

YIN0

HD

VD

PCLK

DSTOP

HD

VD

PCLK

DSTOP

HDIN

VDIN

CLK135

GIO14/

DSP_XF

DSP_XF

GIO8/

DSP_BFSR2

DSP_BFSR2

GIO13/

DSP_BDX2

DSP_BDX2

GIO9/

DSP_BCLKR2

DSP_BCLKR2

GIO5/

INT5

INT5

P10

W11

P14

L1

RESET

RESETN

I2C SERIAL

DATA

DRIVER

DATA

DRIVER

Q212

IC501

IC108

IC402

SCL

SDA

SCL

SDA

4

5

3

4

4

2

4

2

K2

4

2

2

1

I2CSCL

I2CSDA_O

I2CSDA_I

M2

L2

M1

N1

T17

V19

MXI

MXO

VDN

FCLK

FCLK

X500

V3A

RESETN

VD

(12.2727MHz)

X104

(24.576MHz)

X401

(4MHz)

VRESET

PWDN

DVDD

PVDD

AVDD

A1

A2

B1

B2

A1

A2

B1

B2

A1

A2

B1

B2

C1

C2

D1

D2

OSCIN

SCLK

SDATA

RESET

VD

LATCH

1

2

4

3

C1

C2

D1

D2

C1

C2

D1

D2

24

38

26

28

32

30

33

34

R6

SDO1

IC101

IC401

LATCH

35

SCLK1

U5

GIO18/

SDEN1

SDEN1

SDO1

SCLK1

TXD2

RXD2

TMS

TRST

TDI

TDO

TCK

EMU0

EMU1

U6

W3

C14

B14

B15

E14

A15

P3

R1

16

14

12

10

36

VRESET

PWDN

DVDD

PVDD

AVDD

19

16

17

18

38

37

39

15

CS

WE

CAS

RAS

CLK

CKE

UDQM

LDQM

RESET3307N

AUX_O

ALM_O

ALM_I

IC106

23-26,

29-34,

22,35,36,

20,21

29-34,

22,35,36,

20,21

2,4,5,7,

8,10,11,13,

42,44,45,47,

48,50,51,53

8,10,11,13,

42,44,45,47,

48,50,51,53

CS

WR

RD

INTR

OSCIN

(32.768KHz)

OSCOUT

WDTN

TMOUT

SW201

(Bit 2) : Fix to pin 3 side.

POWER BOARD

MAIN BOARD

– 11 –

SCHEMATIC DIAGRAM OF MAIN BOARD (1/4)

TO CAMERA

TO RS232C

TO JTAG

TO

CAMERA

MODULE

ASS'Y

(EU1)

CAMERA

MODULE

ASS'Y

(EU1)

I2C SERIAL DATA

DRIVER

DSP

TO

PAGE 12

PAGE 12

YUV7

YUV6

YUV5

YUV4

YUV3

YUV2

YUV1

YUV0

I2CSCL

DGND

RESETN

DSTOP

VD

HD

R121

1K

R120

5.6K

L501

R509

0

DGND

DGND

R505

2K

V28A

CN500

1

YUV7

2

YUV6

3

YUV5

4

YUV4

5

YUV3

6

YUV2

7

YUV1

8

YUV0

9

DVDD

10

DVDD

11

PVDD

12

AVDD

13

AVDD

14

VRESET

15

PWDN

16

FCLK

17

SCL

18

SDA

19

RESET

20

DSTOP

21

VD

22

HD

23

DGND

24

DGND

25

PCLK

26

AGND

27

AGND

C504

10

R506

2K

CAGND

R508

100

V28D

V28D

V3D

C500

10

C509

0.1

C510

0.1

DGND

C502

0.1

R507

1M

CAGND

R503

4.7K

L502

L500

C514

0.1

V28D1

L503

R504

4.7K

C501

10

C506

0.1

IC501

1

NC

2

IN_A

3

GND

4

OUT_Y

5

VCC

C507

0.1

DGND

DGND

V28D1

R561

100

R560

100

R559

100

R558

100

R557

100

R556

100

R555

100

R554

100

R510

0

R511

0

R512

100

R514

0

R515

0

DGND

I2CSDA_O

I2CSDA_I

PCLK

Q212

1

2

3

4

5

C311

OPEN

C312

OPEN

DGND

C313

OPEN

DGND

C515

10P

C516

10P

X500

(12.2727MHz)

1

3

2

4

DGND

CN104

1

TXD2

2

RXD2

3

GND

EM_CS0N

EM_CS4N

EM_WEN

EM_OEN

EM_CS1N

EM_CS3N

V3D11

C110

4.7/16

4.7/16

4.7/16

4.7/16

L114

1

4

3

2

C116

DGND

V3D

L113

1

4

3

2

V18D

DGND

C109

+

-

+

-

+

-

+

-

C115

L108

RESETN

ETHER_RDYN

1

4

3

2

V3D

DGND

R111

10K

R108

10K

R112

10K

R113

10K

R114

10K

R109

10K

C112

0.1

C111

0.1

C118

0.01

C117

0.01

YUV7

YUV0

RESETN

ETHER_RDYN

SCLK1

MXO

MXI

TST0

TST1

TST2

TST3

TST4

SDO1

RESET3307N

INT2N

INT0N

INT4N_ETHER

VDN

VD

INT7N_RTC

INT6N_ALM

AUX_O

ALM_O

ARMCK_O

FLS_RYBY

SDR_A[14_0]

SDR_DQ[31_0]

SDR _CS0,WE,CAS,RAS,DQM[HH,HL,LH,LL],CKE,CLK

ED[15_0]

EA[20_0]

EM_CS[4,3,1,0]N,WEN,OEN

SDEN1N

RST_ETHER

YUV4

YUV1

MXO

YUV2

YUV6

VD

YUV5

YUV3

TRSTN

TDI

EM_ CS3N

TCK

TDO

TMS

EMU1

EMU0

TEST3

MXI

TEST4

TEST2

TEST1

TEST0

EM_ WEN

EM_ CS1N

EM_ CS4N

EM_ OEN

SDR_A0

SDR_A1

SDR_A2

SDR_A3

SDR_A4

DSTOP

I2CSDA_O

I2CSCL

HD

PCLK

I2CSDA_I

SDR_A5

SDR_A6

SDR_A7

SDR_A8

SDR_A9

SDR_A10

SDR_A11

SDR_A12

SDR_A13

SDR_A14

SDR_ CKE

SDR_ DQMLH

SDR_DQMHL

SDR_DQMLL

SDR_ DQMHH

SDR_ WE

SDR_ RAS

SDR_CAS

SDR_CLK

SDR_CS0

EM_ CS0N

EA2

EA4

EA8

EA12

EA19

SDR_DQ0

SDR_DQ2

SDR_DQ4

ED13

ED14

EA0

EA3

EA7

EA11

EA15

EA18

SDR_DQ1

SDR_DQ3

SDR_DQ5

SDR_DQ7

ED11

ED15

EA1

EA5

EA9

EA14

EA17

SDR_DQ6

SDR_DQ8

SDR_DQ10

ED9

ED10

ED12

SDR_DQ9

SDR_DQ11

SDR_DQ12

ED5

ED6

EA6

EA10

EA20

EA13

EA16

SDR_DQ15

SDR_DQ16

ED1

ED3

ED4

ED8

SDR_DQ14

SDR_DQ17

SDR_DQ19

SDR_DQ20

SDR_DQ18

SDR_DQ21

SDR_DQ22

SDR_DQ23

SDR_DQ24

SDR_DQ25

SDR_DQ26

SDR_DQ27

SDR_DQ29

SDR_DQ28

SDR_DQ13

SDR_DQ30

SDR_DQ31

ED2

ED7

ED0

DGND

DGND

V3D11

ETHER_RDYN

R137

47

R138

47

R144

47

R141

47

R136

10K

R316

10K

R132

R128

470

R129

470

R130

470

470

470

R313

0

R314

0

R125

470

R126

470

R118

10K

R119

OPEN

R124

47

R127

0

R143

100

R139 10K

R171

10K

R167

47

R160

47

R161

47

R159

47

R164

47

R157

47

R165

47

R166

47

R158

47

R154

47

R156

47

R150

47

R151

47

R155

47

R149

47

R152

47

R153

47

R147

47

R148

47

R312

0

R146

47

R168

470

R163

2K

R162

2K

C123

0.01

C119

0.01

C122

0.01

C121

0.01

C120

0.01

C133

0.01

C124

0.01

C126

0.01

C128

0.01

C129

0.01

C151

0.01

C147

0.01

C153

0.01

C168

0.01

C165

0.01

C166

0.01

C167

0.01

C164

0.01

C162

0.01

C139

0.01

C140

0.01

C145

0.01

C138

0.01

C125

0.01

C127

0.01

C130

0.01

C101 4.7/16

C103 4.7/16

+

-

+

-

C105

+

+

-

-

-

4.7/16

C104

4.7/16

R197

47

R198

47

R199

47

R200

47

R901

47

R907

47

R908

47

R909

47

R910

47

R911

47

R912

47

R919

47

R920

47

R921

47

R922

47

R923

47

R924

10

R928

33

R929

33

R930

33

R934

33

R935

33

R931

100

R933

100

R932

100

R926

100

R927

100

R917

33

R918

33

R915

100

R916

100

R913

100

R914

100

R905

33

R906

33

R903

100

R904

100

R902

100

R925

100

R968

10K

R936

47

R937

47

R938

47

R946

47

R947

47

R948

10

R939

100

R940

100

R941

100

R945

33

R944

33

R942

33

R943

33

R956

100

R954

100

R955

100

R963

100

R961

100

R962

100

R950

100

R949

100

R958

100

R957

100

R965

100

R964

100

R967

100

R966

100

R960

100

R951

100

R952

33

R953

33

R959

33

R970

10K

R315

R972

0

R131

10K

R975

10K

R974

10K

R973

0

R110

10K

R971

10K

R976

10K

R977

10K

IC102

A2

DGND8

A3

ARM_A2

A4

ARM_A4

A5

ARM_A8

A6

ARM_A12

A7

DGND7

A8

ARM_A19

A9

EM_BS

A10

EM_WE

A11

EM_CS1

A12

EM_CS0

A13

EM_WAIT

A14

PLLVDD1

A15

TCK

A16

SDR_DQ0

A17

SDR_DQ2

A18

SDR_DQ4

B1

ARM_D13

B2

ARM_D14

B3

ARM_A0

B4

ARM_A3

B5

ARM_A7

B6

ARM_A11

B7

ARM_A15

B8

ARM_A18

B9

CGND9

B10

EM_RNW

B11

EM_CS2

B12

CGND8

B13

M48XO

B14

TRST

B15

TDI

B16

SDR_DQ1

B17

SDR_DQ3

B18

SDR_DQ5

B19

SDR_DQ7

C1

CVDD1

C2

ARM_D11

C3

ARM_D15

C4

ARM_A1

C5

ARM_A5

C6

ARM_A9

C7

ARM_A14

C8

ARM_A17

C9

ARM_A22

C10

EM_BEL

C11

EM_CS3

C12

CVDD8

C13

M48XI

C14

TMS

C15

SDR_CLK

C16

DVDD8

C17

SDR_DQ6

C18

SDR_DQ8

C19

SDR_DQ10

D1

ARM_D9

D2

ARM_D10

D3

ARM_D12

D17

SDR_DQ9

D18

SDR_DQ11

D19

SDR_DQ12

E1

ARM_D5

E2

ARM_D6

E3

DVDD1

E5

NC

E6

ARM_A6

E7

ARM_A10

E8

CVDD9

E9

ARM_A20

E10

EM_BEH

E11

EM_CS4

E12

EM_WIDTH

E13

PLLGND1

E14

TDO

E17

SDR_DQ13

E18

SDR_DQ15

E19

SDR_DQ16/ARM_D16

F1

ARM_D1

F2

ARM_D3

F3

ARM_D4

F5

ARM_D8

F6

DVDD10

F7

ARM_A13

F8

ARM_A16

F9

ARM_A21

F10

EM_OE

F11

DVDD9

F12

CVDD11

F13

DGND6

F14

DGND5

F15

SDR_DQ14

F17

SDR_DQ17/ARM_D17

F18

DVDD7

F19

SDR_DQ19/ARM_D19

G1

DSP_BDR

G2

DSP_CLKS

G3

CGND1

G5

ARM_D2

G6

ARM_D7

G14

SDR_DQ20/ARM_D20

G15

SDR_DQ18/ARM_D18

G17

SDR_DQ21/ARM_D21

G18

SDR_DQ22/ARM_D22

G19

SDR_DQ23/ARM_D23

H1

DSP_BCLKR

H2

DSP_BFSX

H3

DSP_BCLKX

H5

CVDD2

H6

ARM_D0

H14

SDR_DQ24/ARM_D24

H15

CVDD7

H17

SDR_DQ25/ARM_D25

H18

SDR_DQ26/ARM_D26

H19

SDR_DQ27/ARM_D27

J1

DSP_BFSR

J2

DGND1

J3

DSP_BDX

J5

GIO20

J6

DVDD2

J14

SDR_DQ29/ARM_D29

J15

SDR_DQ28/ARM_D28

J17

SDR_DQ30/ARM_D30

J18

SDR_DQ31/ARM_D31

J19

CGND7

K1

GIO19/SDEN2

K2

GIO18/SDEN1

K3

GIO17/CLKOUT2

K5

GIO16/CLKOUT1

K6

GIO15/ATTACH

K14

SDR_A0

K15

SDR_A1

K17

DVDD6

K18

SDR_A2

K19

SDR_A3

L1

GIO14/DSP_XF

L2

GIO13/DSP_BDX2

L3

GIO12/DSP_BCLKX2

L5

GIO10/DSP_BDR2

L6

GIO11/DSP_BFSX2

L14

SDR_A4

L15

SDR_A5

L17

SDR_A6

L18

SDR_A7

L19

SDR_A8

M1

GIO9/DSP_BCLKR2

M2

GIO8/DSP_BFSR2

M3

CVDD3

M5

GIO6/INT6

M6

GIO7/INT7

M14

SDR_A14

M15

SDR_A11

M17

SDR_A10

M18

DGND4

M19

SDR_A9

N1

GIO5/INT5

N2

DVDD3

N3

GIO4/INT4

N5

GIO0/INT0

N6

GIO3/INT3

N14

SDR_CKE

N15

SDR_DQMLH

N17

SDR_A13

N18

SDR_A12

N19

CVDD6

P1

GIO2/INT2

P2

GIO1/INT1

P3

EMU0

P5

PWDN

P6

CGND2

P7

SCLK2

P8

YOUT6

P9

COUT4

P10

HDIN

P11

HDOUT

P12

RSV_1

P13

YIN3

P14

CLK135

P15

SDR_CS0

P17

SDR_DQMHL

P18

CGND6

P19

SDR_DQMLL

R1

EMU1

R2

RESET

R3

TEST0

R6

SDO1

R7

CGND3

R8

DVDD3318_1

R9

DGND3318_1

R10

COUT0

R11

VDOUT

R12

YIN7

R13

YIN0

R14

CIN6

R17

SDR_WE

R18

DVDD5

R19

SDR_DQMHH

T1

TEST1

T2

TEST2

T3

TEST4

T17

(XTAL INPUT) MXI

T18

SDR_RAS

T19

SDR_CAS

U1

TEST3

U2

SCAN

U3

USB_DM

U4

SDI1

U5

SCLK1

U6

TXD2

U7

YOUT5

U8

YOUT2

U9

COUT5

U10

COUT1

U11

RSV_2

U12

RSV_3

U13

YIN4

U14

CVDD5

U15

CIN5

U16

CIN1

U17

PLLVDD2

U18

CLK27

U19

DGND3

V1

USB_DP

V2

USB_VDD

V3

SDI2

V4

RXD1

V5

SDO2

V6

CVDD4

V7

YOUT4

V8

YOUT1

V9

COUT6

V10

COUT2

V11

DVDD3318_2

V12

CGND4

V13

YIN5

V14

YIN1

V15

CIN7

V16

CIN3

V17

CIN0

V18

CVDD10

V19

(XTAL OUTPUT) MXO

W2

DGND2

W3

RXD2

W4

DVDD4

W5

TXD1

W6

YOUT7

W7

YOUT3

W8

YOUT0

W9

COUT7

W10

COUT3

W11

VDIN

W12

RSV_4

W13

YIN6

W14

(Y SIGNAL INPUT) YIN2

W15

CGND5

W16

CIN4

W17

(C SIGNAL INPUT) CIN2

W18

PLLGND2

C314

OPEN

R303

0

TMS

EMU0

TRSTN

TDI

TDO

TCK

EMU1

DGND

DGND

R102

10K

R103

10K

R101

10K

R105

4.7K

R104

4.7K

R107

OPEN

R106

OPEN

R116

1K

CN101

1

TMS

2

TRSTN

3

TDI

4

GND

5

V3D

NC

6

7

TDO

8

GND

9

TCK

10

GND

11

TCK

12

GND

13

EMU0

14

EMU1

L102

3

4

1

2

V3D11

DGND

R176

1K

R969

OPEN

R194

10K

V3D11

V3D11

R175

OPEN

R170

2K

R174

VD

2K

2

3

4

1

6

5

MAIN BOARD

1

A

B

C

D

2

3

4

5

6

– 12 –

SCHEMATIC DIAGRAM OF MAIN BOARD (2/4)

FLASH ROM

(16M-BIT)

RTC

SYSTEM RESET

TO

PAGE 11

PAGE 11

TO

PAGE 13

PAGE 13

SDRAM

(128M-BIT)

RESETN

ETHER_RDYN

RESETN

ETHER_RDYN

SCLK1

SDO1

RESET3307N

INT4N_ETHER

VD

INT6N_ALM

AUX_O

RST_ETHER

ALM_O

ARMCK_O

LATCH

WDTN

WDTN

INT7N_RTC

INT7N_RTC

FLS_RYBY

RESETN

ETHER_RDYN

SCLK1

SDO1

RESET3307N

INT4N_ETHER

VD

INT6N_ALM

AUX_O

RST_ETHER

ALM_O

ARMCK_O

LATCH

SCLK1

(24.576MHz)

MXO

MXI

TST0

TST1

TST1

TST2

TST3

TST4

SDO1

SDO1

RESET3307N

RESET3307N

INT2N

INT0N

WDTN

WDTN

INT4N_ETHER

INT4N_ETHER

VDN

VD

INT7N_RTC

INT7N_RTC

INT6N_ALM

VD

INT7N_RTC

INT6N_ALM

AUX_O

ALM_O

ARMCK_O

FLS_RYBY

SDR_A[14_0]

SDR_A[14_0]

SDR_DQ[31_0]

SDR_CS0,WE,CAS,RAS,DQM[HH,HL,LH,LL],CKE,CLK

ED[15_0]

EA[20_0]

SDR_A[14_0]

SDR_DQ[31_0]

SDR_,CS0,WE,CAS,RAS,DQM[HH,HL,LH,LL],CKE,CLK

ED[15_0]

EA[20_0]

EM_CS[4,3,1,0]N,WEN,OEN

EM_CS[4,3,1,0]N,WEN,OEN

ED[15_0]

EA[20_0]

SDEN1N

RST_ETHER

AUX_O

ALM_O

ARMCK_O

LATCH

FLS_RYBY

RST_ETHER

DGND

R135

1M

C155

15P

C152

15P

X104

1

3

2

4

V3D11

DGND

R184

OPEN

R181

10K

R179

OPEN

R187

OPEN

R177

10K

R185

470

R182

OPEN

R178

OPEN

R188

470

R180

470

IC104

1

SENSE1

2

SENSE2

3

SENSE3

4

GND

5

RESET

6

RESET

7

MR

8

VDD

V5D

V3D

V18D

DGND

C169

1

V3D11

DGND

R186

10K

R191

120

R183

1K

R190 10K

R189 10K

R172

24K

C170 0.1

C195

0.1

V3D11

IC107

1

A

2

B

3

GND

4

Y

5

VCC

DGND

C106

0.1

R173

68K

R192

OPEN

R193

0

IC101

1

NC

2

A

3

GND

4

Y

5

VCC

R134

OPEN

R196

0

DGND

C107

0.1

V3D11

4.7K

R115

SW106

1

2

3

4

SW103

1

2

3

4

IC108

1

NC

2

INA

3

GND

4

OUTY

5

VCC

DGND

V3D

C196

0.1

SDR_DQ0

SDR_DQ1

SDR_DQ2

SDR_DQ3

SDR_DQ4

SDR_DQ5

SDR_DQ6

SDR_DQ7

SDR_DQ8

SDR_DQ9

SDR_DQ10

SDR_DQ11

SDR_DQ12

SDR_DQ13

SDR_DQ14

SDR_DQ15

SDR_DQ31

SDR_DQ30

SDR_DQ29

SDR_DQ28

SDR_DQ27

SDR_DQ26

SDR_DQ25

SDR_DQ24

SDR_DQ23

SDR_DQ22

SDR_DQ21

SDR_DQ20

SDR_DQ19

SDR_DQ18

SDR_DQ17

SDR_DQ16

L172

1

4

3

2

V3D

DGND

C171

0.1

C173

0.01

Z101

Z101-108 : 10K

1

2

3

4

5

4

5

4

5

4

5

4

5

4

5

4

5

4

5

6

7

8

Z102

1

2

3

6

7

8

Z103

1

2

3

6

7

8

Z104

1

2

3

6

7

8

Z105

1

2

3

6

7

8

Z106

1

2

3

6

7

8

Z107

1

2

3

6

7

8

Z108

1

2

3

6

7

8

SDR_DQ6

SDR_DQ5

SDR_DQ4

SDR_DQ3

SDR_DQ2

SDR_DQ1

SDR_DQ0

SDR_DQ7

SDR_DQ9

SDR_DQ10

SDR_DQ11

SDR_DQ12

SDR_DQ13

SDR_DQ14

SDR_DQ15

SDR_DQ8

SDR_A3

SDR_A2

SDR_A1

SDR_A0

SDR_A4

SDR_A5

SDR_A6

SDR_A7

SDR_A8

SDR_A9

SDR_A11

SDR_A0

SDR_DQ30

SDR_A10

SDR_DQ21

SDR_A9

SDR_A2

SDR_DQ16

SDR_A8

SDR_DQ25

SDR_DQ26

SDR_DQ22

SDR_DQ29

SDR_DQ19

SDR_A1

SDR_DQ27

SDR_DQ28

SDR_DQ17

SDR_A5

SDR_DQ20

SDR_A6

SDR_A11

SDR_DQ31

SDR_A7

SDR_DQ18

SDR_DQ23

SDR_DQ24

SDR_A3

SDR_A4

SDR_DQMHH

SDR_CLK

SDR_CKE

SDR_WE

SDR_CAS

SDR_RAS

SDR_CS0

SDR_WE

SDR_CAS

SDR_RAS

SDR_CS0

SDR_CLK

SDR_CKE

SDR_DQMHL

SDR_DQMLL

SDR_DQMLH

SDR_A13

SDR_A14

SDR_A12

SDR_A12

SDR_A14

SDR_A13

SDR_A10

IC105

1

Vcc1

2

DQ0

3

VccQ1

4

DQ1

5

DQ2

6

VssQ1

7

DQ3

8

DQ4

9

VccQ2

10

DQ5

11

DQ6

12

VssQ2

13

DQ7

14

Vcc2

15

LDQM

16

WE

17

CAS

18

RAS

19

CS

20

BA0(A13)

21

BA1(A12)

22

A10

23

A0

24

A1

25

A2

26

A3

27

Vcc3

28

Vss1

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

35

A11

36

NC1

37

CKE

38

CLK

39

UDQM

40

NC2

41

Vss2

42

DQ8

43

VccQ3

44

DQ9

45

DQ10

46

VssQ3

47

DQ11

48

DQ12

49

VccQ4

50

DQ13

51

DQ14

52

VssQ4

53

DQ15

54

Vss3

C188

10/10

DGND

C189

10/10

+

-

IC106

1

Vcc1

2

DQ0

3

VccQ1

4

DQ1

5

DQ2

6

VssQ1

7

DQ3

8

DQ4

9

VccQ2

10

DQ5

11

DQ6

12

VssQ2

13

DQ7

14

Vcc2

15

LDQM

16

WE

17

CAS

18

RAS

19

CS

20

BA0(A13)

21

BA1(A12)

22

A10

23

A0

24

A1

25

A2

26

A3

27

Vcc3

28

Vss1

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

35

A11

36

NC1

37

CKE

38

CLK

39

UDQM

40

NC2

41

Vss2

42

DQ8

43

VccQ3

44

DQ9

45

DQ10

46

VssQ3

47

DQ11

48

DQ12

49

VccQ4

50

DQ13

51

DQ14

52

VssQ4

53

DQ15

54

Vss3

DGND

V3D

L177

1

4

3

2

L176

1

4

3

2

V3D

C191

0.1

C178

0.1

C180

0.1

C179

0.1

C181

0.1

C190

0.1

C182

0.1

C174

0.1

C187

0.1

C184

0.1

C183

0.1

C185

0.1

C186

0.1

C193

0.1

C175

0.1

C192

0.1

+

-

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

EA1

EA2

EA3

EA4

EA5

EA6

EA7

EA8

EA9

EA10

EA11

EA12

EA13

EA14

EA15

EA16

EA17

EA18

EA19

EA0

EA2

ED3

ED2

EA0

EM_CS3N

RESETN

RESETN

WDTN

EM_OEN

EM_WEN

RESETN

FLS_RYBY

EA3

ED1

EA1

ED0

EM_WEN

EM_OEN

EM_CS0N

EA20

DGND

V3D

C238 10/10

+

-

L239

1

4

3

2

IC201

1

CS

2

CE

3

TMOUT

4

NC1

5

A0

6

A1

7

A2

8

A3

9

RD

10

VSS

12

D0

13

D1

14

D2

15

D3

16

INTR

17

NC2

18

OSCIN

19

OSCOUT

20

VDD

11

WR

DGND

X201

3

4

2

1

V3D24

VBAT

DGND

L214

1

4

3

2

C216

10/10

DGND

V3D24

L293

1

4

3

2

V3D

R203

10K

R211

10K

R202

10K

R219

OPEN

R218

OPEN

R217

OPEN

R220

4.7K

C240

0.1

C213

0.1

C217

0.1

C237

0.01

C236 0.01

C219

(32.768KHz)

10P

C220

10P

IC204

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

A19

10

NC_1

11

WE

12

RESET

13

NC_2

14

NC_3

15

RY/BY

16

A18

17

A17

18

A7

19

A6

20

A5

21

A4

22

A3

23

A2

24

A1

25

A0

26

CE

27

VSS_1

28

OE

29

DQ0

30

DQ8

31

DQ1

32

DQ9

33

DQ2

34

DQ10

35

DQ3

36

DQ11

37

VCC

38

DQ4

39

DQ12

40

DQ5

41

DQ13

42

DQ6

43

DQ14

44

DQ7

45

DQ15/A-1

46

VSS_2

47

BYTE

48

A16

+

-

R274

0

EM_CS[4,3,1,0]N,WEN,OEN

7

8

9

10

11

12

7

– 13 –

SCHEMATIC DIAGRAM OF MAIN BOARD (3/4)

TO PLD

D214

POWER

LED

POWER

LED

PLD

SW203

SETTING

RESET

SWITCH

SETTING

RESET

SWITCH

SW204

HTML

DOCUMENT

INITIALIZATION

SWITCH

HTML

DOCUMENT

INITIALIZATION

SWITCH

JK201

ETHERNET

CONNECTOR

(BUILT-IN

ACCESS LED,

LINK LED)

ETHERNET

CONNECTOR

(BUILT-IN

ACCESS LED,

LINK LED)

ETHERNET

CONTROLLER

TO

PAGE 12

PAGE 12

TO

PAGE 14

PAGE 14

EEPROM

*

SW201

(Bit 1) : Fix to pin 6 side.

(Bit 2) : Fix to pin 3 side.

(Bit 2) : Fix to pin 3 side.

RESETN

ETHER_RDYN

SCLK1

SDO1

RESET3307N

RESET3307N

INT4N_ETHER

INT4N_ETHER

VD

INT6N_ALM

INT6N_ALM

AUX_O

RST_ETHER

ALM_O

RST_ETHER

ALM_I

ALM_I

ARMCK_O

ARMCK_O

LATCH

RESETN

ETHER_RDYN

SCLK1

SDO1

VD

AUX_O

ALM_O

LATCH

ETHER_IRQ

ETHER_LED

E_RESET

ETHER_LED

E_RESET

ALM_I

RESETN

SCLK1

SDO1

VD

AUX_O

ALM_O

LATCH

ED[15_0]

EA[20_0]

ED0

TDO

EA19

EA2

EA1

EA0

ED3

ED2

ED1

V3D

DGND

C254

10/10

L255

1

4

3

2

V3D

D212

1

2

3

D211

1

2

3

D210

1

2

3

D213

1

2

3

D209

OPEN

D208

OPEN

D206

OPEN

D207

OPEN

V3D21

DGND

L242

1

4

3

2

V3D

V3D21

L258

1

4

3

2

EM_CS1N

TCK

TDI

V3D21

V3D21

V3D

DGND

DGND

R227

680

R246

ARMCK_O

10K

R234

10K

R236

10K

R229

OPEN

R255

10K

R233

OPEN

R235

OPEN

R231

OPEN

R232

OPEN

R224

OPEN

OPEN

R226

OPEN

OPEN

R223

OPEN

OPEN

R225

OPEN

OPEN

R222

10K

C257 0.1

*

SW201

1

(Bit 2)

(Bit 1)

2

3

4

5

6

CN204

1

VCC

2

TDO

3

TDI

4

ISPEN

5

TMS

6

GND

7

TCK

D214

C248

0.1

DGND

DGND

C246

0.1

C221

0.1

C218

0.1

V3D21

C222

10/10

+

-

+

-

C224 0.1

L223

1

4

3

2

V18D

SW203

SW204

1

3

2

4

1

3

2

4

R304

0

R305

0

C315

OPEN

C316

OPEN

C317

OPEN

C318

OPEN

C319

OPEN

DGND

R306

0

R308

0

R307

0

Q205

OPEN

Q206

OPEN

Q207

OPEN

Q208

OPEN

Q209

IC202

1

TDI

2

A5

3

A6

4

A7

5

GND[Bank0]

6

VCCO[Bank0]

7

A8

8

A9

9

A10

10

A11

11

TCK

12

VCC_1

13

GND_1

14

A12

15

A13

16

A14

17

A15

18

CLK1/I

19

CLK2/I

20

B0

21

B1

22

B2

23

B3

24

B4

25

TMS

26

B5

27

B6

28

B7

TMS

29

GND[Bank1]

30

VCCO[Bank1]

31

B8

32

B9

33

B10

34

B11

35

TDO

36

VCC_2

37

GND_2

38

B12

39

B13

40

B14

41

B15/GOE1

42

CLK3/I

43

CLK0/I

44

A0/GOE0

45

A1

46

A2

47

A3

48

A4

EM_WEN

EM_OEN

EA8

EA7

EA6

EA5

EA4

EA3

EA2

EA1

EA9

ED0

ED1

ED2

ED3

ED4

ED5

ED6

ED7

ED8

ED9

ED10

ED11

ED12

ED13

ED14

ED15

EA0

ETHER_RDYN

EM_CS4N

EM_WEN

EM_OEN

IC209

1

NC1

2

VCC

3

CS

4

SK

5

DI

6

DO

7

GND

8

NC2

C270

4.7/16

+

-

+

-

C282

4.7/16

V3D23

DGND

DGND

V3D23

R269

49.9

AGND

D215

OPEN

V3D23

V3D23

R268

49.9

C289

1000P

R267

49.9

R262

49.9

DGND

C288

0.1

AGND

C290

1000P

C287

0.01

C286

+

-

4.7/16

AGND

R261

0

V3D23

L274

1

4

3

2

V3D

DGND

C284

4.7/16

L275

1

4

3

2

V3D

C271

4.7/16

DGND

C272

10/10

10/10

+

-

+

-

+

-

+

-

C285

L276

1

4

3

2

V3D

AGND

ETHER_LED

C281

4.7/16

V3D

C269

4.7/16

+

-

+

-

L273

1

4

3

2

V3D23

DGND

R249

20K

R250

2.49K

R251

24.9K

R244

OPEN

R241

10K

R243

10K

R245

10K

R240

OPEN

R242

OPEN

R239

10K

R263

OPEN

R265

330

R264

330

R257

10K

10K

R256

OPEN

R254

R253

OPEN

R237

10K

R238

10K

R228

R311

0

10K

C277

0.1

C278

0.1

C280

0.1

C279

0.1

C249

0.1

C264

0.01

C247 0.01

C250 0.01

C256 0.01

C259

0.1

C261

C260

0.01

C263

0.01

0.01

0.01

C262

C251

0.01

C267

0.1

C245

0.01

C252

1000P

C253

0.01

C243

0.01

C244

0.01

C266

1000P

C265

1000P

R209

0

IC208

1

NC1/AEN

2

DTACK/RDY

3

RESET

4

LDS/SA[0]

5

SA[1]

6

SA[2]

7

SA[3]

8

SA[4]

9

SA[5]

10

SA[6]

11

SA[7]

12

SA[8]

13

VDD1

14

VSS1

15

SA[9]

16

IRO/IRQ

17

NC2

18

R/W/IOWR

19

NC3/IORD

20

NC4

21

NC5

22

UDS/BHE

23

SD[15]

24

SD[14]

25

SD[13]

26

SD[12]

27

VDD2

28

VSS2

29

SD[11]

30

SD[10]

31

SD[9]

32

SD[8]

33

SD[7]

34

VSS3

35

SD[6]

36

SD[5]

37

SD[4]

38

SD[3]

39

SD[2]

40

VDD3

41

SD[1]

42

SD[0]

43

VSS4

44

CLKO25M

45

BIST

46

IDDQ

47

TEST2

48

EEDO

49

EEDI

50

EECK

51

EECS

52

VSS5

53

VDD4

54

VSS6

55

VSSA1

56

VDDA1

57

VDD5

58

CPU[0]

59

CPU[1]

60

I_LINK

61

I_SPEED

62

I_ACT

63

VSS7

64

NC6

65

TEST1

66

MDIO

67

MDC

68

VSSA2

69

VDDA2

70

TPIP

71

TPIN

72

VSSA3

73

VDDA3

74

REXTBS

75

VSSA4

76

VDDM

77

VSSM1

78

VDDPD

79

LCLK/XTALIN

80

XTALOUT

81

VSSPD

82

VDDA4

83

REXT100

84

REXT10

85

VSSA5

86

VSSO1

87

TPON

88

TPOP

89

VSSO2

90

VSSO3

91

VDDO

92

ZVREG

93

VSSM2

94

VSS8

95

RXD[0]

96

RXD[1]

97

RXD[2]

98

RXD[3]

99

RX_CLK

100

CRS

101

COL

102

RX_DV

103

GP[0]/LINK

104

VDD6

105

VSS9

106

GP[1]/DPX

107

TX_CLK

108

TX_EN

109

TXD[0]

110

TXD[1]

111

TXD[2]

112

TXD[3]

113

GPI[2]/SPD

114

VDD7

115

VSS10

116

I_OP

117

IO_BASE[0]

118

IO_BASE[1]

119

IO_BASE[2]

120

GPO[0]

121

NC7

122

NC8

123

NC9

124

NC10

125

NC11

126

VDD8

127

VSS11

128

CS

JK201

1

TD+

2

TD-

3

CT

4

GND

5

GND

6

CT

7

RD+

8

RD-

V3D23

V3D23

C291

0.01

C292

0.01

9

10

ACCESS LED_GREEN

11

LINK LED_YELLOW

12

R309

0

C320

OPEN

DGND

Q210

Q211

C283

15P

C268

15P

X202

L208

L209

1

2

4

3

2

1

3

4

(25MHz)

1

3

2

4

I/O BASE ADDRESS : 300H

ISA MODE

EM_CS[4,3,1,0]N,WEN,OEN

8

9

13

14

15

16

17

18

Click on the first or last page to see other WV-NM100 service manuals if exist.