Sharp LC-46X8E Service Manual ▷ View online

LC-46X8E/S/RU

5 – 9

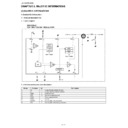

1.5. IC3501 (RH-iXC163WJQZQ)

1.5.1 Block Diagram

1.5.2 Pin Connections and short description

Pin No.

Pin Name

I/O

Pin Function

62, 63

CK, CK

I

The differential system clock Input.

All of the inputs are sampled on the rising edge of the clock except DQ's and DM's that are sam-

pled on both edges of the DQS.

All of the inputs are sampled on the rising edge of the clock except DQ's and DM's that are sam-

pled on both edges of the DQS.

22

CKE

I

Activates the CK signal when high and deactivates the CK signal when low. By deactivating the

clock, CKE low indicates the Power down mode or Self refresh mode.

clock, CKE low indicates the Power down mode or Self refresh mode.

12

CS

I

CS enables the command decoder when low and disabled the command decoder when high.

When the command decoder is disabled, new commands are ignored but previous operations con-

tinue.

When the command decoder is disabled, new commands are ignored but previous operations con-

tinue.

11

RAS

I

Latches row addresses on the positive going edge of the CK with RAS low. Enables row access &

precharge.

precharge.

10

CAS

I

Latches column addresses on the positive going edge of the CK with CAS low. Enables column

access.

access.

53

WE

I

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Latches data in starting from CAS, WE active.

1, 28, 7, 34

DQS0-3

I/O

Data input and output are synchronized with both edge of DQS.

44, 67, 50, 35

DM0-3

I

Data In mask. Data In is masked by DM Latency=0 when DM is high in burst write. DM0 for DQ0 ~

DQ7, DM1 for DQ8 ~ DQ15, DM2 for DQ16 ~ DQ23, DM3 for DQ24 ~ DQ31.

DQ7, DM1 for DQ8 ~ DQ15, DM2 for DQ16 ~ DQ23, DM3 for DQ24 ~ DQ31.

40, 78, 41, 42, 2, 46,

3, 4, 26, 65, 27, 66,

29, 68, 30, 69, 48, 5,

49, 6, 51, 8, 9, 52, 31,

32, 71, 33, 37, 38, 75,

39

3, 4, 26, 65, 27, 66,

29, 68, 30, 69, 48, 5,

49, 6, 51, 8, 9, 52, 31,

32, 71, 33, 37, 38, 75,

39

DQ0-31

I/O

Data inputs/Outputs are multiplexed on the same pins.

14, 56

BA0, BA1

I

Selects which bank is to be active.

LC-46X8E/S/RU

5 – 10

1.6. IC7504 (VHiTDA9886+-1)

1.6.1 Block Diagram

15, 16, 57, 17, 18, 60,

19, 20, 21, 59, 90, 58

19, 20, 21, 59, 90, 58

A0-11

I

Row/Column addresses are multiplexed on the same pins.

Row addresses : RA0 ~ RA11, Column addresses : CA0 ~ CA7.

Column address CA8 is used for auto precharge.

Row addresses : RA0 ~ RA11, Column addresses : CA0 ~ CA7.

Column address CA8 is used for auto precharge.

82, 88, 91, 92, 95,

101, 105, 106

101, 105, 106

VDD

—

Power for the input buffers and core logic.

89, 94, 109, 115, 116,

117, 118, 124, 126,

127, 129, 130, 131,

132, 133, 134, 135,

136, 137, 138, 139,

140, 141, 142, 143,

144

117, 118, 124, 126,

127, 129, 130, 131,

132, 133, 134, 135,

136, 137, 138, 139,

140, 141, 142, 143,

144

VSS

—

Ground for the input buffers and core logic.

45, 47, 70, 72, 74, 76,

77, 79, 83, 84, 86, 87,

96, 97, 99, 100

77, 79, 83, 84, 86, 87,

96, 97, 99, 100

VDDQ

—

Isolated power supply for the output buffers to provide improved noise immunity.

36, 43, 81, 102, 103,

104, 107, 108, 110,

111, 112, 113, 114,

119, 120, 121, 122,

123, 125, 128

104, 107, 108, 110,

111, 112, 113, 114,

119, 120, 121, 122,

123, 125, 128

VSSQ

—

Isolated ground for the output buffers to provide improved noise immunity.

23

VREF

—

Reference voltage for inputs, used for SSTL interface.

93, 61

RFU1/RFU2

—

Reserved for Future Use.

13, 24, 25, 54, 55, 64,

73, 80, 85, 98

73, 80, 85, 98

NC

—

No Connection.

Pin No.

Pin Name

I/O

Pin Function

LC-46X8E/S/RU

5 – 11

1.6.2 Pin Connections and short description

1.7. IC8101 (RH-iXC011WJQZQ)

1.7.1 Block Diagram

Pin No.

Pin Name

I/O

Pin Function

1

VIF1

I

VIF differential input 1

2

VIF2

I

VIF differential input 2

3

OP1

O

Output port 1; open-collector.

4

FMPLL

I

FM-PLL for loop filter.

5

DEEM

O

De-emphasis output for capacitor.

6

AFD

I

AF decoupling input for capacitor

7

DGND

—

Digital ground.

8

AUD

O

Audio output.

9

TOP

I

Tuner AGC TakeOver Pint (TOP) for resistor adjustment.

10

SDA

I/O

I2C-bus data input and output.

11

SCL

I

I2C-bus clock input.

12

SIOMAD

O

Sound intercarrier output and MAD select with resistor.

13

N.C.

—

Not connected.

14

TAGC

O

Tuner AGC output.

15

REF

I

4 MHz crystal or reference signal input.

16

VAGC(1)

I

VIF-AGC for capacitor.

17

CVBS

O

Composite video output.

18

AGND

—

Analog ground.

19

VPLL

I

VIF-PLL for loop filter.

20

VP

—

Supply voltage.

21

AFC

O

AFC output.

22

OP2

O

Output port 2; open-collector.

23

SIF1

I

SIF differential input 1 and MAD select with resistor.

24

SIF2

I

SIF differential input 2 and MAD select with resistor.

LC-46X8E/S/RU

5 – 12

1.7.2 Pin Connections and short description

Pin No.

Pin Name

I/O

Pin Function

Sheet Name

DAC Interface

AD2

AD2

VDDZ_DAC

—

Digital power for DAC (+3.3V).

D3.3V

AD3

VSSZ_DAC

—

Digital ground for DAC.

GND

AD1

DAC_VS

I/O

DAC vsync.

open

AE1

DAC_HS

I/O

DAC hsync.

open

AE2

DAC_CLK

I/O

DAC clock

open

AE4

DAC_DE

I/O

DAC DE

open

AE3

DAC_FLD

I/O

DAC field.

open

AA5

AVSS51

—

Analog ground for DAC (for bias circuit).

GND

AB5

COMP

—

Bias for DAC coupling capacitor.

C-D3.3V

AB4

IRSET

I

Bias for DAC current source.

R-GND

AB3

CVBS_B

I

DAC blue or PB (no connected).

TL8105

AB2

ADVSS2

—

Analog ground for DAC (for DAC's AVSS52).

GND

AB1

ADVDD2

—

Analog power for DAC (+3.3V).

D3.3V

AC1

C_G

I

DAC green or Y (no connected).

TL8106

AC2

AVSS50

—

Analog ground for DAC.

GND

AC3

AVDD50

—

Analog power for DAC (+3.3V).

D3.3V

AC4

Y_R

I

DAC red or PR (no connected).

TL8109

AC5

ADVSS2

—

Analog ground for DAC (for DAC's AVSS52).

GND

AD5

ADVDD2

—

Analog power for DAC (+3.3V).

D3.3V

AD4

VM

I

DAC VM

DTM_CVBS

ADC Interface

N2

N2

AVDD

—

ADC power +3.3V.

D3.3V

N3

VIN1

I

VRADC INPUT1 (no connected)

R-GND

N4

VIN2

I

VRADC INPUT2 (no connected)

R-GND

N5

AVSS

—

ADC ground.

GND

USB Interface

R3

R3

USB_PPON_PP

O

USB Power on control.

USB_PWRON

R2

USB_OC_PP

I

USB over current control.

USB_PWRFLT

P5

VDDA

—

Analog core +3.3V supply.

D3.3V

P4

DN

O

Negative output channel.

USB_DN

P3

DP

O

Positive output channel

USB_DP

P2

VSSA

—

Analog core ground.

GND

P1

RREFEXT

—

External resistor connection for current reference.

R-GND

R5

VSSP

—

PLL ground pin Double Bond.

GND

R4

VDDP

—

PLL +1.2V supply Double Bond.

C-GND

LVDS Interface

AJ5

AJ5

LVDS_VSSP

—

LVDS PLL Ground.

GND

AJ3

LVDS_VDDP

—

LVDS PLL Power supply (+3.3V).

D3.3V

AK5

LVDS_VSSO

—

LVDS Output buffer VSS (Long pad)

GND

AK4

LVDS_VDDO

—

LVDS Output buffer VDD (+3.3V).

D3.3V

AK1

TF2P

O

LVDS Positive Output. (no connected)

open

AK2

TF2M

O

LVDS Negative Output. (no connected)

open

AL1

TE2P

O

LVDS Positive Output. (no connected)

open

AL2

TE2M

O

LVDS Negative Output. (no connected)

open

AM1

TD2P

O

LVDS Positive Output. (no connected)

open

AM2

TD2M

O

LVDS Negative Output. (no connected)

open

AN1

TCLK2P

O

LVDS Positive clock Output. (no connected)

open

AN2

TCLK2M

O

LVDS Negative clock Output. (no connected)

open

AP1

TC2P

O

LVDS Positive Output. (no connected)

open

AP2

TC2M

O

LVDS Negative Output. (no connected)

open

AM4

LVDS_VDDO

—

LVDS Output buffer VDD (+3.3V).

D3.3V

AP3

TB2P

O

LVDS Positive Output. (no connected)

open

AN3

TB2M

O

LVDS Negative Output. (no connected)

open

AP4

TA2P

O

LVDS Positive Output. (no connected)

open

AN4

TA2M

O

LVDS Negative Output. (no connected)

open

AJ6

LVDS_VSSO

—

LVDS Output buffer VSS.

GND

AP5

TF1P

O

LVDS Positive Output. (no connected)

open

AN5

TF1M

O

LVDS Negative Output. (no connected)

open

AP6

TE1P

O

LVDS Positive Output. (no connected)

open

AN6

TE1M

O

LVDS Negative Output. (no connected)

open

AP7

TD1P

O

LVDS Positive Output. (no connected)

open

AN7

TD1M

O

LVDS Negative Output. (no connected)

open

Click on the first or last page to see other LC-46X8E service manuals if exist.