Sharp LC-46X8E Service Manual ▷ View online

LC-46X8E/S/RU

5 – 5

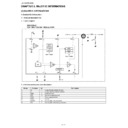

1.4. IC3301 (RH-iXC010WJQZQ)

1.4.1 Block Diagram

1.4.2 Pin Connections and short description

Pin No.

Pin Name

I/O

Pin Function

Sheet Name

Destination

Ball Assignments for CPU Host Interface.

K20, K19, K18,

K17, L20, L19,

L18, L17

K20, K19, K18,

K17, L20, L19,

L18, L17

A_D[7:0]

I/O

Multiplexed address and data bus powered by VDDH/VSS. ADAT_O-7

CPU

M17, M18, M19,

M20, N20, N19,

N18, N17

M20, N20, N19,

N18, N17

ADDR[7:0]

I

CPU Address. (not connected)

TP3301-8

CPU

J18

ALE

I

Address latch enables.

8051_ALE

CPU

J19

WR#

I

CPU Write.

8051_WR

CPU

J20

RD#

I

CPU Read.

8051_RD

CPU

H17

SDA

I/O

I2C data.

R-+3.3V

H18

SCL

I

I2C clock.

R-+3.3V

J17

CPU_CS

I

UX chip select pin from MCU. Active Low.

8051_CS

CPU

Ball Assignments for Analog Support Interface.

W1

W1

XTALI

I

Input for Clock Synthesizer. Supports 24MHz Oscillator or

crystal powered by analog PLL.

crystal powered by analog PLL.

XTAL

X-TAL,27M

Y1

XTALO

O

Used in conjunction with XTALI for 24MHz crystal output

powered by analog PLL.

powered by analog PLL.

XTAL

X-TAL,27M

U2

MLF1

I

Low pass filter node for memory clock PLL powered by

analog PLL.

analog PLL.

CR_+B

R4

PLF2

I

Low pass filter node for video clock PLL powered by analog

PLL.

PLL.

+3.3V

Ball Assignments for Analog Input Interface.

Y4

Y4

CVBS1

I

Composite video input 1.

MAIN_Y/V_TR

FROM-V-SW

V6

Y_G1

I

Y input 1 of component or G input 1 of PC RGB.

SCART_G_TR

FROM-V-SW

LC-46X8E/S/RU

5 – 6

W6

Y_G2

I

Y input 2 of component or G input 2 of PC RGB.

COMP_Y_TR

FROM-V-SW

Y6

Y_G3

I

Y input 3 of component or G input 3 of PC RGB.

DTM_Y

open

W2

CVBS_OUT1

I

CVBS Output 1. (not connected)

open

V2

CVBS_OUT2

I

CVBS Output 2. (not connected)

open

V9

C

I

C input of S-Video.

MAIN_C_TR

FROM-V-SW

W9

PB_B1

I

PB input 1 of component.

SCART_B_TR

FROM-V-SW

Y9

PB_B2

I

PB input 2 of component.

COMP_Pb_TR

FROM-V-SW

Y10

PB_B3

I

PB input 3 of component.

DTM_Pb

open

Y8

PR_R1

I

PR input 1 of component.

SCART_R_TR

FROM-V-SW

W8

PR_R2

I

PR input 2 of component.

COMP_Pr_TR

FROM-V-SW

V8

PR_R3

I

PR input 3 of component.

DTM_PR

open

W4, V4

FS2, FS1

I

SCART function select 2, 1.

W4

R-GND

U4, Y5

FB2, FB1

I

SCART FB input for Port 2, Port 1.

V4

R-GND

V10

AIN_H

I

Hsync input (PC RGB input)

PC-H

FROM EXT7

U10

AIN_V

I

Vsync input (PC RGB input)

PC-V

FROM EXT7

U8

PC_R

I

PC Red input.

PC_R

FROM EXT7

Y7

PC_G

I

PC Green input.

PC_G

FROM EXT7

W10

PC_B

I

PC Blue INPUT.

PC_B

FROM EXT7

Ball Assignments for Capture Interface (TV & RGB).

U18, U19, U20,

T20, T18, T17,

R19, R20

U18, U19, U20,

T20, T18, T17,

R19, R20

DPB[15:8]

(DP_B[15:8])

(DP_B[15:8])

I/O

Digital input port[15:8] (Output reserved)

AD_RA0-8

AD_GA0-8

AD_BA0-8

AD_GA0-8

AD_BA0-8

TO CPU

Y12, U13, V13,

W13, Y13, Y14,

W14, V14, U14,

U15, V15, W15,

Y16, W16, V16,

U16, U17, V17,

W17, Y17, Y18,

W18, V18, W19

W13, Y13, Y14,

W14, V14, U14,

U15, V15, W15,

Y16, W16, V16,

U16, U17, V17,

W17, Y17, Y18,

W18, V18, W19

DPA[23:0]

(DP_A[23:0])

(DP_A[23:0])

I/O

Digital input/output port [23:0]

AD_RA0-8

AD_GA0-8

AD_BA0-8

AD_GA0-8

AD_BA0-8

TO CPU

T19

DPB_CLK (CLK_B)

I/O

Digital port B CLK input/output. (no connected)

open

Y15

DPA_CLK (CLK_A)

I/O

Digital port A CLK input/output.

AD_CLK

TO CPU

W20

DPE_DE (DE_B)

I/O

DE input/output of Digital port B.

AD_DE

TO CPU

Y20

DPA_VS (VS_A)

I/O

Vsync input/output of Digital port A.

AD_VD

TO CPU

Y19

DPA_HS (HS_A)

I/O

Hsync input/output of Digital port A.

AD_HD

TO CPU

V20

DPB_VS (VS_B)

I/O

Vsync input/output of Digital port B. (no connected)

open

V19

DPB_HS (HS_B)

I/O

Hsync input/output of Digital port B. (no connected)

open

P19

HS

I/O

Hsync output for Digital port.

R-+B

P17

VS

I/O

Vsync output for Digital port.

R-+B

Ball Assignments for Frame Buffer Memory.

D3, C3, C2, C1,

A1, A2, A3, C5,

A4, B5, A5, D6,

A7, B7, C7, D7,

D8, C8, B8, A8,

D9, D10, C10,

B10, A10, A11,

B11, C11, D12,

A13, B13, C13

D3, C3, C2, C1,

A1, A2, A3, C5,

A4, B5, A5, D6,

A7, B7, C7, D7,

D8, C8, B8, A8,

D9, D10, C10,

B10, A10, A11,

B11, C11, D12,

A13, B13, C13

MD[31:0]

I/O

Memory data.

WX_MD31-0

TO SDRAM

F1, F2, F3, F4,

G4, G3, G2, G1,

H1, H2, H3, H4

G4, G3, G2, G1,

H1, H2, H3, H4

MA[11-0]

I/O

Memory Address.

WX_MA11-0

TO SDRAM

J2

RAS#

O

RAS# signal powered by VDDH/VSS.

WX_RAS

TO SDRAM

J1

CAS#

O

CAS# signal powered by VDDH/VSS.

WX_CAS

TO SDRAM

K1

WE#

O

WE#, write enable signal powered by VDDH/VSS.

WX_WE

TO SDRAM

J3

CS1#

O

Chip select 0 for the first 2/4 Mbyte of SGRAM/SDRAM

powered by VDDH/VSS.

powered by VDDH/VSS.

WX_CS1

TO SDRAM

J4

CS0#

O

Chip select 1 for the second 2/4 Mbyte of SGRAM/SDRAM

powered by VDDH/VSS.

powered by VDDH/VSS.

WX_CS0

TO SDRAM

D1

MCK0

O

Memory clock+.

WX_MCLK0

TO SDRAM

E1

MCK0#

O

Memory clock-.

WX_MCLK0#

TO SDRAM

B1, A6, A9, A12

DQM[3:0]

O

Read/Write bytes enable powered by VDDH/VSS.

WX_DQM3-0

TO SDRAM

K2

CLKE

O

Memory Clock Enable.

WX_CLKE

TO SDRAM

B2, B6, B9, B12

DQS[3:0]

I/O

Memory data strobe.

WX_DQS3-0

TO SDRAM

E3

MVREF

—

DDR voltage reference.

WX_DDR_VREF

TO SDRAM

K3

BA0

O

Bank address select.

WX_BA0

TO SDRAM

Pin No.

Pin Name

I/O

Pin Function

Sheet Name

Destination

LC-46X8E/S/RU

5 – 7

K4

BA1

O

Bank address select.

WX_BA1

TO SDRAM

Ball Assignments for Power and Ground.

C14, C15, D13,

D14, D15, E13,

E14, E15, G16,

H5, H16, J5,

J16, K5, K16,

R16, T14, T15

C14, C15, D13,

D14, D15, E13,

E14, E15, G16,

H5, H16, J5,

J16, K5, K16,

R16, T14, T15

VDDC

—

1.2V Digital core power.

D1.2V

E4, E7

VSSR

—

Digital memory reference Ground.

GND

E2, E8

VDDR

—

2.5V Digital power for Memory.

2.5V

B4, C4, D4, D5,

D11, E5, E6, E9,

E10, E11, E12,

F5, G5

D11, E5, E6, E9,

E10, E11, E12,

F5, G5

VDDM

—

2.5V Memory interface power. Output driver.

2.5V

L16, M16, N16,

P16, T12, T13,

R17, R18

P16, T12, T13,

R17, R18

VDDH

—

3.3V Digital I/O power.

D3.3V

B3, C6, C9,

C12, D2, H8,

H9, H10, H11,

H12, H13, J8,

J9, J10, J11,

J12, J13, K8,

K9, K10,

K11,K12, K13,

L5, L8, L9, L10,

L11, L12, L13,

M8, M9, M10,

M11, M12, M13,

N8, N9, N10,

N11, N12, N13,

P18, T16, H20

C12, D2, H8,

H9, H10, H11,

H12, H13, J8,

J9, J10, J11,

J12, J13, K8,

K9, K10,

K11,K12, K13,

L5, L8, L9, L10,

L11, L12, L13,

M8, M9, M10,

M11, M12, M13,

N8, N9, N10,

N11, N12, N13,

P18, T16, H20

VSS

—

Core and Digital IO ground.

GND

W3

AVSS_BG_ASS

—

ADC ground.

GND

V3

AVDD3_BG_ASS

—

3.3V ADC power.

R-D3.3V

T3

PAVDD1

—

3.3V power for MCLK PLL.

R-D3.3V

T2

PAVSS1

—

Ground for MCLK PLL.

GND

R3

PAVSS2

—

Ground for PCLK PLL.

GND

T4

PAVDD2

—

3.3V power for PCLK PLL.

R-D3.3V

U6, T8, U7, U5

AVDD_ADC[4, 3, 2, 1]

—

1.2V power for analog ADC.

L-D1.2V

T6, T9, T7, T5

AVSS_ADC[4, 3, 2, 1]

—

Ground for analog ADC.

GND

U9, Y3

AVDD3_ADC[2, 1]

—

3.3V ADC power.

L-D3.3V

U3

AVDD3_OUTBUF

—

3.3V power for output buffer.

R-D3.3V

Y2

AVSS_OUTBUF

—

3.3V ground for output buffer.

GND

C18, C19

LVDS_VSSO

—

LVDS out buffer ground.

GND

C16

LVDS_VSSD

—

LVDS Digital ground.

GND

E16

LVDS_VSSA

—

LVDS analog ground.

GND

E18

LVDS_VSSP

—

LVDS PLL GND.

GND

D18

LVDS_VDDP

—

LVDS PLL VDD.

R-D1.2V

E17

LVDS_VDDA

—

LVDS analog VDD.

R-D3.3V

D16

LVDS_VDDD

—

LVDS Digital VDD.

R-D3.3V

C17, D17

LVDS_VDDO

—

LVDS out buffer VDD.

R-D3.3V

P20

NC

—

Not connected.

open

U1

AVDDAPLL

—

1.2V analog PLL power.

D1.2V

V1

AVSSAPLL

—

1.2V analog GND.

GND

R2

AVDDLLPLL

—

1.2V Line Lock PLL power.

D1.2V

T1

AVSSLLPLL

—

1.2V Line Lock PLL GND.

GND

Miscellaneous Ball Assignments.

F18

F18

RESET

I

System reset forces the chip to a known state. Active High. SVP_RESET

TO CPLD

G18

INTN

I/O

Interrupt signal (active low).

N_CPLD_INT

TO CPLD

G17

PWM0

I/O

PWM I/O. (no connected)

open

F16

V5SF

I

5V reference voltage (must be connected to 5V even in

standby mode, when CPU I/O is 5V)

standby mode, when CPU I/O is 5V)

D5V

F17

TESTMODE

I

Reserved (Connected to ground).

-

R-GND

LVDS Output Ball Assignments.

A14

A14

TA1P

O

LVDS 1st Channel Differential positive data out.

TA1+

TO LCD CONT

B14

TA1M

O

LVDS 1st Channel Differential negative data out.

TA1-

TO LCD CONT

A15

TB1P

O

LVDS 1st Channel Differential positive data out.

TB1+

TO LCD CONT

Pin No.

Pin Name

I/O

Pin Function

Sheet Name

Destination

LC-46X8E/S/RU

5 – 8

B15

TB1M

O

LVDS 1st Channel Differential negative data out.

TB1-

TO LCD CONT

A16

TC1P

O

LVDS 1st Channel Differential positive data out.

TC1+

TO LCD CONT

B16

TC1M

O

LVDS 1st Channel Differential negative data out.

TC1-

TO LCD CONT

A18

TD1P

O

LVDS 1st Channel Differential positive data out.

TD1+

TO LCD CONT

B18

TD1M

O

LVDS 1st Channel Differential negative data out.

TD1-

TO LCD CONT

A19

TE1P

O

LVDS 1st Channel Differential positive data out.

TE1+

TO LCD CONT

B19

TE1M

O

LVDS 1st Channel Differential negative data out.

TE1-

TO LCD CONT

B17

TCLK1M

O

LVDS 1st Channel Differential positive CLK out.

TCLK1-

TO LCD CONT

A17

TCLK1P

O

LVDS 1st Channel Differential negative CLK out.

TCLK1+

TO LCD CONT

F19

TCLK2M

O

LVDS 2st Channel Differential positive CLK out.

TCLK2-

TO LCD CONT

E20

TCLK2P

O

LVDS 2st Channel Differential negative CLK out.

TCLK2+

TO LCD CONT

G20

TE2P

O

LVDS 2st Channel Differential positive data out.

TE2+

TO LCD CONT

H19

TE2M

O

LVDS 2st Channel Differential negative data out.

TE2-

TO LCD CONT

P20

TD2P

O

LVDS 2st Channel Differential positive data out.

TD2+

TO LCD CONT

G19

TD2M

O

LVDS 2st Channel Differential negative data out.

TD2-

TO LCD CONT

D20

TC2P

O

LVDS 2st Channel Differential positive data out.

TC2+

TO LCD CONT

E19

TC2M

O

LVDS 2st Channel Differential negative data out.

TC2-

TO LCD CONT

C20

TB2P

O

LVDS 2st Channel Differential positive data out.

TB2+

TO LCD CONT

C19

TB2M

O

LVDS 2st Channel Differential negative data out.

TB2-

TO LCD CONT

A20

TA2P

O

LVDS 2st Channel Differential positive data out.

TA2+

TO LCD CONT

B20

TA2M

O

LVDS 2st Channel Differential negative data out.

TA2-

TO LCD CONT

HDMI Interface Ball Assignments.

L4

L4

PVCC

—

TMDS PLL supply voltage.

+3.3V

M5

ANTSTO

O

Test pin. (no connected)

open

M4, N4, N5, P4

AVCC

—

TMDS analog supply voltage.

+3.3V

L2

RXC-

I

TMDS differential CLK-.

TMDS_CLKN

FROM HDMI

L1

RXC+

I

TMDS differential CLK+.

TMDS_CLKP

FROM HDMI

L3, M3, N3, P3,

R1

R1

TMDS_GND

—

TMDS GND.

M2

RX0-

I

HDMI Differential input pair 0-

TMDS_D0N

FROM HDMI

M1

RX0+

I

HDMI Differential input pair 0+

TMDS_D0P

FROM HDMI

N2

RX1-

I

HDMI Differential input pair 1-

TMDS_D1N

FROM HDMI

N1

RX1+

I

HDMI Differential input pair 1+

TMDS_D1P

FROM HDMI

P2

RX2-

I

HDMI Differential input pair 2-

TMDS_D2N

FROM HDMI

P1

RX2+

I

HDMI Differential input pair 2+

TMDS_D2P

FROM HDMI

R5

REGVCC

—

ACR PLL Regulator supply voltage.

P5

DGND

—

ACR PLL GND.

T10

PWR5V

I

TMDS port Transmitter Detect (5V tolerant).

DDC5VOR_A

FROM HDMI

T11

DSCL

I/O

DDC I2C clock for DDC (5V tolerant).

SCL_SINK

U11

DSDA

I/O

DDC I2C data for DDC (5V tolerant).

SDA_SINK

U12

WS

O

I2S Word select output.

R-+B

V11

SCDT

O

Indicates Active video at HDMI input port.

R-GND

V12

SD0

O

I2S serial data output.

R-+B

W11

AUDIOCLK

I

Audio master clock input reference.

R-GND

W12

SPDIF

O

S/PDIF audio output.

HDMI_SPDIF

TO CODEC

Y11

SCK

O

I2S serial clock output.

R-+B

Pin Assignments for Reference Voltage.

V5

V5

VREFN1

—

ADC1 voltage reference-.

C-GND

W5

VREFP1

—

ADC1 voltage reference+.

C-GND

V7

VREFN2

—

ADC2 voltage reference-.

C-GND

W7

VREFP2

—

ADC2 voltage reference+.

C-GND

Pin No.

Pin Name

I/O

Pin Function

Sheet Name

Destination

Click on the first or last page to see other LC-46X8E service manuals if exist.