Sharp ER-A450 (serv.man2) Service Manual ▷ View online

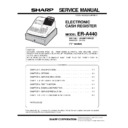

2) Block diagram

Fig. 2-4

MTD

MTD

RJMTR

SLMTD

SLMTS

SLMTR

SLMTD

TXDI

SCKI

RXDI

HTS1

SCK1

STH1

HTS2

SCK2

STH2

ROS1

ROS2

RAS1

RAS2

RAS3

OPTCS

AS

RD

WR

RDO

WRO

Φ

RESET

RES

VRESC

POFF

MD0

MD1

MD1

WAIT

RJRST

SLRST

*PRST

RJTMG

SLTMG

PTMG

INT4

INT1

INT2

INT3

EXINT0

EXINT1

EXINT2

EXINT3

SD

T1

~7

T1

~7

DT

1

1

~

9

TEST

IRQ0

A23~A0

SSPRQ

SL

F

F

SL

R

R

S

VF

RF

JF

F

CUT

PC

U

U

T

STAM

P

TR

G

G

I

TR

G

G

TR

G

G

DO

T

T

E

N

IRLON

D0~D7

Φ

Address decode

External CS

Internal CS

Internal CS

RASEL

Image

control

Image

control

SSP comparison register

BAR.

Buffer

Read/write

control

control

Divider

CHS

serial select

serial select

Multiplexer

WAIT

control

control

CAPS

select

select

Print gate

Print pulse control

Print mode PMD

INTO

control

control

Printer control port

Motor

drive

drive

* Output selection with CAPS.

PRST/PTMG.

PRST/PTMG.

EXWAIT

I/R Control

IRTX

IRRX

RCI

ASKRX

4 – 6

3) Pin description

Pin

No.

Signal

name

In/

Out

Function

1

RF

Out

Receipt side paper feed solenoid

2

JF

Out

Journal side paper feed solenoid

3

PCUT

Out

Printer partial cut signal (NU)

4

FCUT

Out

Printer auto cut signal (NU)

5

VF

Out

Multi line validation paper feed (NU)

6

STAMP

Out

Printer stamp signal (NU)

7

SLFS

Out

Slip printer paper feed singnal (NU)

8

SLRS

Out

Slip printer release signal (NU)

9

SLMTD

Out

Slip printer motor drive signal (NU)

10

RES

Out

Peripheral output reset

11

TRG

Out

Dot head trigger signal (NU)

12

TRG

Out

Dot head trigger signal

13

POFF

In

Power off signal input

14

INT1

In

(NU)

15

HTS1

Out

8 bit serial port output (for CKDC8)

16

SCK1

Out

Serial port shift clock output (for CKDC8)

17

STH1

In

8 bit serial port input (for CKDC8)

18

RAS VZ

—

Chip select (NU)

19

—

—

Nu

20

VCC

—

+5V

21

GND

—

GND

22

INTMCR

—

Interrupt (NU)

23

Out

Turns active when reset and power down

is met

is met

24

SLTMG

In

Slip printer timing signal (NU)

25

SLRST

In

Slip printer reset signal (NU)

26

AS

In

Address strobe

27

RD

In

Read strobe

28

WR

In

Write strobe

29

φ

In

(

φ

) System clock (7.3728 MHz)

30

Out

Slip printer printhead drive signal (dot7)

(NU)

(NU)

31

Out

Slip printer printhead drive signal (dot6)

(NU)

(NU)

32

Out

Slip printer printhead drive signal (dot5)

(NU)

(NU)

33

GND

—

GND

34

Out

Slip printer printhead drive signal (dot4)

(NU)

(NU)

35

Out

Slip printer printhead drive signal (dot3)

(NU)

(NU)

36

Out

Slip printer printhead drive signal (dot2)

(NU)

(NU)

37

Out

Slip printer printhead drive signal (dot1)

(NU)

(NU)

38

D0

I/O

Data bus 0

39

D1

I/O

Data bus 1

40

D2

I/O

Data bus 2

41

D3

I/O

Data bus 3

42

GND

—

GND

43

D4

I/O

Data bus 4

44

D5

I/O

Data bus 5

45

D6

I/O

Data bus 6

46

D7

I/O

Data bus 7

47

SPRQ

Out

SSP interrupt request to CPU

48

RESET

In

MPCA reset

49

SHEN

In

Shift enable from CKDC8

Pin

No.

Signal

name

In/

Out

Function

50

INT3

In

Interrupt signal (Nu)

51

RXD2

Out

8 bit serial port output to CPU

52

TXD2

In

8 bit serial port input from CPU

53

SCK2

In

Serial port shift clock input from CPU.

54

IRQ0

Out

Interrupt request to CPU

55

A0

In

Address bus 0

56

A1

In

Address bus 1

57

A2

In

Address bus 2

58

A3

In

Address bus 3

59

A4

In

Address bus 4

60

A5

In

Address bus 5

61

GND

—

GND

62

VCC

—

+5V

63

A6

In

Address bus 6

64

A7

In

Address bus 7

65

A8

In

Address bus 8

66

A9

In

Address bus 9

67

A10

In

Address bus 10

68

A11

In

Address bus 11

69

A12

In

Address bus 12

70

A13

In

Address bus 13

71

A14

In

Address bus 14

72

A15

In

Address bus 15

73

A16

In

Address bus 16

74

A17

In

Address bus 17

75

A18

In

Address bus 18

76

A19

In

Address bus 19

77

A20

In

Address bus 20

78

A21

In

Address bus 21

79

A22

In

Address bus 22

80

LCDC

—

LCD CS (NU)

81

A23

In

Address bus 23

82

TRGI

In

Dot pulse control/drive signal

83

PTMG

Out

Printer timing signal

84

PRST

Out

Printer reset signal

85

RDY

In

Ready from FMC unit

86

IPLON

In

To option connector (NU)

87

MD1

In

Mode select input (+5V)

88

MD0

In

Mode select input (GND)

89

TEST

In

+5V

90

MA15

—

Image address 15 (NU)

91

MA18

—

Nu

92

MA19

—

Nu

93

RCVRDY1

—

Nu

94

RCVRDY2

—

Nu

95

RC0

—

Remote control encord signal for CPU

96

IRTX

—

I/R output for LED (NU)

97

UASCK

—

I/R serial data shift clock (NU)

98

UARX

—

I/R serial data for CPU (NU)

99

UATX

—

I/R serial data from CPU (NU)

100

VCC

—

+5V

101

GND

—

GND

102

IRRX

—

I/R input from I/R unit (NU)

103

RCI

—

I/R input from I/R unit (NU)

104

DAX1

—

System clock (7.3728MHz)

4 – 7

Pin

No.

Signal

name

In/

Out

Function

105

DAX2

—

Nu

106

MCR1

—

Nu

107

MCR2

—

Nu

108

WAIT

Out

Wait request signal

109

EXWAIT

In

External wait control input signal

110

RA18

Out

Nu

111

RA17

Out

Nu

112

GND

—

GND

113

RA16

Out

Nu

114

RA15

Out

Nu

115

RDO

Out

Expansion RD signal

Option

116

WRO

Out

Expansion WR signal

117

EXINT3

In

Expansion interruption signal 3

Option

118

EXINT2

In

Expansion interruption signal 2

119

EXINT1

In

Expansion interruption signal 1

120

EXINT0

In

Expansion interruption signal 0

121

Out

Chip select base signal for expansion

option

option

122

ROS1

Out

ROM 1 chip select signal

123

ROS2

Out

ROM 2 chip select signal (NU)

124

RAS2

Out

RAM 2 chip select signal

125

RAS1

Out

RAM 1 ship select signal

126

RJRST

In

Printer reset signal

127

RJTMG

In

Printer timing signal

128

DT4

Out

Printer dot signal 4

129

DT3

Out

Printer dot signal 3

130

DT2

Out

Printer dot signal 2

131

DT1

Out

Printer dot signal 1

132

GND

—

GND

133

DT7

Out

Printer dot signal 7

134

DT6

Out

Printer dot signal 6

135

DT5

Out

Printer dot signal 5

136

MTD

Out

Printer motor drive signal

137

MTD

Out

Printer motor drive signal

138

DOT9

Out

Printer dot signal 9 (NU)

139

DOT8

Out

Printer dot signal 8 (NU)

140

SYNC

—

Nu (+5V)

141

ASKRX

—

I/R input from I/R unit (NU)

142

VCC

—

+5V

143

GND

—

GND

144

—

—

Nu

145

RAS3

Out

146

RJMTR

In

Printer motor lock detection signal (NU)

147

SLMTD

In

Nu

148

SLMTS

In

Nu

149

SLMTR

In

GND

150

HTS2

Out

Serial output to FMC unit (NU)

151

SCK2

Out

Serial clock to FMC unit (NU)

152

STH2

In

Serial input to FMC unit (NU) pull-up

153

—

—

Nu

154

—

—

Nu

155

—

—

Nu

156

—

—

Nu

157

—

—

Nu

158

LCDWT

—

Nu

159

DOTEN

Out

Dot drive enable signal

160

RASP

—

Nu

2-3. CKDC8

1) Pin configulation

2) Pin assignment (CKDC8)

Pin

No.

SYMBOL

SIGNAL

NAME

IN/

OUT

FUNCTION

1

DP

DP

OUT DISPLAY SEGMENT Dp

2

A

SA

OUT DISPLAY SEGMENT a

3

B

SB

OUT DISPLAY SEGMENT b

4

C

SC

OUT DISPLAY SEGMENT c

5

D

SD

OUT DISPLAY SEGMENT d

6

E

SE

OUT DISPLAY SEGMENT e

7

F

SF

OUT DISPLAY SEGMENT f

8

G

SG

OUT DISPLAY SEGMENT g

9

VSS0

GND

GND

10

VDD0

VDD

VDD

11

KR4

KR4

IN

KEY RETURN 4

12

KR10

KR10

IN

KEY RETURN (feed clerk

MRS sw)

MRS sw)

13

KR11

KR11

IN

KEY RETURN (MODE sw)

14

KR8

NU

IN

GND

15

HTS

HTS

IN

16

STH

STH

OUT

17

/SCK

/SCK

IN

SHIFT CLOCK

18

ST0

ST0

OUT KEY STROBE 0

19

ST1

ST1

OUT KEY STROBE 1

20

ST2

ST2

OUT KEY STROBE 2

21

ST3

ST3

OUT KEY STROBE 3

22

ST4

ST4

OUT KEY STROBE 4

23

ST5

ST5

OUT KEY STROBE 5

24

VDD1

VDD

VDD

25

AXSS

GND

GND

26

KR9

NU

GND

27

KR0

KR0

IN

KEY RETURN 0

28

KR1

KR1

IN

KEY RETURN 1

29

KR2

KR2

IN

KEY RETURN 2

30

KR3

KR3

IN

KEY RETURN 3

31

KR5

KR5

IN

KEY RETURN 5

32

KR6

KR6

IN

KEY RETURN 6

NU

NU

G10

G9

G8

G7

G6

G5

G4

G3

G2

G1

BUZ

/POFF

NU

ST8

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

DP

SA

SB

SB

SC

SD

SD

SE

SF

SG

GND

VDD

KR4

KR10

KR11

KR11

NU

HTS

STH

STH

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

ST7

ST6

/RESETS

/SHEN

ERC

LDRQ

GND

ST6

/RESETS

/SHEN

ERC

LDRQ

GND

GND

/RES0

VDD

GND

KR7

VDD

GND

KR7

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

/SCK

ST0

ST1

ST2

ST3

ST4

ST5

VDD

GN

D

NU

KR0

KR1

KR2

KR3

KR5

KR6

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

CKDC8

4 – 8

Pin

No.

SYMBOL

SIGNAL

NAME

IN/

OUT

FUNCTION

33

KR7

KR7

IN

KEY RETURN 7

34

AVRF

GND

35

AVDD

VDD

36

/RESET

/RES0

IN

37

XT2

38

XT1

39

IC

GND

40

X2

41

X1

42

VSS1

GND

43

LDRQ

LDRQ

IN

LORD REQUEST

44

ERC

ERC

IN

EVENT READ CANCEL

45

SHEN

/SHEN

OUT SHIFT ENABLE

46

/RES1

/RESETS

OUT SYSTEM TO RESET

47

ST6

ST6

OUT KEY STROBE 6

48

ST7

ST7

OUT KEY STROBE 7

49

ST8

ST8

OUT KEY STROBE 8

50

ST9

NU

OUT KEY STROBE 9

51

/POFF

/POFF

IN

POWER OFF

52

BUZ

BUZ

OUT BUZZER

53

T0

G1

OUT DISPLAY DIGIT 1

54

T1

G2

OUT DISPLAY DIGIT 2

55

T2

G3

OUT DISPLAY DIGIT 3

56

T3

G4

OUT DISPLAY DIGIT 4

57

T4

G5

OUT DISPLAY DIGIT 5

58

T5

G6

OUT DISPLAY DIGIT 6

59

T6

G7

OUT DISPLAY DIGIT 7

60

T7

G8

OUT DISPLAY DIGIT 8

61

T8

G9

OUT DISPLAY DIGIT 9

62

T9

G10

OUT DISPLAY DIGIT 10

63

T10

NU

OUT DISPLAY DIGIT 11

64

ID

NU

OUT DISPLAY SEGMENT

3. Clock generator

1) CPU (HD64151010FX)

Fig. 3-1

Basic clock is supplied from a 14.7456MHz ceramic oscillator.

The CPU contains an oscillation circuit from which the basic clock is

internally driven. If the CPU was not operating properly, the signal

does not appear on this line in most cases.

The CPU contains an oscillation circuit from which the basic clock is

internally driven. If the CPU was not operating properly, the signal

does not appear on this line in most cases.

2) CKDC8 oscillation circuit

Fig. 3-2

Two oscillators are connected to the CKDC8.

The main clock X3 generates 4.19MHz which is used during power

on.

When power is turned off, the CKDC8 goes into the standby mode

and the main clock stops.

The sub-clock X2 generates 32.768KHz which is primarily used to

update the internal RTC (real time clock). During the standby mode, it

keeps oscillating to update the clock and monitoring the power recov-

ery.

The main clock X3 generates 4.19MHz which is used during power

on.

When power is turned off, the CKDC8 goes into the standby mode

and the main clock stops.

The sub-clock X2 generates 32.768KHz which is primarily used to

update the internal RTC (real time clock). During the standby mode, it

keeps oscillating to update the clock and monitoring the power recov-

ery.

4. Reset (POFF) circuit

Fig. 4-1

In order to prevent memory loss at a time of power off and power

supply failure of the ECR, the power supply condition is monitored at

all times. When a power failure is met, the CPU suspends the execu-

tion of the current program and immediately executes the power-off

program to save the data in the CPU registers in the external S-RAM

with the signal STOP forced low to prepare for the power-off situation.

The signal STOP is supplied to the CKDC8 as signal RESET to reset

the devices.

supply failure of the ECR, the power supply condition is monitored at

all times. When a power failure is met, the CPU suspends the execu-

tion of the current program and immediately executes the power-off

program to save the data in the CPU registers in the external S-RAM

with the signal STOP forced low to prepare for the power-off situation.

The signal STOP is supplied to the CKDC8 as signal RESET to reset

the devices.

CPU

(HD64151010FX)

99

98

XTAL

EXTAL

14.7456MHz

X1

101

PHAI

37

38

33P

HD404728A91FS

C105

CKDC 8

X2

X3

4.19MHz

4.19MHz

X2

32.768KHz

32.768KHz

2

1

3

41

18P

C106

40

X1

XT2

XT1

R164

330K

330K

+

-

/POFF

3

2

1

4

8

B

IC3A

KIA393F

KIA393F

C3

1000P

1000P

D7

1SS133

C208

1µ 50V

1µ 50V

+

ZD2

MTZ5.1A

MTZ5.1A

R14

9.1KG

9.1KG

R13

15KG

15KG

R10

56K

R11

2.7K

2.7K

R9

2.7K

2.7K

R12

8.2KG

8.2KG

+24V

+5V

POFF

CPU

72

IRQ0

89

RESET (FROM CKDC 8)

STOP (TO CKDC 8)

MPCA7

13

48

1

IR

Q0

54

IN

T0

4 – 9

Click on the first or last page to see other ER-A450 (serv.man2) service manuals if exist.