Panasonic KX-TDE100UA (serv.man2) Service Manual ▷ View online

9

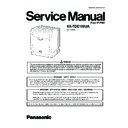

KX-TDE100UA

(1)

(3)

(5)

(7)

(8)

(10)

(12)

(14)

(16)

(12)

(14)

(16)

(18)

(20)

(22)

(23)

(25)

(27)

(28)

(30)

(32)

(33)

(35)

(37)

(39)

(41)

(42)

(43)

(45)

(46)

(46)

(48)

(49)

(51)

(53)

(55)

(56)

(58)

(60)

(62)

(63)

(65)

(66)

(67)

(2)

(4)

(6)

(11)

(13)

(15)

(17)

(13)

(15)

(17)

(19)

(21)

(24)

(26)

(29)

(31)

(34)

(36)

(38)

(40)

(44)

(47)

(50)

(52)

(54)

(57)

(59)

(61)

(64)

(9)

EC_AD[0-15]

EC_PAR

EC_nCBE1

EC_nCBE0

EC_nFRAME

EC_nPERR

EC_nCBE1

EC_nCBE0

EC_nFRAME

EC_nPERR

EC_nSTOP

EC_nTRDY

EC_nTRDY

EC_nINT

EC_CLK

EC_nCDET

RINGER

CT_NETAEF

CT_D[0-7]

DG

+3.3VD

+15V

MASTER/nS

M/nS

POWER_TYPE1

POWER_TYPE0

M/nS

POWER_TYPE1

POWER_TYPE0

+3.3VD

DG

+2.5VD

+3.3VD

+3.3VD_B

+3.3VD_B

RS232_RTS2_CON

RS232_CTS2_CON

RS232_TXD2_CON

RS232_RXD2_CON

RS232_DTR2_CON

RS232_DSR2_CON

+15V

SHELF_FAN_ALM_FPGA

DC_ALM_FPGA

LED_RUN_FPGA_DRIVE

AC_ALM_FPGA

nHALT_FPGA

nFAN_ALM_FPGA

nLOS_FPGA

nBATT_FPGA

RINGER_SYNC_FPGA

LED_ALM_FPGA_DRIVE

CT_D[0]

CT_C8

CT_FRAME

CT_FRAME

nBUSY

EX1_D[15]

CLK_SD_33.33MHz

SD0_nRESET_SOFT

RS232_DCD2_CON

CLK_32.768kHz

RMT_nRESET_SOFT

+15V_CON

+3.3VD_BB

+3.3VD

DG

DG

+3.3VD

EX1_A[1-7]

HWCLK[1]

CLKIO_66.66MHZ

+1.8VD

+1.25VD

+1.2VD

NEXUS_nRESET_SOFT

SHW_FH

SHW_CLK

LUHW[1]

LDHW[1]

CH_SEL[3]

CH_SEL[0]

CH_SEL[1]

MELODYSEL

MOHSEL

CH_SEL[5]

+3.3VD

DG

+15V

VREF_7.5V

Mu/nA

CH_SEL[7]

CH_SEL[6]

LUHW[0]

LDHW[0]

HW_CLK[0]

SVM_DSP_OUT[1]

SVM_DSP_OUT[0]

SVM_DSP_OUT[0]

VOX[0-3]

CH_SEL[4]

HWFH

MEMORY_CARD_PRESNT

RTC_nINT

nBAT_ALM

CL3162

CL3164

CL3144

CL3172

CL3160

CL3180

CL3169

CL3159

DG

CL3173

CL3166

DG

DG

CL3146

TP_DRAM_VREF

CL3182

CL3178

CL3157

CL3171

CL3158

CL3176

CL3167

CL3179

DG

CL3177

CL3175

TP_+1.2VD

CL3168

CL3143

CL3174

CL3170

CL3165

CL3163

CL3181

CL3161

CL3149

CL3148

CL3152

CL3151

CL3145

CL3147

MAIN No.7

+3.3VD

CLK_SD_33.33MHz

DG

EX1_A[1-7]

EX1_D[0-15]

nDR

RS232_nDCD2

RS232_nDSR2

RS232_nDTR2

RS232_RXD2

RS232_TXD2

RS232_nCTS2

RS232_nRTS2

SD0_nINT

SD0_WP

SD0_CD

nCS_SD0

SD0_nRESET_SOFT

nWE0

SD0_DACK

SD0_nDRQ

RS232_RTS2_CON

RS232_TXD2_CON

RS232_RXD2_CON

RS232_CTS2_CON

RS232_DTR2_CON

RS232_DCD2_CON

RS232_DSR2_CON

MCCLK

MCDAT

MCCMD

TP_+1.25VD

TP_+2.5VD

TP_+3.3VD

TP_+3.3VD_B

TP_+15V

DG

CL3150

CL3153

CL3195

CL3194

CL3199

CL3192

CL3196

CL3198

CL3193

CL3191

CL3197

CL3190

CL3185

CL3189

CL3188

CL3186

CL3183

CL3184

CL3184

CL3187

CL3155

CL3154

TP_+15V_CON

TP_+3.3VD_BB

TP_+1.8VD

MAIN No.10

+3.3VD

DG

EC_AD[0-15]

EC_PAR

EC_nCBE0

EC_nCBE1

EC_nRST

EC_nSTOP

EC_nTRDY

EC_nFRAME

EC_nPERR

EC_nINT

EC_nCDET

EC_CLK

+15V_CON

CT_FRAME

CT_NETAEF

CT_C8

RINGER

DC_ALM_FPGA

AC_ALM_FPGA

RS232_RTS2_CON

RS232_TXD2_CON

RS232_RXD2_CON

RS232_CTS2_CON

RS232_DTR2_CON

RS232_DCD2_CON

RS232_DSR2_CON

+3.3VD_BB

SHW_CLK

SHW_FH

CT_D[0-7]

M/nS_FPGA

LDHW[1]

LUHW[1]

nFAN_ALM_FPGA

LED_ALM_FPGA

LED_RUN_FPGA

MASTER/nS_FPGA

nBATT_FPGA

POWER_TYPE1_FPGA

POWER_TYPE0_FPGA

RINGER_SYNC_FPGA

nHALT_FPGA

nLOS_FPGA

SHELF_nFAN_ALM_FPGA

CL3202

CL3201

CL3200

MAIN No.9

+15V

+3.3VD

CH_SEL[0]

DG

HWCLK[0]

LDHW[0]

LUHW[0]

MELODYSEL

MOHSEL

Mu/nA

CH_SEL[1]

VREF_7.5V

DG

CL3204

CL3203

MAIN No.8

+3.3VD

CLK_NEXUS_66MHz

DG

EX2_A[0-21]

EX2_D[0-15]

EX2_nDR

HWCLK[0]

LDHW[0]

LUHW[0]

nBS

NEXUS_nINT

SRAM_nBC1

SRAM_nBC0

SRAM_nWR

nBACK

nBREQ

SRAM_nCS

nCS_NEXUS

nBUSY

nRESET_SOFT

nWE1

nWE0

CH_SEL[0]

MELODYSEL

MOHSEL

Mu/nA

+3.3VD_B

EC_AD[0-15]

EC_PAR

EC_nCBE0

EC_nCBE1

EC_nSTOP

EC_nTRDY

EC_nFRAME

EC_nPERR

EC_nINT

EC_nCDET

EC_CLK

CT_D[0-7]

CT_FRAME

CT_NETAEF

CT_C8

RINGER

nRESET_POWER

LDHW[1]

HWFH

LUHW[1]

CH_SEL[4]

SHW_CLK

SHW_FH

POWER_TYPE0

POWER_TYPE1

M/nS

MASTER/nS

HWCLK[1]

CH_SEL[1]

RMT_nRESET_SOFT

CH_SEL[3]

CH_SEL[5]

CH_SEL[6]

CH_SEL[7]

VOX[0-3]

nCS_SRAM

MEMORY_CARD_PRESNT

EXT_nINT0

CL3207

MAIN No.13

+3.3VD

+3.3VD_B

DG

nRESET_POWER

+15V

+3.3VD_BB

+15V_CON

HARD_nRESET_SW

+1.25VD

+1.2VD

+2.5VD

DRAM_VREF

+1.8VD

nBAT_ALM

MAIN No.4

CLKIO_66.66MHz

CLK_SD_33.33MHz

EX1_D[0-7]

FAN_ALARM_nINT

AC_ALARM_nINT

DC_ALARM_nINT

nRD

nWE1

nWE0

nRDY_CPU

nBUSY_NEXUS

nCS_FPGA

CLK_32.768kHz

nLOS_FPGA

nHALT_FPGA

RINGER_SYNC_FPGA

DC_ALM_FPGA

AC_ALM_FPGA

nBATT_FPGA

LED_RUN_FPGA_DRIVE

LED_ALM_FPGA_DRIVE

nFAN_ALM_FPGA

NEXUS_nRESET_SOFT

PLD_TDI

PLD_TCK

SD0_nRESET_SOFT

PLD_TMS

PLD_TDO

FPGA_INT

RMT_nRESET_SOFT

SHELF_nFAN_ALM_FPGA

EX1_A[0-25]

EX1_A-1

HWFH_NEXUS

LUHW0_NEXUS

LDHW0_NEXUS

HW_CLK0_NEXUS

CPU_nRESET

CT_D[0]

CT_FRAME

CT_C8

nCS_SRAM

nCS_FLASH

PROG_B

CH_SEL[5]

CH_SEL[6]

CH_SEL[7]

SVM_DSP_OUT[0]

SVM_DSP_OUT[1]

RTC_nINT

nBACK

nBAT_ALM

MAIN No.15

+15V

+3.3VD

DG

HWCLK[0]

LDHW[0]

Mu/nA

CH_SEL[6]

CH_SEL[7]

SVM_DSP_OUT[0]

SVM_DSP_OUT[1]

VOX[0-3]

VREF_7.5V

+3.3VD

+3.3VD

+15V

+3.3VD

+3.3VD

+1.25VD

+3.3VD_B

+3.3VD

+1.2VD

+3.3VD

+3.3VD_B

+15V

+2.5VD

+15V

+1.8VD

SD&RS232

NEXUS(+SRAM)

POWER

CODEC

EC_CT CON

FPGA+RTC+SVM

SVM_VOX

KX-TDE100UA IPCMPR CARD DETAILED BLOCK DIAGRAM (2/2)

10

KX-TDE100UA

4.2.

IPCMPR Card Circuit Operation

4.2.1.

IPCMPR Card

4.2.1.1.

Outline

1) Function

• System Control

• Circuit Switching (includes gain adjustment function)

• Conference Call (3 people x 8 ~ 8 people x 3)

• MOH

• PAGING

• Clock

• Circuit Switching (includes gain adjustment function)

• Conference Call (3 people x 8 ~ 8 people x 3)

• MOH

• PAGING

• Clock

2) Configuration

• Power Supply: DC/DC Converter

• CPU: HITACHI SH7788 (400MHz)

• ASIC: Our own products

• ROM: 8Mbit x 1 (for boot programs)

• SDRAM: 512Mbit x 2 (for work area)

• SRAM: 16Mbit x 1 (for user data backup)

• SD card I/F (for operating programs) x 1

• LAN I/F (for PC programming and the VoIP) x 2

• MOH: External sound input x 2

• PAGING: External output x 2

• Expanded memory connector x 1

• Modem card connector x 1

• CPU: HITACHI SH7788 (400MHz)

• ASIC: Our own products

• ROM: 8Mbit x 1 (for boot programs)

• SDRAM: 512Mbit x 2 (for work area)

• SRAM: 16Mbit x 1 (for user data backup)

• SD card I/F (for operating programs) x 1

• LAN I/F (for PC programming and the VoIP) x 2

• MOH: External sound input x 2

• PAGING: External output x 2

• Expanded memory connector x 1

• Modem card connector x 1

3) Operation Rating

• Power Input: +15V_CON

• Power Output: +15V (for MOH)

• Power Output: +15V (for MOH)

+3.3V (for I/O)

+3.3VD_BB (back board signal line pull-up)

+3.3VD_B (for SRAM backup)

+1.25VD (for CPU core)

+2.5VD (for DDR-SDRAM, CPU, LAN SW IC amd FPGA)

+1.8VD (for LAN SW IC)

+1.2VD (for FPGA)

+3.3VD_BB (back board signal line pull-up)

+3.3VD_B (for SRAM backup)

+1.25VD (for CPU core)

+2.5VD (for DDR-SDRAM, CPU, LAN SW IC amd FPGA)

+1.8VD (for LAN SW IC)

+1.2VD (for FPGA)

11

KX-TDE100UA

4.2.2.

Description of Each Part

LED Lamp (BATT ALARM): Turns on to indicate the dropping of the lithium battery voltage (less than 2.8V).

LED Lamp (SD ACCESS): Turns on when the SD card is accessing.

SD card slot: Mounts the system program SD card.

Reset Switch: Press at the system reset.

System Initialize Switch:

On default startup, set the switch to the "SYSTEM INITIALIZE" position for the power ON. Return the switch to the "NORMAL"

position when the main power switch starts to flash. On normal startup, turn the power ON with the "NORMAL" position.

LAN connector: 1, 2. Used for the PC programming and the VoIP.

PAGING 1, 2: External PAGING output. Connect to the device with the built-in amplifier.

MOH 1, 2: External music on-hold input.

LED Lamp (LINK / ACT) Turns on: LINK OK. Blinking: ACTive data is communicated.

LED Lamp (100 / 10) Turns on: 100BASE-TX. Turns off: 10BASE-T.

LED Lamp (SD ACCESS): Turns on when the SD card is accessing.

SD card slot: Mounts the system program SD card.

Reset Switch: Press at the system reset.

System Initialize Switch:

On default startup, set the switch to the "SYSTEM INITIALIZE" position for the power ON. Return the switch to the "NORMAL"

position when the main power switch starts to flash. On normal startup, turn the power ON with the "NORMAL" position.

LAN connector: 1, 2. Used for the PC programming and the VoIP.

PAGING 1, 2: External PAGING output. Connect to the device with the built-in amplifier.

MOH 1, 2: External music on-hold input.

LED Lamp (LINK / ACT) Turns on: LINK OK. Blinking: ACTive data is communicated.

LED Lamp (100 / 10) Turns on: 100BASE-TX. Turns off: 10BASE-T.

12

KX-TDE100UA

4.2.3.

Circuit Description

4.2.3.1.

Outline of Block Description

• CPU2 block (BLOCK1)

This block operates the main unit control. Besides this operates various controls, select signal generation, DMA control and

serial port control. This contains the built-in clock function.

Configuration: IC101 (CPU), IC102 (clock buffer for PCI), and so on.

Function:

(IC101) Generates the select signal in accordance with the memory map and operates Readout/Storage of data between each

peripheral.

Controls the DMA transfer between built-in serial controller and memory.

Operates input/output control of each I/O signal in accordance with the program.

serial port control. This contains the built-in clock function.

Configuration: IC101 (CPU), IC102 (clock buffer for PCI), and so on.

Function:

(IC101) Generates the select signal in accordance with the memory map and operates Readout/Storage of data between each

peripheral.

Controls the DMA transfer between built-in serial controller and memory.

Operates input/output control of each I/O signal in accordance with the program.

• CPU_POWER block (BLOCK2)

This block is a power supply part of CPU.

Configuration: IC101 (CPU), X501 (33.33MHz clock for CPU), and so on.

Function:

Power pins of CPU.(+3.3VD,+2.5VD,+1.25VD)

Clock oscillation circuit for CPU operation.

Configuration: IC101 (CPU), X501 (33.33MHz clock for CPU), and so on.

Function:

Power pins of CPU.(+3.3VD,+2.5VD,+1.25VD)

Clock oscillation circuit for CPU operation.

• MEMORY2 block (BLOCK3)

This is a work area and the main unit control program storage or the system boot program storage area.

Configuration: IC602 (Flash ROM), IC601, IC603 (DDR-SDRAM), CN601 (IPCMEC card connector) and so on.

Function:

(IC602) Saves (some of) the system boot program and the system data.

(IC601, IC603) The main program is loaded from the SD card on the system start-up.

Used as the program area and the CPU work area after start-up.

It is independent bus connection to CPU due to high-speed action (bus clock 166MHz).

Configuration: IC602 (Flash ROM), IC601, IC603 (DDR-SDRAM), CN601 (IPCMEC card connector) and so on.

Function:

(IC602) Saves (some of) the system boot program and the system data.

(IC601, IC603) The main program is loaded from the SD card on the system start-up.

Used as the program area and the CPU work area after start-up.

It is independent bus connection to CPU due to high-speed action (bus clock 166MHz).

• FPGA + RTC + SVM block (BLOCK 4)

The FPGA is a CPU Peripheral function IC.

Configuration: IC801 (FPGA), IC802 (RTC, 32.768kHz clock for CPU), IC804 ( SVM DSP ), IC805 ( SVM voice data FLASH )

and so on.

Function:

(IC801) has the functions of RTC I/F, LAN SW I/F(SPI I/F), reset control port, LED driver and address decoder and so on.

(IC802)This is working in the Real time clock function when system stops.

This IC is maintained by the onboard battery back-up.

(IC804,IC805) These are the simple voice mail function.

Configuration: IC801 (FPGA), IC802 (RTC, 32.768kHz clock for CPU), IC804 ( SVM DSP ), IC805 ( SVM voice data FLASH )

and so on.

Function:

(IC801) has the functions of RTC I/F, LAN SW I/F(SPI I/F), reset control port, LED driver and address decoder and so on.

(IC802)This is working in the Real time clock function when system stops.

This IC is maintained by the onboard battery back-up.

(IC804,IC805) These are the simple voice mail function.

• LAN block (BLOCK 5)

It is LAN controller connected with PCI.

Configuration: IC1002 (MAC+PHY (LAN controller)), X1001 ( 25MHz clock for LAN controller) and so on.

Function:

(IC1002) This is a function to communicate LAN through LAN SW.

Configuration: IC1002 (MAC+PHY (LAN controller)), X1001 ( 25MHz clock for LAN controller) and so on.

Function:

(IC1002) This is a function to communicate LAN through LAN SW.

• LAN_SW_5P block (BLOCK 6)

5ports LAN SW and the external I/F LAN connector.

Configuration: IC1101 (LAN SW), JK1102, JK1103 (LAN connector) and so on.

Function:

(IC1101) It is a hub that does LAN signal of two internal ports and two external ports in the switching.

(JK1102, JK1103) These are connectors with built-in LAN transformer and LED.

Configuration: IC1101 (LAN SW), JK1102, JK1103 (LAN connector) and so on.

Function:

(IC1101) It is a hub that does LAN signal of two internal ports and two external ports in the switching.

(JK1102, JK1103) These are connectors with built-in LAN transformer and LED.

• SD and RS232 block (BLOCK 7)

SD card I/F and RS232 (serial) I/F

Configuration: IC1201 (SD card controller), CN1201 (SD card connector) , IC1202 (RS232 D/R)and so on.

Function:

(IC1201) This provides the SD card I/F function and loads the main unit program and the system data from the SD card storing

the main unit control program.

(IC1202). This provides the serial I/F driver / receiver function.

Configuration: IC1201 (SD card controller), CN1201 (SD card connector) , IC1202 (RS232 D/R)and so on.

Function:

(IC1201) This provides the SD card I/F function and loads the main unit program and the system data from the SD card storing

the main unit control program.

(IC1202). This provides the serial I/F driver / receiver function.

Click on the first or last page to see other KX-TDE100UA (serv.man2) service manuals if exist.