Panasonic KX-TDA6110XJ / KX-TDA6110X Service Manual ▷ View online

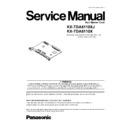

6 BLOCK DIAGRAM

BUS-S#3

[Circlink chip]

TMC20073

CT- BUS

Switch

ZL50031

BUS-S#2

[Circlink chip]

TMC20073

E

xp

a

n

sion B

a

c

kb

o

a

rd

c

o

nnec

to

r

Ba

c

c

k Bo

a

a

rd

C

o

o

n

n

e

c

to

r

LVDS

Transceiver

LVDS

Driver

Driver

In

te

r s

hel

f c

onnec

hel

f c

onnec

to

r

#

3

In

te

r s

h

h

el

f c

onnec

onnec

to

r

#

2

LVDS

Receiver

LVDS

Transceiver

LVDS

Driver

Driver

LVDS

Receiver

SHW_CLK

BMCTL

SHW_CLK

SHW_CLK

LSTo[9:11]

LSTo[6:8]

LSTi[9:11]

LSTi[6:8]

LSTo[9:11]

LSTo[6:8]

LSTi[9:11]

LSTi[6:8]

S3_NETREF

S1_NETREF

S2_NETREF

S2_NETREF

nLOS1

RINGERSYNC

RINGERSYNC

RINGERSYNC

nMRESET3

nLOS2

nLOS3

nLOS2

nINTR1

BM_nIRQ

nDIAG1,nCMIBYP1

nMRESET3

nMRESET2

nINTR3

nINTR2

nDIAG2,nCMIBYP2

nSLF1_PRS

nSLF2_PRS

nSLF2_PRS

+15V

DC/ DC

Conv.

+3.3V

nSLF3_PRS

nSLF2_PRS

nEC_RST

nEC_RST

LED/Green

ES1Status/Green

[FPGA]

BUS-M internal bus

EMPR Control Signal

BUS

nEC_RST

nEC_RST

ESLID3[1:0]

ESLID2[1:0]

" 00"

" 01"

BM_nPRS

CT_NETREF

CT_D[7:0]

CT_C8,

CT_FRAME

S2_NETREF

CT_NETREF

LSTo[0:2]

LSTi[0:2]

In

te

r s

h

h

el

f c

o

o

nnec

to

r

#

1

LVDS

Transceiver

LVDS

Driver

Driver

LVDS

Receiver

LSTo[3:5]

LSTi[3:5]

RINGERSYNC

nLOS1

nMRESET1

nSLF1_PRS

ESLID1[1:0]

" 10"

S3_NETREF

BUS-S#1

[Circlink chip]

TMC20073

nINTR3

nDIAG3,nCMIBYP3

nEC_RST

LSTo[3:5]

LSTi[3:5]

nMRESET1

nMRESET2

nMRESET2

nSLF3_PRS

nLOS3

nINTR2

S3_NETREF

nDIAG3,nCMIBYP3

nDIAG2,nCMIBYP2

nDIAG1,nCMIBYP1

LED control

BSOP1[1:0]

BSOP2[1:0]

BSOP3[1:0]

* Dashed functions are

mounted

on BUS-ME (KX-TDA6111)

2.5V

1.2V

Regulator

+1.2V

+2.5V

Serial

PROM

EMPR

data bus

address bus

SHW_FH

SHW_FH

SHW_FH

SHW_CLK

SHW_FH

40MHz

X'tal

40MHz

X'tal

DIV(1/ 2)

System Clock (20MHz)

40MHz

X'tal

BM_nRST

+2.5V

+3.3V

+3.3V

+2.5V

+3.3V

+3.3V

+1.2V

LED/Red

ES2Status/Green

ES2Status/Green

KX-TDA6110XJ/KX-TDA6110X BUS-M BLOCK DIAGRAM

IC614

IC101

IC612

IC605

IC604

IC311

IC312

IC313

IC313

IC314

IC315

IC315

IC301

Regulator

16MHz

X'tal

BSOP1[1:0]

BSOP2[1:0]

BSOP3[1:0]

13

KX-TDA6110XJ / KX-TDA6110X

6.1. BLOCK DISCRIPTION

The BUS-M card consists of the interface with the EMPR, the BMCTL (FPGA) comprising a control circuit within the card, the

CTSW (system TSW) exchanging the PCM highway interface of the basic shelf backboard and the PCM highways of the expansion

shelves, the CircLink (communication controller) realizing the control message communication between the basic shelf and expsion

shelves, the connectors connecting the shelf-to-shelf communication cables, and the differential receiver (LVDS standard)

comprising the differential communication channels.

BMCTL Block

CTSW (system TSW) exchanging the PCM highway interface of the basic shelf backboard and the PCM highways of the expansion

shelves, the CircLink (communication controller) realizing the control message communication between the basic shelf and expsion

shelves, the connectors connecting the shelf-to-shelf communication cables, and the differential receiver (LVDS standard)

comprising the differential communication channels.

BMCTL Block

The BMCTL has a glue logic function to connect the expansion bus of the EMPR card and the internal control bus of the BUS-

M card and a function to terminate and relay the control signals connected to the control register in the BUS-M card and the

expansion shelves.

M card and a function to terminate and relay the control signals connected to the control register in the BUS-M card and the

expansion shelves.

The main functions of the BMCTL are as follows.

1. Termination of the triggers such as CircLink interruption (nINTRRCL1, nINTRCL2, nINTRCL3), cable insert detection

interruption (SSSTAT1, SSSTAT2, SSSTAT3) and line out of sync detection interruption (nLOS1, nLOS2, nLOS3) within the

BUS-M card, and generation of the BUS-M interruption signal (BM_nIRQ) for the EMPR card.

BUS-M card, and generation of the BUS-M interruption signal (BM_nIRQ) for the EMPR card.

2. Generation of reset signal (nMRESET1, nMRESET2,nMRESET3) according to each expansion shelf.

3. Selection of line synchronizing signal (S1_NETREF,S2_NETREF, S3_NETREF) input from expansion shelf and drive of line

3. Selection of line synchronizing signal (S1_NETREF,S2_NETREF, S3_NETREF) input from expansion shelf and drive of line

synchronizing signal line (CT_NETTREF) on basic shelf backboard.

4. Control of maintenance function signal (nCMIBYP3, nDIAG1, nCMIBYP1, nDIAG2, nCMIBYP2, and nDIAG3) control to

CircLink # 1(IC301), # 2, and # 3.

5. Control of output pin enable signal (ODEZL) of CT-BUS switch (IC101).

6. Control of status LED control signal (LED_RED,LED_GR) and link LED control signal (ES1S_LED, ES2S_LED, and

6. Control of status LED control signal (LED_RED,LED_GR) and link LED control signal (ES1S_LED, ES2S_LED, and

ES3S_LED).

7. Register display of extended shelf status display signal (BSOP1,BSOP2,BSOP3).

8. Generation of address decode to CircLink # 1 (IC301), #2, and #3 and chipselect (nCSCL1, nCSCL2, nCSCL3).

9. Generation of address decode to CT-BUS switch (IC101) and chipselect (nCSZL).

CT-BUS switch

8. Generation of address decode to CircLink # 1 (IC301), #2, and #3 and chipselect (nCSCL1, nCSCL2, nCSCL3).

9. Generation of address decode to CT-BUS switch (IC101) and chipselect (nCSZL).

CT-BUS switch

The CTSW has the following functions; 1) to exchange 1536ch of PCM highways in total which consists of 384ch of the

PCM highways on the basic shelf backboard and 1152ch to be connected to three expansion shelves (384ch for each shelf),

2) to generate the PCM highway clock and frame synchronization signal which are distributed among the expansion shelves.

PCM highways on the basic shelf backboard and 1152ch to be connected to three expansion shelves (384ch for each shelf),

2) to generate the PCM highway clock and frame synchronization signal which are distributed among the expansion shelves.

Communication Controller block

The CircLink is a communication controller to realize control message communication between the basic shelf and

expansion shelves. The CircLink chips on expansion shelves and the CircLink chips on the BUS-M card are connected one-

on-one basis. But the CircLink chip initially mounted on the BUS-M card only corresponds to the extended port #1, so the

CircLink chips corresponding to the extended ports #2 and #3 should be added by mounting BUS-ME cards (KX-TDA6111).

expansion shelves. The CircLink chips on expansion shelves and the CircLink chips on the BUS-M card are connected one-

on-one basis. But the CircLink chip initially mounted on the BUS-M card only corresponds to the extended port #1, so the

CircLink chips corresponding to the extended ports #2 and #3 should be added by mounting BUS-ME cards (KX-TDA6111).

Shelf Interface block

The shelves are connected with 20 pairs of twisted pair cables. Three ports of 40 pin half pitch connectors for cable

connections and an LVDS interface ship as a driver receiver of board-to-board signal are mounted on the board.

But the LVDS device initially mounted on the BUS-M card only corresponds to the extended port #1, so the LVDS devices

corresponding to the extended ports #2 and #3 should be added by mounting BUS-ME cards (KX-TDA6111).

connections and an LVDS interface ship as a driver receiver of board-to-board signal are mounted on the board.

But the LVDS device initially mounted on the BUS-M card only corresponds to the extended port #1, so the LVDS devices

corresponding to the extended ports #2 and #3 should be added by mounting BUS-ME cards (KX-TDA6111).

Power block

The BUS-M card uses three types of power supplies; +3.3 V, +2.5 V and +1.2 V. Since a power supply of +15 V is supplied

from the backboard, the power block consists of three types of devices; a DC/DC converter converting +15 V into +3.3 V and

series regulators converting +3.3 V into +2.5 V and +3.3 V into +1.2 V.

from the backboard, the power block consists of three types of devices; a DC/DC converter converting +15 V into +3.3 V and

series regulators converting +3.3 V into +2.5 V and +3.3 V into +1.2 V.

Others

- Mount two 120 pin board-to-board connectors on the board for mounting 2 ports of the BUS-ME cards.

- Since the BMCTL is implemented by SRAM-type FPGA (IG614), it is necessary to read the configuration data during start-

up. The configuration data is stored in a serial PROM (IC210). The reading of the configuration data occurs when power is

on and the EC_nRST signal is asserted. Since the status of the internal register is random just after the completion of

configuration, it requires logical reset by the EC_nRST.

- Since the BMCTL is implemented by SRAM-type FPGA (IG614), it is necessary to read the configuration data during start-

up. The configuration data is stored in a serial PROM (IC210). The reading of the configuration data occurs when power is

on and the EC_nRST signal is asserted. Since the status of the internal register is random just after the completion of

configuration, it requires logical reset by the EC_nRST.

14

KX-TDA6110XJ / KX-TDA6110X

6.2. DESCRIPTION OF THE SIGNAL OF BUS-M

Signal Name

Function

BM_nPRS

Signal informing the EMPR card that the BUS-M card is inserted

BM_DATA[15:0]

Data path extended from EMPR card

BM_AD[25:0]

Address bus extended from EMPR card

BM_nRST

BUS-M card logic reset signal controlled by EMPR card

BM_nIRQ

BUS-M card interrupt signal to be notified to EMPR card

BM_nCS

Chip select signal to BUS-M card extended from EMPR card

BM_nRDY

Ready signal extended from EMPR card

BM_WE[1:0]

Write signal extended from EMPR card

BM_RDnWR

Bus direction control signal extended from the EMPR card

MnWRD

NWrite/Read signal from EMPR Card (Local control signal in BUS-M card)

MnWE0

Write enable low byte signal from EMPR Card (Local control signal in BUS-M card)

MnWE1

Write enable low byte signal from EMPR Card (Local control signal in BUS-M card)

MnRD

Read signal from EMPR Card (Local control signal in BUS-M card)

MnRDY

Ready signal to EMPR Card (Local control signal in BUS-M card)

MnCS

Chip select signal from EMPR Card (Local control signal in BUS-M card)

MnIRQ

Interrupt signal to EMPR Card (Local control signal in BUS-M card)

LD[15:0]

Local data bus in BUS-M card

LA[25:22] LA[14:0]

Local address bus in BUS-M card

nDETCL3

BUS-ME Card #3 detection

nCMI3B

CircLink #3 CMI Modem control signal

nMRESET3

Expansion shelf #3 Reset signal

SSTAT3

Expansion shelf #3 BUS cable presence detection bit

nCSCL3

Chip select signal for CircLink #3 on BUS-ME card

S3_NETREF

Network reference clock from Exoansion shelf #3

nDIAG3

Diagnosis function contorl signal for CircLink #3

nINTRCL3

Interrupt signal from CircLink #3 on BUS-ME card

BS32, BS31

Expansion shelf #3 BUS-S card Status signal 2

nLOS3

Loss of sync signal from Expnsion shelf #3

nDETCL2

BUS-ME Card #2 detection

nCMI2B

CircLink #2 CMI Modem control signal

nMRESET2

Expansion shelf #2 Reset signal

SSSTAT2

Expansion shelf #2 BUS cable detection port

nCSCL2

Chip select signal for CircLink #2 on BUS-ME card

S2_NETREF

Network reference clock from Exoansion shelf #2

nDIAG2

Diagnosis function contorl signal for CircLink #2 on BUS-ME Card

nINTRCL2

Interupt singnal from CircLink #2

BS22, BS21

Expansion shelf #2 BUS-S card Status signal 2

nLOS2

Loss of sync signal from Expnsion shelf #2

nCMI1B

CircLinkk #1 CMI Modem control signal

nMRESET1

Expansion shelf #1 Reset signal

SSSTAT1

Expansion shelf #1 BUS cable detection port

nCSCL1

Chip select signal for CircLink #1 on BUS-ME card

S1_NETREF

Network reference clock from Expansion shelf #1

nDIAG1

Diagnosis function contorl signal for CircLink #1

nINTRCL1

Interupt singnal from CircLink #1

BS12, BS11

Expansion shelf #1 BUS-S card Status signal 2

nLOS1

Loss of sync signal from Expansion shelf #1

nWRZL

nWrite/Read signal for CTSW

nDTAZL

Data acknowledge signal for CTSW

nDSZL

Data strobe signal for CTSW

nCSZL

Chip strobe signal for CTSW

ODEZL

Output port enable signal for CTSW

C16M

Global Clock Buffer Input (16MHz)

nRDCL

Read signal for CircLink #1 #2 #3

nWECL

Write signal for CircLink #1 #2 #3

CRDID0-7

Card ID port [0-7]

LED_RED

Status LED control port (RED)

LED_GR

Status LED control port (GREEN)

ES1S_LED

LINK LED #1 control port

ES2S_LED

LINK LED #2 control port

ES3S_LED

LINK LED #3 control port

NRST

System reset input port from EMPR Card

DONE

Configuration Done Delay Start-up Sequence

COLK

Configuration Clock

TDO

JTAG Test Data output

15

KX-TDA6110XJ / KX-TDA6110X

Signal Name

Function

TCK

JTAG Test Clock

TMS

JTAG Test Mode Select

TDI

JTAG Test Data input

HSWAP_EN

Disable Weak Pull-up Resistors During Configuration

PROG_B

Program/Configure Device

EC_nRST

EC bus reset signal

CT_D[0-7]

Voice bus on backboard

CT_NETREF

Network reference timing signal on the backboard

16

KX-TDA6110XJ / KX-TDA6110X

Click on the first or last page to see other KX-TDA6110XJ / KX-TDA6110X service manuals if exist.