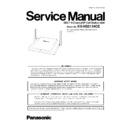

Panasonic KX-NS0154CE (serv.man2) Service Manual ▷ View online

41

KX-NS0154CE

L4

MEMXD2_LCDD4

Not used

O

L5

VDDIO_RGMII

RGMII I/O

PI

L6

VDDIO

General I/O

PI

L7

GND

GND Connection

P

L8

GND

GND Connection

P

L9

GND

GND Connection

P

L10

GND

GND Connection

P

L11

GND

GND Connection

P

L12

GND

GND Connection

P

L13

PLL3_AVDD

PLL3 Analog

PI

L14

IF_EN_AD

TDM-DTX for IC503

O

L15

IF_DATA_AD

TDM-SCLK for IC503

I

L16

IF_CLK_IF

RFAPU/APU Interface Clock out (Not used)

O

L17

AMPOUT2

Output of Out Amplifier 2 (Not used)

O

L18

AMPOUT3

Output of Out Amplifier 3 (Not used)

O

L19

DIFFIN1P

Positive Input In Amplifier 0 (Not used)

I

M1

MEMXD1_LCDD3

Not used

O

M2

MEMXD4_LCDD6

Not used

O

M3

MEMXD15_LCDD21

not used

O

M4

MEMXD0_LCDD2

Reset SW detect

I

M5

VCC_USB2

USB2 I/O power supply

PI

M6

VDDL_USB1

USB1 1.2 V

PI

M7

OSC12M_VSS

Oscillator 12 MHz GND

P

M8

VDD

1.2 V Core

PI

M9

GND

GND Connection

P

M10

VDD

1.2 V Core

PI

M11

GND

GND Connection

P

M12

GND

GND Connection

P

M13

VDDIO_APU

DAIF I/O Voltage 1.8 V

PO

M14

VDDIO_RFAPU

RFAPU I/O

PI

M15

VCC_AMP_OUT

VCC for AFE Out Amplifiers

PI

M16

GND_AMP_OUT

GND for AFE Out Amplifiers

P

M17

DIFFIN0N

Negative Input In Amplifier 0 (Not used)

I

M18

DIFFIN0P

sitive Input In Amplifier 0 (Not used)

I

M19

DIFFIN1N

Negative Input In Amplifier 1 (Not used)

I

N1

MEMXD12_LCDD18

PHY link signal detect

I

N2

MIIRXER_EXTINT12

MII Rx Error

I

N3

MII_TXER_SPI1CS1

MII TX Error

O

N4

MDC

Management Data Clock

O

N5

VDDRA_USB1

USB1 3.3 V

PI

N6

USB1VRES

USB1 Reference Circuit Input

I

N7

OSC12M_VDD12

Oscillator 12 MHz 1.2 V

PI

N8

VDDIO_NFLQSPI

QSPI I/O

PI

N9

VDDIOC

Keyboard I/O

PI

N10

VDDIO

General I/O

PI

N11

DGPIO30

GPIO (Not used)

O

N12

VDD

1.2 V Core

PI

N13

VDD_ANA

1.8 V Core Analog Output Voltage

PO

N14

MICPWR1

Microphone Power 1 Output (Not used)

PO

N15

SINGIN0

Input of Single-ended In Amplifier 0 (Not used)

I

N16

VCCA

Analog VCC

PI

N17

GNDA

Analog GND

P

N18

XI13M

13.824 MHz XTAL Input

I

N19

BCLK

BCLK output (Not used)

O

P1

MIIRXD1_RGMIIRD1

MII RX Data

I

P2

MIIRXD3_RGMIIRD3

MII RX Data

I

P3

MIIRXD2_RGMIIRD2

MII RX Data

I

P4

MIIRXCRS_U2TX

MII_RXCRS

I

P5

USB1ID

USB1 ID

I

P6

USB1VBUS

USB1 Vbus

PI

P7

KEY_COL6

Trace (Not used)

O

P8

KEY_ROW9

Trace (Not used)

O

P9

KEY_ROW8

Trace (Not used)

O

P10

KEY_ROW7_IIC2SDA

Trace (Not used)

O

P11

U1CTS_DIGMIC_DATA

UART1 Clear To Send (Not used)

I

P12

DGPIO31

GPIO (Not used)

O

P13

TPX2

Not used

I/O

Pin No.

Terminal Name

Contents of Control

I/O setting

Remark

42

KX-NS0154CE

P14

VREF

Reference Voltage Powered by VCCA for Filtering

PO

P15

MICPWR0

Microphone Power 0 Output

PO

P16

SINGIN1

Input of Single-ended In Amplifier 1 (Not used)

I

P17

DCIN2

DC A/D Input 2 (Not used)

I

P18

TPS

Not used

I/O

P19

XO13M

13.824 MHz XTAL out (NC in external oscillator mode)

O

R1

MIIRXCK_RGMIIRXC

RX Clock

I

R2

MIICRS_DV_RGMIIRX_CTL

MII Carrier Sense

I

R3

MIIRXD0_RGMIIRD0

MII RX Data

I

R4

MDIO

Management Data I/O Line

I/O

R5

NFLREADY1_MEMXA22

NFL Ready

I

R6

NFLD7_MEMXA21

NFL Data

I/O

R7

EXTINT3_CLK_REF_OUT

STRAP pin

I

R8

EXTINT1_IIC1SCL

I2C clock

O

R9

KEY_ROW3

DIP SW detect

I

R10

KEY_COL5

Trace (Not used)

O

R11

U1RX

UART1 Serial Data Input

I

R12

U1RTS_DIGMIC_CLK

UART1 Ready To Send (Not used)

O

R13

FORCEMUTE

Hardware Force Mute Function

I

R14

LEDSINK2

LED Sink 2 (Not used)

O

R15

VDD12_DCLS

Class D Digital 1.2 V (Input)1

PI

R16

VSS

Digital GND of Analog Blocks

P

R17

VSS

Digital GND of Analog Blocks

P

R18

TPY1

Not used

I/O

R19

DCIN0

DC A/D Input 0 (Not used)

I

T1

MIITXEN_RGMIITX_CTL

MII TX Enable

O

T2

MIIREFCK_RGMIITXC

MIITXCK

I

T3

MIICOL_U2RX

MII Collision

O

T4

NFLRD_MEMXA24

NFL Read

O

T5

NFLCS0_MEMXA18

NFL Chip Select

O

T6

NFLD4_QDQ3

NFL Data

I/O

T7

NFLD5_QCS0

NFL Data

I/O

T8

KEY_ROW0

DIP SW detect

I

T9

KEY_COL1

DIP SW detect

I

T10

KEY_COL4

Trace (Not used)

O

T11

U1TX

UART1 Serial Data Output

O

T12

TEST_ANA

Analog Test Select (Not used)

I

T13

EXT_REG_CTL

Output Enable for External Regulator (Not used)

O

T14

DCDC_VSENS

Core DCDC Voltage Sense (Not used)

I

T15

SINK_DCLS

Class D Power Amplifier Ground

P

T16

SINK_DCLS

Class D Power Amplifier Ground

P

T17

TPX1

Not used

I/O

T18

TPY2

Not used

I/O

T19

GNDI

GND1 Connection

P

U1

MIITXD1_RGMIITD1

MII TX Data

O

U2

MIITXD0_RGMIITD0

MII TX Data

O

U3

USB1N

USB1 Negative

I/O

U4

NFLALE_MEMXA17

NFL Address Latch

O

U5

NFLWR_MEMXA23

NFL Write

O

U6

NFLD1_QDQ0

NFL Data

I/O

U7

EXTINT0_IIC1SDA

I2C data

I/O

U8

KEY_ROW1

DIP SW detect

I

U9

KEY_COL0

DIP SW detect

I

U10

KEY_ROW6_IIC2SCL

Trace (Not used)

O

U11

EXTINT8_DRV_Vbus

Not used

I

U12

DCINS

DC Power Supply Sense (Not used)

I

U13

PWM0

PWM Output 0 (Not used)

O

U14

VCC5V_DCDC

5V Supply Voltage Input to the Core DCDC Regulator

PI

U15

VDD18_DCLS

Class D Digital 1.8 V (Input)

PI

U16

VCC5V_DCLS

Class D Supply Voltage (Output Amplifiers)

PI

U17

VCC5V_DCLS

Class D Supply Voltage (Output Amplifiers)

PI

U18

VSS

Digital GND of Analog Blocks

P

U19

DCIN1

DC A/D Input 1 (Not used)

I

V1

MIITXD3_RGMIITD3

MII TX Data

O

V2

MIITXD2_RGMIITD2

MII TX Data

O

V3

USB1P

USB1 Positive

I/O

V4

NFLD3_QDQ2

NFL Data

I/O

Pin No.

Terminal Name

Contents of Control

I/O setting

Remark

43

KX-NS0154CE

V5

NFLCLE_MEMXA25

NFL Command Latch

O

V6

NFLD2_QDQ1

NFL Data

I/O

V7

EXTINT2_CLK_OUT

GPIO (Not used)

O

V8

KEY_ROW4

Trace (Not used)

O

V9

KEY_COL3

DIP SW detect

I

V10

KEY_ROW5

Trace (Not used)

O

V11

SD_D0

SDMMC Data (Not used)

I/O

V12

RSTN

External Reset (extend POR)

I

V13

LEDSINK1_PWM1

PWM Output 1 (Not used)

O

V14

COIL_DCDC

Core DCDC Coil

PO

V15

VDD18_DCDC

DCDC Digital 1.8 V Input

PI

V16

VCC33SW_DCLS

Class D 3.3 V Switch

PI

V17

VCC_ANA

VCC Analog Voltage

PI

V18

PAOUTN

Class D Power Amplifier Negative (Not used)

O

V19

PAOUTP

Class D Power Amplifier Positive (Not used)

O

W1

USB2N

USB2 Negative (Not used)

I/O

W2

USB2P

USB2 Positive (Not used)

I/O

W3

XI12M

12MHz clock input for USB

I

W4

XO12M

12 MHz Crystal Feedback (Not used)

O

W5

NFLD0_QCLK

NFL Data

I/O

W6

NFLD6_QCS1

NFL Data

I/O

W7

KEY_COL7_SPI2CS

SPI2 CS

I

W8

KEY_ROW2

DIP SW detect

I

W9

KEY_COL2

DIP SW detect

I

W10

SD_CLK

SDMMC Clock (Not used)

O

W11

SD_CMD

SDMMC Command (Not used)

I/O

W12

VCC_ANA

VCC Analog Voltage

PI

W13

GND_DCDC

DCDC GND

P

W14

SINK_DCDC

Unique Ground for Core DCDC

P

W15

DCDC_VRP

DCDC Internal Voltage for External Filter

PO

W16

VCC33_DCDC

3.3 V Supply Voltage Input

PO

W17

VDDSW_DCLS

Class D VDD Switch

PI

W18

VSS

Digital GND of Analog Blocks

P

W19

DCIN3

DC A/D Input 3 (Not used)

O

Pin No.

Terminal Name

Contents of Control

I/O setting

Remark

44

KX-NS0154CE

16.1.2.

IC101 (DDR2)

Pin No.

Terminal Name

Contents of Control

I/O setting

Remark

A1

VDD

Power Supply

PI

A2

NC

No connect

-

A3

VSS

Ground

P

A7

VSSQ

DQ Ground

P

A8

#UDQS

Data Store

I/O

A9

VDDQ

DQ Power Supply

PI

B1

DQ14

Data Inputs/Outputs

I/O

B2

VSSQ

DQ Ground

P

B3

UDM

Input Data Mask

I

B7

UDQS

Data Store

I/O

B8

VSSQ

DQ Ground

P

B9

DQ15

Data Inputs/Outputs

I/O

C1

VDDQ

DQ Power Supply

PI

C2

DQ9

Data Inputs/Outputs

I/O

C3

VDDQ

DQ Power Supply

PI

C7

VDDQ

DQ Power Supply

PI

C8

DQ8

Data Inputs/Outputs

I/O

C9

VDDQ

DQ Power Supply

PI

D1

DQ12

Data Inputs/Outputs

I/O

D2

VSSQ

DQ Ground

P

D3

DQ11

Data Inputs/Outputs

I/O

D7

DQ10

Data Inputs/Outputs

I/O

D8

VSSQ

DQ Ground

P

D9

DQ13

Data Inputs/Outputs

I/O

E1

VDD

Power Supply

PI

E2

NC

No connect

-

E3

VSS

Ground

P

E7

VSSQ

DQ Ground

P

E8

#LDQS

Data Store

I/O

E9

VDDQ

DQ Power Supply

PI

F1

DQ6

Data Inputs/Outputs

I/O

F2

VSSQ

DQ Ground

P

F3

LDM

Input Data Mask

I

F7

LDQS

Data Store

I/O

F8

VSSQ

DQ Ground

P

F9

DQ7

Data Inputs/Outputs

I/O

G1

VDDQ

DQ Power Supply

PI

G2

DQ1

Data Inputs/Outputs

I/O

G3

VDDQ

DQ Power Supply

PI

G7

VDDQ

DQ Power Supply

PI

G8

DQ0

Data Inputs/Outputs

I/O

G9

VDDQ

DQ Power Supply

PI

H1

DQ4

Data Inputs/Outputs

I/O

Click on the first or last page to see other KX-NS0154CE (serv.man2) service manuals if exist.