Panasonic KX-HTS32RU / KX-HTS824RU Service Manual ▷ View online

17

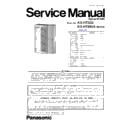

KX-HTS32\KX-HTS824 Series

4.2.1.4.

ROM Function

System software and several configuration data are stored in NAND Flash ROM on Main unit.

When system start, CPU internal boot rom will read basical operating system software and application software from NAND Flash

memory.

And also, during system operation, system configuration and Voice Mail data will be stored in Flash ROM.

When system start, CPU internal boot rom will read basical operating system software and application software from NAND Flash

memory.

And also, during system operation, system configuration and Voice Mail data will be stored in Flash ROM.

Memory I/F

NAND : 512MBytes (x8bit w/ ECC(4bit/512Bytes)

Bus width

8bit

Memory Cell Spec

Page size : 2048+128spare Bytes

Block size : 128k+8k Bytes

Number of Blocks : up to 4096

Block size : 128k+8k Bytes

Number of Blocks : up to 4096

Power

Operating Voltage : 3.3V

Clock

none

Reset

none

NFLASH_IO[3]

NFLASH_IO[7]

NFLASH_IO[1]

NFLASH_IO[0]

NFLASH_IO[0]

NFLASH_IO[0-7]

NFLASH_IO[5]

NFLASH_IO[4]

NFLASH_IO[4]

NFLASH_IO[6]

NFLASH_IO[2]

NFLASH_IO[1]

NFLASH_IO[0]

NFLASH_IO[2]

NFLASH_IO[7]

NFLASH_IO[6]

NFLASH_IO[5]

NFLASH_IO[4]

NFLASH_IO[3]

NFLASH_IO[0]

NFLASH_IO[2]

NFLASH_IO[7]

NFLASH_IO[6]

NFLASH_IO[5]

NFLASH_IO[4]

NFLASH_IO[3]

NFLASH_CLE_N

NFLASH_RE_N

NFLASH_CS1_N

NFLASH_ALE_N

NFLASH_RDBY_N

G

D

G

D

LED_D

LED_ST

LED_SH

CS_SPI

nRESET

CS_SPI

nRESET

DOUT

SCLK

SCLK

8.192MHz

UNITSEL1

UHW0

RWn

NFLASH_CS1_N

UNITSEL0

DEVSEL2

UNITSEL2

DEVSEL2

UNITSEL2

R151

R107

DG

R152

DEVSEL1

DEVSEL0

R137

R143

4.7k

R144

DG

R145

R146

R153

FH_HW0

CLK_HW0

DHW0

R105

+3.3V_CPU

R128

R142

1

2

3

4

5

6

7

8

R127

R106

DIN

nWPS

R104

R136

R132

+3.3V_CPU

R129

TP_8.192MHz

R130

+3.3V_CPU

+3.3V_CPU

R131

R140

R139

C127

C126

nINT_PLD

USB_FLT0

USB_FLT0

R103

R111

R157

8ms

R158

R147

1

2

3

45

6

7

8

IC102

1

NC1

2

NC2

46

NC27

47

NC28

3

NC3

48

NC29

4

NC4

45

NC26

5

NC5

44

I/O7

6

NC6

43

I/O6

7

R/*B

42

I/O5

8

*RE

41

I/O4

9

*CE

40

NC25

10

NC7

39

NC24

11

NC8

38

NC23

12

VCC1

37

VCC2

13

VSS1

36

VSS2

14

NC9

35

NC22

15

NC10

34

NC21

16

CLE

33

NC20

17

ALE

32

I/O3

18

*WE

31

I/O2

19

*WP

30

I/O1

20

NC11

29

I/O0

21

NC12

28

NC19

22

NC13

27

NC18

23

NC14

26

NC17

24

NC15

25

NC16

R173

R148

R141

IC101

AB19

AB19

AC19

AC19

B1

B1

AC22

AC22

AB23

AB23

AB20

AB20

AC21

AC21

AB21

AB21

AC20

AC20

W20

W20

D15

D15

D12

D12

D9

D9

D10

D10

D11

D11

D8

D8

Y22

Y22

AA22

AA22

AA23

AA23

T20

T20

V20

V20

T19

T19

G23

G23

H22

H22

H23

H23

J23

J23

J22

J22

K22

K22

AB22

AB22

D14

D14

D13

D13

T23

T23

U19

U19

W22

W22

Y23

Y23

W23

W23

T22

T22

U23

U23

U22

U22

V23

V23

V22

V22

U20

U20

R19

R19

R20

R20

V19

V19

K23

K23

L22

L22

M22

M22

L23

L23

M23

M23

N22

N22

N23

N23

P23

P23

P22

P22

H20

H20

H19

H19

J20

J20

J19

J19

K19

K19

K20

K20

R125

1

2

3

4

5

6

7

8

R126

1

2

3

4

5

6

7

8

R134

1

2

3

4

5

6

7

8

R135

NAND Flash

512MB

512MB

(To CPLD)

(From CPLD)

(To CPLD)

(From CPLD)

(From CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

Place on solder side

(SLIC_INT)

18

KX-HTS32\KX-HTS824 Series

4.2.1.5.

RAM Function

DDR2 memory is used for program operation and working memory space. DDR2 memory is controled by ddr memory control

function which is embedded in CPU.

function which is embedded in CPU.

Memory I/F

DDR2 : 128MBytes (x16bit x 1chip)

Bus width

16bit

Power

Operating Voltage : 1.8V

Clock

360MHz / DDR2-720

Reset

none

DDR_A[12]

DDR_A[11]

DDR_A[10]

DDR_A[9]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

DDR_A[13-0]

DDR_DQ[2]

DDR_DQ[6]

DDR_DQ[0]

DDR_DQ[3]

DDR_DQ[7]

DDR_DQ[5]

DDR_DQ[0-15]

DDR_DQ[1]

DDR_A[8]

DDR_DQ[8]

DDR_DQ[9]

DDR_DQ[9]

DDR_DQ[10]

DDR_DQ[12]

DDR_DQ[13]

DDR_DQ[14]

DDR_DQ[15]

DDR_DQ[13]

DDR_DQ[14]

DDR_DQ[15]

DDR_A[12]

DDR_BA[1]

DDR_DQ[15]

DDR_DQ[14]

DDR_DQ[13]

DDR_DQ[12]

DDR_DQ[11]

DDR_DQ[10]

DDR_DQ[9]

DDR_DQ[8]

DDR_DQ[7]

DDR_DQ[6]

DDR_DQ[5]

DDR_DQ[4]

DDR_DQ[3]

DDR_DQ[2]

DDR_DQ[1]

DDR_DQ[0]

DDR_DQ[14]

DDR_DQ[13]

DDR_DQ[12]

DDR_DQ[11]

DDR_DQ[10]

DDR_DQ[9]

DDR_DQ[8]

DDR_DQ[7]

DDR_DQ[6]

DDR_DQ[5]

DDR_DQ[4]

DDR_DQ[3]

DDR_DQ[2]

DDR_DQ[1]

DDR_DQ[0]

DDR_BA[0-2]

DDR_BA[0]

DDR_BA[1]

DDR_BA[2]

DDR_BA[1]

DDR_BA[2]

DDR_A[13]

DDR_A[13]

DDR_BA[2]

DDR_BA[0]

DDR_A[11]

DDR_A[10]

DDR_A[10]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

DDR_DQ[4]

DDR_DQ[11]

DG

DG

DG

DDR_DM0

DDR_DM1

DDR_DM1

DDR_nWE

DDR_nRAS

DDR_nCAS

DDR_nRAS

DDR_nCAS

DDR_ODT

DDR_CLK_N

DDR_CLK_P

DDR_nCS

DDR_CKE

DDR_CKE

DDR_nRAS

DDR_nCAS

DDR_nCAS

DDR_ODT

DDR_nCS

DDR_nCS

DDR_CLK_N

DDR_nWE

DDR_CLK_P

DDR_DM0

DDR_DM1

DDR_DM1

DG

DG

C104

C100

DG

C101

R100

R101

DG

C117

C120

C116

R122

C123

R124

C125

R123

R121

R120

R119

R118

R117

R116

R115

C124

C115

R108

C119

C121

CL100

C102

C103

R138

R159

R159

R160

R161

R162

R161

R162

R109

R133

R163

R164

R165

R166

R167

R168

R169

R170

R171

R172

R133

R163

R164

R165

R166

R167

R168

R169

R170

R171

R172

C106

C107

C122

C118

IC101

W7

W7

T1

T1

AB5

AB5

W6

W6

Y5

Y5

Y8

Y8

AC8

AC8

AB7

AB7

AC9

AC9

AB8

AB8

AC10

AC10

AC7

AC7

AB9

AB9

AB10

AB10

Y6

Y6

AC5

AC5

AC6

AC6

AC3

AC3

AB3

AB3

AB6

AB6

AC4

AC4

AB4

AB4

Y7

Y7

U5

U5

T2

T2

Y2

Y2

V4

V4

R2

R2

W4

W4

T4

T4

W1

W1

T5

T5

W2

W2

U1

U1

Y1

Y1

AA2

AA2

AB1

AB1

AA1

AA1

P2

P2

V1

V1

P1

P1

Y9

Y9

U2

U2

W8

W8

AC2

AC2

U4

U4

V2

V2

AB2

AB2

R1

R1

+1.8V_CPU

+1.8V_CPU

+1.8V_CPU

+1.8V_CPU

IC100

J1

VDDL

J7

VSSDL

R1

VDD5

P9

VSS5

M9

VDD4

N1

VSS4

J9

VDD3

J3

VSS3

E1

VDD2

E3

VSS2

B2

VSSQ2

C9

VDDQ5

A7

VSSQ1

M8

A0

M3

A1

C7

VDDQ4

A1

VDD1

A3

VSS1

A9

VDDQ1

C1

VDDQ2

E9

VDDQ6

G1

VDDQ7

C3

VDDQ3

G3

VDDQ8

G7

VDDQ9

G9

VDDQ10

J2

VREF

M7

A2

N2

A3

G2

DQ1

G8

DQ0

N8

A4

N3

A5

H3

DQ3

H7

DQ2

N7

A6

P2

A7

H9

DQ5

H1

DQ4

P8

A8

P3

A9

F9

DQ7

F1

DQ6

M2

A10/AP

P7

A11

C2

DQ9

C8

DQ8

R2

A12

R8

NC5

D3

DQ11

D7

DQ10

R3

NC3

R7

NC4

D9

DQ13

D1

DQ12

L2

BA0

L3

BA1

B9

DQ15

B1

DQ14

L1

BA2

K7

*RAS

E8

*LDQS

F7

LDQS

L7

*CAS

K3

*WE

A8

*UDQS

B7

UDQS

F3

LDM

B3

UDM

E2

NC2

A2

NC1

K9

ODT

L8

*CS

K2

CKE

J8

CLK

B8

VSSQ3

D2

VSSQ4

D8

VSSQ5

E7

VSSQ6

F2

VSSQ7

F8

VSSQ8

H2

VSSQ9

H8

VSSQ10

K8

*CLK

Place near to pin J2

DDR2

128MB

128MB

19

KX-HTS32\KX-HTS824 Series

4.2.1.6.

USB Function

This system supports USB2.0 USB host connector. By connecting USB memory devices system operating data can be backup or

restored.

restored.

4.2.1.7.

RTC Function

This system has Real Time Clock (RTC) device which is battery backed up.

When system starts up, software will get current time from RTC.

When system starts up, software will get current time from RTC.

USB

USB 2.0 1port

Connector

USB Host (Type-A)

Speed

USB 2.0 High speed (480Mbps) /Full speed (12Mbps)

Power

3.3V USB internal PLL

2.5V USB analog PHY function

5V USB Bus Power (up to 500mA)

2.5V USB analog PHY function

5V USB Bus Power (up to 500mA)

Clock

none

Reset

none

CPU Interface

SPI (3wire)

Power

0.9 - 5.5V/0.22uA

Clock

32.768kHz Xtal

Reset

none

LF301

1

2

4

3

USB_FLT0

R303

R301

+5V

USB-GND

DG

USB_EN0

C303

C301

TP301

DG

DG

C307

+3.3V_CPU

DG

R309

JK300

4

3

2

1

6

5

7

8

R347

R348

FG

USB-GND

R314

R305

D301

D303

D328

C309

IC301

1

VIN

2

GND

4

*OC

5

ILIM

3

EN

6

VOUT

Differential pair signal

USB 90ohm

USB0

Isolation Area

GND

+5V

DM

DP

(To CPU)

(From CPLD)

DG

B500

1

2

DIN

R506

R504

DG

TP_32.768kHz

D501

+3.3V_B

+3.3V_CPU

DG

DOUT

SCLK

TP_+3.3V_B

CS_SPI06

+3.3V_CPU

+3.3V_B

CL504

R507

C508

TP_+3V

X500

R545

R546

C506

IC500

1

OSCI

2

OSCO

3

CLKOE

4

*INT

5

VSS

6

CE

7

SCL

8

SDIO

9

CLKOUT

10

VDD

11

FRAME

D502

D503

C507

RTC and Backup battery

(From CPLD)

(To CPU)

(From CPU)

(From CPU)

Place on solder side

Place on solder side

Place on solder side

20

KX-HTS32\KX-HTS824 Series

4.2.2.

Wireless LAN

In this section, we will describe general function of embedded Wireless LAN block that is responsible for IEEE802.11b/g/n 2.4GHz

Wirelss LAN interface function.

Wirelss LAN interface function.

(1) Block Diagram

• KX-HTS824/32 has the RF of the two systems for 2×2MIMO

• It is provided with a BPF for unwanted signal suppression at Receiver block

• Base clock of the RF local frequency is 36MHz (crystal oscillator)

• It is provided with a BPF for unwanted signal suppression at Receiver block

• Base clock of the RF local frequency is 36MHz (crystal oscillator)

36MHz

Rx

Rx

x

RXR

RXR

Tx

Lo

ANT1

x

RXR

RXR

Rx

x

RXR

RXR

Tx

ANT2

3.3V

1.8V

ATT

ATT

BB_IQ_1

BB_IQ_2

IC400

IC402

IC403

DL400

DL401

X400

Click on the first or last page to see other KX-HTS32RU / KX-HTS824RU service manuals if exist.