Panasonic KX-HTS32RU / KX-HTS824RU Service Manual ▷ View online

13

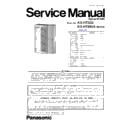

KX-HTS32\KX-HTS824 Series

SPI

SPI

SPI

TD

M

TDM

SPI

-

TDM

-

SPI

-

TDM

-I

F

SPI

-I

F

RJ45

J

K

304

RJ45

J

K

303

RJ45

J

K

302

USB

TYPE

-A

J

K

300

USB

O

C

Co

n

tr

o

l

G

b

EPu

ls

e

T

ransform

er

G

b

EPu

ls

e

T

ransform

er

G

b

EPu

ls

e

T

ransform

er

AN

T

CN401

AN

T

CN402

2.4GHz

BP

F

DP

DT

2.4GHz

WLAN

BA

S

E

BA

ND

WR

X312

2.4GHz

BP

F

DP

DT

TR/RT

S

W

TR/RT

S

W

36MHz

Xt

al

GRX330

SoC

PXB4389

-

7

20

M

32b

it

MIPS

34Kc

Clock:

720M

Hz

IQ

CN

T

CL

K(8.192MHz)

NA

ND F

lash Mem

ory

512MB/8bit/E

C

C

4bit

C3FB

VY000039

H27U4G8F2ETR

-

B

I

DDR2

Mem

ory

128MB/16bit/800M

C3AB

TY000121

NT5TU64M

16HG

-

A

C

IO

[7:0]

Co

ntrol

DQ

[15:0]

A[12:0]/BA[2:0]

Co

ntrol

CPLD

DEVSEL[2:0]

UNIT

S

E

L

[2

:0]

SPI

-

IF

RT

C

32.768

kH

z X

tal

CS_SPI06

SCLK/DIN/DOUT

DE56#1

DE56#2

DuS

LIC#1

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

RJ1

1

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

RJ1

1

JK900

-B

RJ1

1

JK900

-C

RJ1

1

JK900

-D

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

A

RJ1

1

JK700

-

B

DuS

LIC#2

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

C

RJ1

1

JK700

-

D

DuS

LIC#3

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

E

RJ1

1

JK700

-

F

DuS

LIC#4

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

G

RJ1

1

JK700

-

H

-I

F

-I

F

-

-

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

SCLK/DIN/DOUT

TDM

-

IF

TDM

-IF(HW1)

SPI -

SPI-IFl(SCLK/CS_SPI/DIN/DOUT/RWn)

TDM-

IF(H

W0)

DEVSEL[2:0]/UNITSEL[2:0

]

CPLD

DuS

LIC#1

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-A

RJ1

1

JK700

-B

DuS

LIC#2

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-C

RJ1

1

JK700

-D

DuS

LIC#3

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-E

RJ1

1

JK700

-F

DuS

LIC#4

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-G

RJ1

1

JK700

-H

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

SPI-

IF

-IFl(SCLK1/DIN1/DOUT1)

TDM-

IF

CPLD

DuS

LIC#1

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

A

RJ1

1

JK700

-

B

DuS

LIC#2

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

C

RJ1

1

JK700

-

D

DuS

LIC#3

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

E

RJ1

1

JK700

-

F

DuS

LIC#4

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

FXS

Int

e

rf

ac

e

Analog

Ci

rc

u

it

RJ1

1

JK700

-

G

RJ1

1

JK700

-

H

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

TDM

-I

F

SPI

-I

F

SPI-

IF

TDM-

IF

CPLD

SPI-I

F

DE56#1

DE56#2

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

RJ1

1

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

FXO

Int

e

rf

ac

e

An

a

log

Ci

rc

u

it

RJ1

1

JK900

-

B

RJ1

1

JK900

-

C

RJ1

1

JK900

-

D

TDM-

IF

CPLD

DE56#1

DP

H

Interface A

nalog

C

ircuit

RJ1

1

JK101

DP

H

Interface A

nalog

C

ircuit

TDM-

IF

DOOR

O

PEN

ER

Interface

Ci

rc

u

it

CN100

-IFl(SCLK2/DIN2/DOUT2/RWn)

-IF(HW2)

TDM

-

IF

-I

F

-I

F

TD

M

-I

F

SPI

-I

F

-I

F

-I

F

TDM

-

IF

SPI

-

IF

TD

M

-

IF

SPI

-

IF

DEVSEL[2:0]

DEVSEL[2:0]

DEVSEL[2:0]

DEVSEL[2:0]

UNIT

S

E

L

[2:0]

DEVSEL[2:0]

Control(Reset/Int)

Control(Reset/

Int)

SPI-

IF

Contro

l(Reset/Int)

Contro

l(Reset/Int)

Contro

l(Reset/Int)

PS

YS

OUTP/N

(36MHz)

n

HRS

T

POR

BT_

MODE_

OE

n

R

ES

ET_

OUT[5:0]

n

R

ES

ET_OP[3:0]

nR

E

S

E

T

_O

P

[0]

nR

E

S

E

T

_O

P

[1]

n

R

ES

ET_

OP[2]

nR

E

S

E

T

_O

P

[3]

CL

K

(13.824MHz)

13.824MHz

Xt

al

13.824MHz

Xt

al

CLK(13.824MHz)

CLK(13.824MHz)

nR

E

S

E

T

n

R

ES

ET_

OUT

nR

E

S

E

T

_O

UT

nR

E

S

E

T

_O

UT

SP

I-

IF

SP

I-

IF

SP

I-

IF

TD

M

-I

F

TD

M

-I

F

SP

I-

IF

TD

M

-I

F

SP

I-

IF

TD

M

-I

F

TD

M

-I

F

PBX UNIT

MAIN UNIT

LCOT4

Block

SLC8 Block

Option SLC8

Card

Option SLC8

Card

Option LCOT4

Card

Option DPH2

Card

AC/D

C

Power Unit

DC

/DC

Co

n

v

24V

15V

DC12V

Ba

ttery I

/F

DC

/DC

Co

n

v

DC

/DC

Co

n

v

DC

/DC

Co

n

v

DC

/DC

Co

n

v

5V

1.05V

1.8V

3.3V

LD

O

LD

O

1.5V

2.5V

Reset

Detect

POR

12V

BTMODE_

OE

AC/DC Unit

TDM

SPI

TDM

-

IF

IF

TDM

IF

IF

IF

IF

n

R

ES

ET_

OUT

-

IF(SCLK0/CS_SPI[05:04]/DIN0/

DOUT0/RWn)

IF

SPI

LA

N

PORT

L

A

N/W

AN P

O

R

T

WA

N

PORT

US

B2.0 PORT

SPI

SPI

TDM

Control(Reset/Int)

14

KX-HTS32\KX-HTS824 Series

4.2.1.

CPU/L2SW/DSP/ROM/RAM/USB/RTC

4.2.1.1.

CPU Function

In this section, we will discribe general function of CPU that is responsible for PBX function, monitoring and control each unit.

Processor

MIPS 34Kc/720MHz

Internal Memory

Instruction Cache : 32Kbytes

Data Cache : 32Kbytes

Data Cache : 32Kbytes

Dual Thread Function

VPE0 : Application / VPE1 : DSP Fuction

Memory I/F

DDR2 : 128MBytes (x16bit x 1chip)

NAND : 512MBytes (x8bit w/ ECC(4bit/512Bytes)

NAND : 512MBytes (x8bit w/ ECC(4bit/512Bytes)

Boot Device

CPU Internal Boot ROM

L2SW Function

Gigabit GMAC/PHY

L2SW Mac Entries : up to 2048

Traffic Management function

L2SW Mac Entries : up to 2048

Traffic Management function

802.11 Wireless LAN

802.11b/g/n

1x1/2x2 MIMO mode support

1x1/2x2 MIMO mode support

USB

USB2.0

Power

Each voltage described as below is required for CPU operation. In this system, these voltage is

generated by DCDC converter device and supplyed to CPU.

generated by DCDC converter device and supplyed to CPU.

3.3V Digital circuit I/O voltage

2.5V Internal circuit voltage

1.8V DDR2 circuit voltage

1.05V CPU core voltage

2.5V Internal circuit voltage

1.8V DDR2 circuit voltage

1.05V CPU core voltage

Clock

The frequency of system clock of CPU is 36MHz, this clock is generated by Wireless LAN control LSI

and is disributed to CPU via differential signal.

And the frequency of CPU internal operating clock is 720MHz, this clock is generated by internal PLL

circuit from 36MHz input clock.

and is disributed to CPU via differential signal.

And the frequency of CPU internal operating clock is 720MHz, this clock is generated by internal PLL

circuit from 36MHz input clock.

Reset

The basic reset signal called POR (Power On Reset) is generated by voltage monitoring IC on power

circuit and is connected to the CPU por terminal.

circuit and is connected to the CPU por terminal.

EJTAG_TRST_U

EJTAG_TDI_U

EJTAG_TDO_U

EJTAG_TMS_U

EJTAG_TCK_U

EJTAG_TDI_U

EJTAG_TDO_U

EJTAG_TMS_U

EJTAG_TCK_U

C2000

C2001

R2006

nHRST

R2007

R2010

R2012

R2011

R2013

R2014

DG

DG

R2003

nPOR

FSYSOUT_P

FSYSOUT_N

FSYSOUT_N

CL2002

+3.3V_CPU

D2000

C2003

JTAG_TRST

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TCK

JTAG_RST

+2.5V

CL2007

DG

+3.3V_CPU

BTMODE_OE

IC101

G22

G22

A15

A15

E23

E23

E22

E22

M19

M19

L19

L19

D23

D23

A17

A17

A16

A16

B17

B17

B16

B16

A14

A14

B14

B14

E18

E18

E19

E19

L2

L2

F23

F23

C22

C22

C23

C23

J1

J1

J2

J2

IC3001

1

NC

2

A

4

Y

5

VCC

3

GND

EJTAG DEBUG

For Debug

15

KX-HTS32\KX-HTS824 Series

4.2.1.2.

L2SW Function

This CPU has internally Layer 2 Switch (L2SW) and Gigabit PHY function which suppports Multiport Gigabit ether switch.

And this internal L2SW block can support non-blocking L2 packet switching with hardware packet processing engine.

This system has tree Gigabit ether port LAN, WAN and LAN/WAN (Selectable).

And this internal L2SW block can support non-blocking L2 packet switching with hardware packet processing engine.

This system has tree Gigabit ether port LAN, WAN and LAN/WAN (Selectable).

L2SW Function

Gigabit GMAC/PHY

L2SW Mac Entries : up to 2048

Traffic Management function

L2SW Mac Entries : up to 2048

Traffic Management function

Connector

RJ45(8pin)

Power

For L2SW and Gigabit PHY operation, below voltage should be supplyed.

3.3V Gigabit PHY

2.5V RGMII pin I/O

1.05V Gigabit PHY

3.3V Gigabit PHY

2.5V RGMII pin I/O

1.05V Gigabit PHY

Clock

L2SW and PHY operation clock is generated by internal PLL device in CPU.

Reset

L2SW and PHY reset signal is generated by internal reset login in CPU.

GY

Q303

C330

C324

C327

C333

C336

GTP0_AN

GTP0_AP

GTP0_DP

GTP0_CN

GTP0_BN

GTP0_BP

GTP0_CP

GTP0_DN

Q300

NC

R325

R317

+3.3V_CPU

R321

DG

LED3

+3.3V_CPU

R331

R343

LED2

R340

C313

DG

C314

C315

DG

DG

DG

DG

DG

C312

R319

R313

R310

FG

R316

R354

R351

T300

1

2

3

16

15

14

20

19

18

4

17

21

22

23

24

5

6

7

8

9

10

11

3

1

2

1

JK302

9

10

11

12

7

8

5

6

3

4

1

2

D304

D316

D305

D317

D306

D318

D307

D319

WAN

LINK/ACT

SPEED

(1G/OTHER)

(1G/OTHER)

16

KX-HTS32\KX-HTS824 Series

4.2.1.3.

DSP Function

DSP Function

MIPS processor VPE1 thread

Dedicated Voice Firmware

Voice Codec PCM/G.711(u-law/A-law)/G.729a

Jitter buffer

Echo canceller

DTMF generate/receive

Dedicated Voice Firmware

Voice Codec PCM/G.711(u-law/A-law)/G.729a

Jitter buffer

Echo canceller

DTMF generate/receive

TDM side I/F

TDM clock slave mode

Interface signal

FH_HW0 : TDM Frame Header signal (8kHz from CPLD)

UHW0 : TDM Upstream Highway (to CPLD)

DHW0 : TDM Downstrem Highway (from CPLD)

CLK_HW0 : TDM clock (4.096MHz from CPLD)

Interface signal

FH_HW0 : TDM Frame Header signal (8kHz from CPLD)

UHW0 : TDM Upstream Highway (to CPLD)

DHW0 : TDM Downstrem Highway (from CPLD)

CLK_HW0 : TDM clock (4.096MHz from CPLD)

Power

For DSP operation, below voltage should be supplyed.

3.3V Internal PLL

1.05V CPU/DSP Core

3.3V Internal PLL

1.05V CPU/DSP Core

Clock

DSP operation clock is generated by internal PLL device in CPU.

Reset

DSP reset signal is generated by internal reset login in CPU.

NFLASH_IO[1]

NFLASH_IO[0]

NFLASH_IO[0]

NFLASH_CLE_N

NFLASH_RE_N

NFLASH_CS1_N

NFLASH_ALE_N

NFLASH_RDBY_N

LED_D

LED_ST

LED_SH

CS_SPI

nRESET

CS_SPI

nRESET

DOUT

SCLK

SCLK

UNITSEL1

UHW0

RWn

NFLASH_CS1_N

UNITSEL0

DEVSEL2

UNITSEL2

DEVSEL2

UNITSEL2

R151

R107

DG

R152

DEVSEL1

DEVSEL0

R137

R146

R153

FH_HW0

CLK_HW0

DHW0

R105

+3.3V_CPU

R128

R142

1

2

3

4

5

6

7

8

R127

R106

DIN

nWPS

R104

R136

R132

+3.3V_CPU

R129

R130

R131

R130

R131

nINT_PLD

USB_FLT0

USB_FLT0

R103

R111

8ms

R158

R147

1

2

3

45

6

7

8

R173

R148

R141

IC101

AB19

AB19

AC19

AC19

B1

B1

AC22

AC22

AB23

AB23

AB20

AB20

AC21

AC21

AB21

AB21

AC20

AC20

W20

W20

D15

D15

D12

D12

D9

D9

D10

D10

D11

D11

D8

D8

Y22

Y22

AA22

AA22

AA23

AA23

T20

T20

V20

V20

T19

T19

G23

G23

H22

H22

H23

H23

J23

J23

J22

J22

K22

K22

AB22

AB22

D14

D14

D13

D13

T23

T23

U19

U19

W22

W22

Y23

Y23

K23

K23

L22

L22

M22

M22

L23

L23

M23

M23

N22

N22

N23

N23

P23

P23

P22

P22

H20

H20

H19

H19

J20

J20

J19

J19

K19

K19

K20

K20

R125

1

2

7

8

R134

1

2

3

4

5

6

7

8

R135

(From CPLD)

(To CPLD)

(From CPLD)

(From CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

(To CPLD)

(SLIC_INT)

Click on the first or last page to see other KX-HTS32RU / KX-HTS824RU service manuals if exist.