Panasonic KV-S1057C / KV-S1027C / KV-SL1066 / KV-SL1056 / KV-SL1055 / KV-SL1036 / KV-SL1035 Service Manual ▷ View online

69

Fig.10.2.3

Fig.10.2.4

Fig.10.2.5

CN8-1 Motor OUT

Note: Frequency depends on each model

Note: Frequency depends on each model

CN13-2 US OUT S1057C

CN9-1 R415

US-AMP_OUT

70

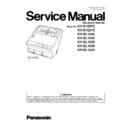

11 Block Diagram

11.1. Block Diagram-1

KV-S1057C/SL1066

CIS

(for Front side)

VLED(7 V)

LEDr

LEDg

LEDb

LEDb

CIS

(for Back side)

VLED( 7 V)

LED

Drive

Motor Drive

Motor Drive

(IC19)

(IC19)

CLKH

IOCLKH

ICLKH

OCLKH

IRQL

IACKL

ORQL

ORQL

OACKL

BDH[15:0]

UDH[15:8]

UDH[15:8]

UDH[7:0]

CCSL

CRDL

CRDL

CWRL

CIH[1:0]

DONEH

INTL

RESET

SAH[19:0]

SDH[31:0]

SDH[31:0]

SOEL

SWEL

SWEL

DAC

DAC (IC7)

(IC7)

MOT1_VREF

US_GAIN

LED_F_DAR

LED_F_DAG

LED_F_DAB

LED_B_DAR

LED_F_DAG

LED_F_DAB

LED_B_DAR

LED_B_DAG

LED_B_DAB

PLT VREF

START LED

START COMP

START OFFSET

AO1

AO2

AO3

AO4

AO5

AO6

AO7

AO8

AO9

AO10

AO11

AO12

AO2

AO3

AO4

AO5

AO6

AO7

AO8

AO9

AO10

AO11

AO12

Motor

Couble Detect

CIS LED

(Front)

CIS LED

(Back)

PLT Motor

START

START

START

START

START

LED

Drive

Double Feed

Generate

Double Feed

Receive

OVL108

OVL110

OVL109

OVL110

OVL109

OVL65

SPI FLASH 4MByte

SPI FLASH 4MByte (IC8)

(IC8)

12Ch

12Ch

Panel IF

Panel IF

CLK

DI

LD

KSSTART

KSTXD

KSRXD

KSCLK

KSTXD

KSRXD

KSCLK

KRST

POWERSW

POWERSW

SCLK

SI/SIO0

SO/SIO1

CS#

WP#/ACC

ADC

US_IN

ATT_ON

US_CLK

Motor I/F

Flex

Risc

Risc

PM36

SPI

GPIO

Scanner

I/F

Flex

Risc

Risc

GPIO

Document

Sensor

Sensor

Start

Sensor

START

PAPER

LED_F_DAR

LED_F_DAG

LED_F_DAG

LED_B_DAR

LED_B_DAG

LED_B_DAB

LED_B_DAG

LED_B_DAB

UART

(Ch0)

DEBUG

CONNECTOR

(UART)

OVL185

OVL186

OVL186

RXD

TXD

TXD

RESET

SDRAM

I/F

*SLEEP

POW_CNT1

PLL

RESET

GPIO

CPU(IC4)

(IC4)

128

128MByte

MByte

1G

1Gbit

bit

16bit bus

16bit bus

DDR2

DDR2(IC21)

(IC21)

RESET IC

RESET IC(IC6)

(IC6)

12

12MHz

MHz

JTAG

DEBUG

PowerControl

FET)

MODEL ID

Pull Up or

Pull Down)

MDLNAME0

MDLNAME1

MDLNAME3

MDLNAME4

MDLNAME1

MDLNAME3

MDLNAME4

BDREV0

BDREV1

RESERV

BDREV1

RESERV

RESERV

MODE

CLK

FSI

LEDr

LEDg

LEDb

LEDb

MODE

CLK

FS

SIG

US_GAIN

VREF

VREF

EEPROM

EEPROM (IC5)

(IC5)

WP

SCL

SDA

SCL

SDA

4Kbit

4Kbit

XIN1

XOUT1

RESETN

IN1

IN2

IN3

IN 4

IN5

IN6

IN2

IN3

IN 4

IN5

IN6

MCLK

TGSYNC

OP [9:0]

OC1

OC2

OC2

AFE

AFE (IC2)

(IC2)

SEN

SCK

SCK

SDO

SDI

VRLC

USB

(Device)

USB2.0

Connector

GPIO

VBUS

PCIe

Door

Sensor

Sensor

DOOR

Auto/Manual

Sensor

Sensor

Auto/Manual

128MByte

1Gbit

16bit bus

DDR2

DDR2(IC20)

(IC20)

Panel

KEY

Power

Start/Stop

Skip

Up

Down

Start/Stop

Skip

Up

Down

LED

Ready

Error

Error

USB3.0

Connector

Clock

Genelator

OVL106

ACH11

ACH09

ACH10

ACH08

ACH09

ACH10

ACH08

XSPI1CS0

XSPI1DO

XSPI1DI

XSPI1CLK

XSPI1DO

XSPI1DI

XSPI1CLK

XSPI0CCLK

XSPI0DO

XSPI0DI

XSPI0CS0

XSPI0DO

XSPI0DI

XSPI0CS0

ACH12

ACH13

OVL111

OVL112

OVL113

OVL112

OVL113

OVL00

OVL25

OVL26

OVL27

OVL28

OVL26

OVL27

OVL28

ACH1

OVL155

OVL 85

OVL41

OVL63

OVL64

OVL63

OVL64

OVL61

OVL130

OVL129

OVL129

OVL131

OVL132

OVL132

USB3.0 Controller

USB3.0 Controller (IC26)

(IC26)

(IC27)

(IC27)

OVL43-50

OVL53-60

OVL53-60

OVL107

OVL110

OVL109

M

GPIO

Motor I/F

Flex

Risc

Risc

Motor Drive

Motor Drive (IC18)

(IC18)

STEP

DIR

RESET

RESET

ENABLE

MS1

MS2

MS1

MS2

OUT1A

OUT2A

MOT1_VREF

M

STBY

ENABLE

ENABLE

PHA1

PHB1

IN0

IN1

IN2

IN3

PHB1

IN0

IN1

IN2

IN3

OUT1A

OUT2A

MOT2_VREF

OVL38

OVL96

OVL96

OVL90

OVL91

IOVL92

OVL94

OVL93

OVL95

OVL91

IOVL92

OVL94

OVL93

OVL95

OVL86

OVL170

OVL169

OVL169

OVL166

IOVL167

OVL168

IOVL167

OVL168

GPIO

(IC30)

(IC30)

OVL09 -24

OVL02 -08

OVL02 -08

OVL29

OVL30

OVL31

OVL30

OVL31

OVL32-33

OVL34

OVL35

OVL36

OVL36

ACH2

OVL152

OVL153

OVL153

OVL177

OVL193

OVL82

OVL83

OVL139

OVL138

OVL82

OVL83

OVL139

OVL138

PERSTN02

GPIO1

GPIO2

SPU1TXD

SPU1RXD

GPIO1

GPIO2

SPU1TXD

SPU1RXD

SRAM(IC36)

A0-A18

D0-D15

CS

OE

WE

UB

LB

SRAM(IC37)

A0-A18

D0-D15

CS

OE

WE

UB

LB

OVL151

GPIO

OVL147

OVL148

OVL150

START COMP

START LED

OVL172

OVL173

OVL173

OVL160

OVL161

OVL162

OVL163

OVL175

OVL176

OVL178

OVL179

OVL161

OVL162

OVL163

OVL175

OVL176

OVL178

OVL179

MCLK

TGSYNC

OP[9:0]O

OP[9:0]O

OC1

SEN

SCK

SCK

SDO

SDI

VRLC

FPGA

FPGA(IC43)

(IC43)

LVDS

LVDS

LVDS

SPICS2

SPIWD

SPIRD

SPICLK

AFE

AFE(IC3)

(IC3)

IN1

IN2

IN3

IN 4

IN5

IN6

IN2

IN3

IN 4

IN5

IN6

MCLKCISF

SPCSF

MCLKAFEF

SPAFEF

SPCSF

MCLKAFEF

SPAFEF

MCLKCISB

SPCSB

MCLKAFEB

SPCSB

MCLKAFEB

SPAFEB

BCLKI

BCLKI

FD0-9

FCLKI

FOC2

FCLKI

FOC2

BD0-9

SD0CLK

SP

FPRESET

NSTATUS

NCONFIG

CONFDONE

INITDONE

OVL127

OVL52

OVL136

Platen Motor

Platen Motor

Conveyor Motor

Conveyor Motor

Program and Image Memory

Program and Image Memory

JPEG

Comp ression

Comp ression

SIG

A/D converter

A/D converter

A/D

A/D converter

converter

D/A

D/A

Main Program

Main Program &

Shading Correction Data

Shading Correction Data

Backup Data

Backup Data

KV

KV- SL1066

SL1066

KV

KV- S1057C

S1057C

71

KV-S1027C/SL1035/SL1036/SL1055/SL1056

CIS

(for Front side)

VLED(7V)

LEDr

LEDg

LEDb

LEDb

CIS

(for Back side)

VLED(7V)

LED

Drive

SDO

Motor Drive(IC19)

DAC (IC7)

MOT1_VREF

US_GAIN

LED_F_DAR

LED_F_DAG

LED_F_DAB

LED_B_DAR

LED_F_DAG

LED_F_DAB

LED_B_DAR

LED_B_DAG

LED_B_DAB

PLT VREF

START LED

START COMP

AO1

AD2

AO3

AO4

AO5

AO6

AO7

AO8

AO9

AD10

AD11

AD12

AD2

AO3

AO4

AO5

AO6

AO7

AO8

AO9

AD10

AD11

AD12

Motor

DFS plate

CIS LED

(Front)

CIS LED

(Back)

PLT Motor

START

START

START

LED

Drive

Double Feed

Generate

Double Feed

Receive

OVL108

OVL110

OVL109

OVL110

OVL109

OVL65

OVL165

SPI FLASH 4MByte (IC8)

12Ch

Panel IF

CLK

DI

LD

KSSTART

KSTXD

KSRXD

KSTXD

KSRXD

KSCLK

SCLK

SI/SIO0

SO/SIO1

CS#

WP#/ACC

ADC

US_IN

ATT_ON

US_CLK

Motor I/F

Flex

Risc

Risc

PM36

SPI

GPIO

Scanner

I/F

Flex

Risc

Risc

GPIO

Document

Sensor

Sensor

Start

Sensor

START

PAPER

LED_F_DAR

LED_F_DAG

LED_F_DAB

LED_F_DAG

LED_F_DAB

LED_B_DAR

LED_B_DAG

LED_B_DAB

LED_B_DAG

LED_B_DAB

UART

(Ch0)

DEBUG CONNECTOR

(UART)

OVL185

OVL186

OVL186

RXD

TXD

TXD

RESET

SDRAM

I/F

6VLOAD

*SLEEP

POW_CNT1

PLL

RESET

GPIO

CPU (IC4)

64MByte

512Mbit

16bit bus

DDR2 (IC21)

RESET IC (IC6)

12MHz

JTAG

DEBUG CONNECTOR

( ICE )

Power Control

FET)

MODEL ID

Pull Up or

Pull Down)

MDLNAME0

MDLNAME1

MDLNAME3

MDLNAME3

MDLNAME4

BDREV0

BDREV1

RESERV

RESERV

RESERV

RESERV

MODE

CLK

FSI

CNT

LEDr

LEDg

LEDb

LEDb

MODE

CLK

FS

CNT

SIG

US_GAIN

RINP

GINP

BINP

GINP

BINP

MCLK

VSMP

RSMP

VSMP

RSMP

OP[7:0]

AFE (IC3)

SEN

SCK

SCK

SDI

OEB

VRLC

VREF

VREF

EEPROM (IC5)

WP

SCL

SDA

SCL

SDA

4Kbit

XIN1

XOUT1

RESETN

RINP

GINP

BINP

GINP

BINP

MCLK

VSMP

RSMP

VSMP

RSMP

OP[7:0]

AFE (IC2)

SEN

SCK

SCK

SDI

OEB

VRLC

USB

(Device)

USB2.0

Connector

GPIO

VBUS

PCIe

Door

Sensor

Sensor

DOOR

Auto/Manual

Sensor

Sensor

Auto/Manua

64MByte

512Mbit

16bit bus

DDR2(IC20)

Panel

KEY

Power

Start/Stop

Skip

Up

Down

Start/Stop

Skip

Up

Down

LED

Ready

Error

Error

Seg/LCD

USB3.0

Connector

Clock

Genelator

GND

GND

OVL106

ACH11

ACH09

ACH09

ACH10

ACH08

ACH08

XSPI1CS0

XSPI1DO

XSPI1DI

XSPI1CLK

XSPI1DO

XSPI1DI

XSPI1CLK

XSPI0CCLK

XSPI0DO

XSPI0DI

XSPI0CS0

XSPI0DO

XSPI0DI

XSPI0CS0

SDO

OVL140

OVL143

OVL144

OVL141

OVL111

OVL112

OVL113

OVL112

OVL113

OVL142

ACH1

OVL155

OVL85

OVL85

OVL48

OVL49

OVL50

OVL49

OVL50

OVL54

OVL51

OVL52

OVL51

OVL52

OVL46

OVL47

OVL47

USB3.0 Controller (IC26)

(IC27)

OVL119- 126

OVL55- 62

OVL53- 60

M

GPIO

Motor I/F

Flex

Risc

Risc

Motor Drive(IC18)

STEP

DIR

RESET

RESET

ENABLE

MS1

MS2

MS1

MS2

REF

OUT1A

OUT1B

OUT2A

OUT2B

MOT1_VREF

M

STBY

ENABLE

ENABLE

PHA1

PHB1

IN0

IN1

IN2

IN3

PHB1

IN0

IN1

IN2

IN3

OUT1A

OUT1B

OUT2A

OUT2B

MOT2_VREF

OVL38

OVL96

OVL96

OVL90

OVL91

OVL91

IOVL92

OVL94

OVL93

OVL94

OVL93

OVL95

OVL86

OVL170

OVL169

OVL169

OVL166

IOVL167

IOVL167

OVL168

GPIO

OVL145

OVL146

ACH2

OVL152

OVL153

OVL153

OVL177

OVL193

OVL82

OVL83

OVL139

OVL138

OVL83

OVL139

OVL138

PERSTN02

GPIO1

GPIO2

SPU1TXD

SPU1RXD

GPIO1

GPIO2

SPU1TXD

SPU1RXD

OVL151

GPIO

OVL147

OVL148

OVL150

START OFFSET

START LED

OVL191

OVL172

OVL173

OVL172

OVL173

OVL160

OVL161

OVL161

OVL162

OVL163

OVL163

OVL175

OVL176

OVL178

OVL176

OVL178

OVL179

A/D

A/D

Program &

Image Memory

Image Memory

D/A

converter

KRST

POWERSW

POWERSW

Main Program

Shading Correction

Data

KV- SL10xx

xx

KV- S1027C

7C

72

On this system, the CPU (IC4) controls the operation of CIS (Contact Image Sensor), Motor (Conveyor Motor,PLATEN Motor), Sen-

sors' block (Paper, Starting, Door,Auto,Double Feed Detect) and Panel Block (LCD,LEDs, Switch) to execute scanning documents.

sors' block (Paper, Starting, Door,Auto,Double Feed Detect) and Panel Block (LCD,LEDs, Switch) to execute scanning documents.

(Paper Feeding)

The CPU (IC4) provides the Motor Driver (IC19) with some motor-pulse signals to drive the Conveyor Motor to execute scan-

ning documents.

ning documents.

(Image Processing)

KV-S1027C/KV-SL1056/SL1055/SL1036/SL1035

KV-S1027C/KV-SL1056/SL1055/SL1036/SL1035

1. This scanner has 2 CISs (CIS(F) and CIS (B)) so that both sides of document can be scanned independently.

At first, both CIS (F) and CIS (B) are driven by the drive pulses (CIS Transfer Gate pulse and CIS Transfer Gate Clock) that

are output from the pulse generation circuit in the CPU (IC4).

are output from the pulse generation circuit in the CPU (IC4).

2. As the result of this, image analog signals "SIG" are output from the CIS (F) and the CIS (B) respectively.

3. The analog signals are alternately converted to digital signals (Digital Signal for Front, Digital Signal for Back by the AFE

3. The analog signals are alternately converted to digital signals (Digital Signal for Front, Digital Signal for Back by the AFE

(IC2,IC3) that operates as an A/D converter.

4. The converted digital signals are divided into two parts (Digital Signals for Front and Digital Signals for Back), and are stored

to the DDR2 Memory (IC20,IC21) temporarily by the CPU (IC4).

5. According to the command from the PC, DSP in the CPU (IC4) performs image processing such as shading, color conversion

(Only applied to color image data), and JPEG compression by using DDR2 Memory (IC20,IC21) that enables the intermediate

data (Only applied to color image data)

data (Only applied to color image data)

6. After handling the above process, the CPU (IC4) stores the data into the DDR2 Memory (IC20,IC21).

7. Controlled by USB Controller in the CPU (IC4), the processed data is transmitted from DDR2 Memory (IC20,IC21) to the PC

7. Controlled by USB Controller in the CPU (IC4), the processed data is transmitted from DDR2 Memory (IC20,IC21) to the PC

via the USB interface.

KV-S1057C/KV-SL1066

1. This scanner has 2 CISs (CIS(F) and CIS (B)) so that both sides of document can be scanned independently.

At first, both CIS (F) and CIS (B) are driven by the drive pulses (CIS Transfer Gate pulse and CIS Transfer Gate Clock) that

are output from the pulse generation circuit in the FPGA (IC43).

are output from the pulse generation circuit in the FPGA (IC43).

2. As the result of this, image analog signals "SIG" are output from the CIS (F) and the CIS (B) respectively.

3. The analog signals are alternately converted to digital signals (Digital Signal for Front, Digital Signal for Back by the AFE

3. The analog signals are alternately converted to digital signals (Digital Signal for Front, Digital Signal for Back by the AFE

(IC2,IC3) that operates as an A/D converter.

4. The digital signal output from AFE(IC2,IC3) is converted to a differential signal in FPGA(IC43).

The differential signals ( CIS(F) data and CIS(B) data) are output from FPGA(IC43) to CPU(IC4)

5. The converted digital signals are divided into two parts (Differential Signals for Front and Differential Signals for Back), and

are stored to the DDR2 Memory (IC20,IC21) temporarily by the CPU (IC4).

6. According to the command from the PC, DSP in the CPU (IC4) performs image processing such as shading, color conversion

(Only applied to color image data). In addition, JPEG compression is performed in PM-36(IC30).

7. After handling the above process, the CPU (IC4) stores the data into the DDR2 Memory (IC20,IC21).

8. Controlled by USB Controller (IC26), the processed data is transmitted from DDR2 Memory (IC20,IC21) to the PC via the

8. Controlled by USB Controller (IC26), the processed data is transmitted from DDR2 Memory (IC20,IC21) to the PC via the

USB interface.

Click on the first or last page to see other KV-S1057C / KV-S1027C / KV-SL1066 / KV-SL1056 / KV-SL1055 / KV-SL1036 / KV-SL1035 service manuals if exist.