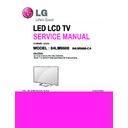

LG 84LM9600 (CHASSIS:LC23J) Service Manual ▷ View online

FRC Board

1

FRC Processor(LG1122)

2

SPLT IC(ALTERA)

To T-Con

From Main Board

To T-Con

To T-Con

To PSU

3

Scaler IC(PA138)

4

FMT IC(ALTERA)

1

2

3

4

Block Diagram

LG1152D-B2

AUD

BB_TP_DATA

DAC_DATA

AAD_DATA

HSR_P/M

PC_AUDIO

PC_Audio L/R

PC-RGB

COMPOSITE

COMPONENT

A/V1_CVBS

Comp1 Y,Pb,Pr

PC_R,G,B,H,V

HDMI

Switch

HDMI 1(ARC)

LG1152A-B2

USB1

USB2

USB3

USB

HUB

PHY

RMII

LAN

Motion-R

M-Remote_R/TX

Audio

AMP

OPTIC

SPK

SPDIF

I2S

DDR

DDR

Flash

CHB_DATA

DTV TS

SC_CVBS_IN

SC_R/G/B 3bit

SC_L/R_IN_out

CI Slot

EB_DATA

Audio

AMP

I2S

Woofer

HDMI 2

HDMI 3

HDMI 4(MHL)

Logo Light

Built-in WiFi

LG1122

FPGA

LVDS

2Link

LVDS 4Ch

PA138

PA138

LVDS 2Chx2

PA138

FPGA

LVDS 8Ch

V by 1 8Ch.

V by 1 8Ch.

Block Diagram for Jack Interface

Earphone Block

Main Chip

SC_DET

SC_CVBS_IN

DTV/MNT_V_OUT

MUX

IC500

ATV_OUT

DTV/ATV_SELECT

SC_FB/ID_IN 2bit

SC_R/G/B 3bit

SC_L/R_IN

DSUB_R/G/B 3bit

DSUB_DET

RGB_DDC_SCL/SDA 2bit

Tuner

HP_L/ROUT

PC_L/R_IN

SPDIF_OUT

COMP_Y+/Pb+/Pr+

COMP_DET

AV_CVBS_IN

AV_L/R_IN

AV_CVBS_DET

SPDIF

PC_Audio

RGB

SCART

Block Diagram for Backlight

SoC

3D

Chip

Main

UD@60Hz

Dual-Link LVDS For Video

UD@60Hz

Dual-Link LVDS For OSD

FRC3

FPGA

PA138

PA138

FPGA

FPGA

TCON

THC

216

THC

216

THC

215

THC

215

LVDS

LVDS

LVDS

LVDS

LVDS

Vx1

Vx1

Vx1

Vx1

LVDS

LVDS

Bypass

Bypass

Vx1 to LVDS

Interface

Formatter

Interface

Formatter

Vx1 to LVDS

LVDS to Vx1

LVDS to Vx1

3840x2160

1920x2160

1920x2160

3840x1080

(1920x2160)

1920x2160

1920x2160

1920x2160

1920x2160

3840x1080

(1920x2160)

3840x1080

(1920x2160)

3840x1080

(1920x2160)

4 Ch.

2 Ch.

2 Ch.

8 Ln.

8 Ln.

8 Ch.

8 Ch.

8 Ch.

8 Ch.

8 Ln.

8 Ln.

Interface resolution

(Image resolution)

Frame

Repeater

Frame

Repeater

[

84LM96

Edge LED Backlight]

SPI/Vsync

LED BLU control

Click on the first or last page to see other 84LM9600 (CHASSIS:LC23J) service manuals if exist.