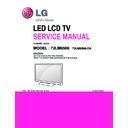

LG 72LM9500-DA (CHASSIS:LT23J) Service Manual ▷ View online

System Diagram – Focused on Digital Chip

Flexnoc ( 64 x 40 0 MHz)

AAD AFE

Demod

AFE (CHB)

AFE (1ch)

AFE (3ch)

L9A

L9D

AAD

(BTSC)

GFX

Headphone

Digital

Audio output

UART x3

I2C x12

SPI x2

DMAC

GPIO

WDG

Timer

eMMC/SD

SCI

USB x3

USB PHY

HP out

Line out

Audio L/R

LVDS RX (HS)

LVDS RX (HS)

Tuner

Audio L/R

x6 ch

Tuner

HDMI x4

DAC

SP

DIF

CVBS(CHB)

CVBS(x8ch)

HDMI RX

STP out

Sound

DSP

Speake

r

vpes

MCU

Line out

apes

Component

/RGB

LVDS TX (HS)

LVDS TX (HS)

LVDS RX (HS)

LVDS TX (HS)

DAC

CVD

SC

SRAM

SMC

CI

eMMC/SD

USB x3

DVB-CI

EB

NANDC

GEM

NAND (SLC)

RGMII/RMII

DDRC

DDR3 PHY

DDRC

DDR3 PHY

DDRC

DDR3 PHY

UART x3

I2C x9

SPI x2

SCI

GPIO

JTAG

Flex

no

c

(

64 x

40

0 MHz)

VDEC

core

VDEC

core

VDEC

MCU

SDCAS

DES

TDES

AES

DVB-CSA

SDIO

TP

I0

STP

I1

STP

I0

STP

O

TP

I1

SDCORE

2-channel

time-shared

TP engine

Download

TE

ADEC

VENC

DDR3 x16

DDR3 x16

Flex

no

c

(

64 x

40

0 MHz)

DDR3

x16

APB Br

CA9

CA9

L2 $

1MB

DVR

MAU

SDEC

MAU

ADEC

MAU

PREP

MAU

IME

HME

QME

Core

MAU

DEBLOCK

CMC

Audio

DSP

MIC

Ex

tern

al

I

2

S

DAC

ADC

ADC

DIF

SIF

DE

TP out

TP in

(CI)

STP in

(CHB)

TS

PES

DEC

PES

DEC

PES

DEC

Upload

vpes

(thumbnail)

senc

TS

- Dual-core CPU (CA9)

- Dual-core GPU (Mail400)

- Multiple MCU (x4)

- Multiple DSP (x2)

- Multiple DDR3 Channel (x3)

Audio

TS

PREP

CVD

ES

Display

CPU/GPU

ADC

PES

DEC

PESDEC

MAU

SP

ROM

MCU

OTP

Mail400

L2 $

64KB

VP

PP

PP

AHB

Scaler(R)

IPC(R)

NR(R)

Scaler(L)

IPC(L)

NR(L)

MCU

CVE

SMUX

PRE3D

MIXED IPs (Bus)

DCO

Global clock/reset/power mgt.

with PLL + DFT inside

DDR3

PLL

DDR3

PLL

DCO

Display

PLL

CPU

PLL

CRG

+DFT

CRG

+DFT

DISP

IF

ICOD

DEC

JPEG

PNG

ENC

JPEG

SPE

VLC

MAU

AUD

PLL

LVDS TX (HS)

LVDS TX (HS)

LVDS TX (HS)

L9-3D

L9-3D

L9-3D

OSD

Right

Left

PQ(L)

PQ(R)

OSD

Scaler(sub)

2Dto3D

Flex

no

c

System Diagram – Focused on Interface between Analog and Digital Chip

Dual Tuner

+ Demod for CHB

DIF

CVBS(CHB)

SIF

Parallel TS

System

Demux

TS (from GCB)

Audio DSP

Multi-STD

Audio Decoder

BTSC AFE

10b@18.432MHz

w/ PLL

1ch L/R

Audio-ADC

24b@48KHz

GBB AFE

1ch@30MHz

w/ PLL

Global Baseband

V/Q, DVB-T/C

CVBS AFE(CHB)

10b@27MHz

CVBS(6ch)

Component(2ch)

3ch Video

AFE

10b@165MHz

w/ LLPLL

PC-RGB

HDMI-Rx 1.4

(1-port PHY)

(1-port PHY)

3D, ARC, 4kx2k

HDMI(1ch)

CVD (CHB)

Capture

Block

(3CH)

(3CH)

AAD

(THAT)

Audio Codec1

(Digital Part)

Mux

Analog Chip

Digital Chip

Audio L/R (5-ch)

SW

I2S(stero)

Sound

DSP

Audio DAC

48KHz

Audio DAC

48KHz

I2S

SPDIF

Video Decoder

(

Dual HD

)

CVBS AFE(2-ch)

12b@54MHz

6+1(clk)+2(gc)

12 : CVBS

Mux

12

Diplay

Engine

MC NR,

Vertical MC IPC

Scaler, PE

OSD, VCR

LVDS

CVBS

Encoder

H.264 Encoder

SD upto 480p

12

Channel

Browser

Browser

PHY

(3-port)

USB2.0

Host (x3)

DDR3-PHY

DDR3(x16) * 3

Ethernet

MAC

MLC NAND

Controller

CPU

Dual C-A9 (1GHz)

Graphic

Engine

2D-VG / 3D Open-ES2.0

Audio

10(data)+1(en)+5(gc)

4(val, err, clk, sop)

+8 (data)

+8 (data)

I2C

I2C

6(gbb, l9da)

I2C

(Headphone)

Line out (main audio)

SCART out

Digital

Audio

Output

LVDS

LVDS

Video

LVDS

Video

OSD

LVDS

Audio PLL

w/ DCO

MIC IN (Mono)

SW

I2S (mono)

3(lrck, lrch, sck)

I2S

I2S

Video DAC

10b@27MHz

CVBS-Out

6 (data)

I2C

SW

SW

CVBS-Out

SW

3D or UD

Data bridge

1 (ARC data)

ARC

(1ch)

I2S or SPDIF

8

Audio Clocks

9

1ch mono

Audio-ADC

24b@48KHz

Audio Codec0

(Digital Part)

Mux

LVDS

interrupt

3(hdmi, 3ch, gbb)

5(gc)

3(lrck, lrch, sck)

3(lrck, lrch, sck)

3(lrck, lrch, sck)

Audio

HDMI

(1-Link)

I2S

CPU

xi_main

1 Ghz

DDR3PLL

xo_main

1.6Ghz

DDR3PLL1

1.6Ghz

24Mhz

DDR3PLL2

0

1

0

1

0

1

CT

R

R

1/2

1/5

1.6Ghz

1.6Ghz

Memory Controller

Memory Controller

Memory Controller

800Mhz

800Mhz

Video/Audio Block

CPU peripherial

dcoin_clk

DCO

DCO

200Mhz

200Mhz

Glitch-free logic

between

de_dco_out and

sdec_dco_out

de_dco_out

sdec_dco_out

0

1

CT

R

R

DISPLL

u_DPLL

udnt_buf_dpll_fin

disp_fout

Clock Divide & Reset

generation w/ test logic

DE

TE

sclk

27Mhz

27Mhz

27Mhz

27Mhz

2 port USB PHY

1 port USB PHY

30/48Mhz

30/48 Mhz

i_core800_clk

i_core320_clk

i_m01_ddrclk

i_m2_ddrclk

u_crg

Clock Divide & Reset generation

w/ test logic

Clock Divide & Reset generation

w/ test logic

Clock Divide & Reset generation

w/ test logic

Clock Divide & Reset generation

w/ test logic

Clock Divide & Reset generation

w/ test logic

USB controller

About 220 internally generated clocks

SSC setting

- 0xFD3001CC

- 0xFD3001D0

- 0xFD3001CC

- 0xFD3001D0

SSC setting

- 0xFD3001C4

- 0xFD3001D8

- 0xFD3001C4

- 0xFD3001D8

SSC setting

-0xFD300108

-0xFD30010C

-0xFD300108

-0xFD30010C

SSC setting

- 0xFD3001D4

- 0xFD3001D8

- 0xFD3001D4

- 0xFD3001D8

Click on the first or last page to see other 72LM9500-DA (CHASSIS:LT23J) service manuals if exist.