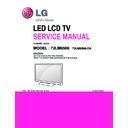

LG 72LM9500-DA (CHASSIS:LT23J) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

DDR_DATA[15]

DDR_DATA[15]

DDR_A[6]

DDR_A[12]

DDR_DATA[11]

DDR_A[13]

DDR_A[1]

DDR_A[4]

DDR_DATA[4]

DDR_DATA[6]

DDR_DATA[3]

DDR_DATA[7]

DDR_DATA[5]

DDR_DATA[12]

DDR_A[11]

DDR_DATA[0]

DDR_A[10]

DDR_DATA[7]

DDR_DATA[9]

DDR_A[2]

DDR_DATA[5]

DDR_A[3]

DDR_DATA[12]

DDR_DATA[0]

DDR_DATA[1]

DDR_A[4]

DDR_DATA[14]

DDR_A[6]

DDR_A[13]

DDR_DATA[9]

DDR_A[0]

DDR_A[12]

DDR_DATA[6]

DDR_A[9]

DDR_A[7]

DDR_A[5]

DDR_A[2]

DDR_DATA[2]

DDR_DATA[10]

DDR_DATA[8]

DDR_A[8]

DDR_DATA[8]

DDR_A[8]

DDR_A[10]

DDR_DATA[1]

DDR_DATA[10]

DDR_DATA[13]

DDR_DATA[2]

DDR_A[5]

DDR_DATA[3]

DDR_DATA[4]

DDR_DATA[13]

DDR_DATA[11]

DDR_A[3]

DDR_A[11]

DDR_DATA[14]

DDR_A[7]

DDR_A[0]

DDR_A[1]

DDR_A[9]

DDR_WEN

+0.75V_VREF_D1

DDR_A[0-13]

+0.75V_VREF_D0

DDR_RESET_N

+0.75V_VREF_M1

C9418

0.1uF

DDR_DQS[0]

R9403

240

1%

DDR_CASN

+1.5VQ

DDR_CLKN

DDR_BA[2]

H5TQ1G63DFR-PBC

IC9400

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

R9411

1K

1%

DDR_CKE

DDR_BA[2]

C9409

0.1uF

C9404

0.1uF

C9406

0.1uF

+1.5VQ

C9417

1000pF

R9407

1K

1%

DDR_RESET_N

DDR_BA[0]

+1.5VQ

R9408

1K

1%

R9409

1K

1%

+1.5V_LG1132

+1.5VQ

R9401

100 1%

C9402

0.1uF

DDR_DQS_N[0]

DDR_DM[0]

DDR_ODT

DDR_DQS[0]

C9411

0.1uF

+0.75V_VREF_M1

DDR_DQS[1]

DDR_CLKN

DDR_BA[0]

DDR_A[0-13]

DDR_DQS_N[1]

C9408

0.1uF

C9400

0.1uF

+1.5VQ

DDR_DATA[0-15]

+1.5VQ

C9421

1000pF

DDR_CLK

DDR_DM[1]

R9405

1K

1%

C9415

0.1uF

+0.75V_VREF_D0

DDR_CLK

DDR_BA[1]

R9410

1K

1%

C9412

0.1uF

OPT

C9416

0.1uF

OPT

DDR_DM[1]

DDR_CASN

C9410

1000pF

+0.75V_VREF_D1

DDR_RASN

DDR_DATA[0-15]

+0.75V_VREF_M0

+0.75V_VREF_D1

DDR_BA[1]

C9405

0.1uF

OPT

C9419

0.1uF

DDR_ODT

R9402

240

1%

C9422

1000pF

C9413

0.1uF

DDR_DQS_N[1]

DDR_CKE

+0.75V_VREF_M0

+0.75V_VREF_D0

DDR_RASN

+1.5VQ

C9403

0.1uF

DDR_DQS[1]

C9414

0.1uF

OPT

DDR_DM[0]

DDR_DQS_N[0]

C9420

0.1uF

R9406

1K

1%

+1.5VQ

+1.5VQ

DDR_WEN

R9404

1K

1%

1%

C9401

4.7uF

4.7uF

C9407

4.7uF

4.7uF

L9400

BLM18SG121TN1D

IC9300

LG1132

LG1132

DDR_A[0]

V21

DDR_A[1]

B22

DDR_A[2]

V20

DDR_A[3]

T20

DDR_A[4]

C22

DDR_A[5]

T21

DDR_A[6]

C21

DDR_A[7]

T22

DDR_A[8]

C20

DDR_A[9]

U22

DDR_A[10]

D22

DDR_A[11]

B21

DDR_A[12]

D20

DDR_A[13]

U21

DDR_A[14]

B20

DDR_DQ[0]

M22

DDR_DQ[1]

G20

DDR_DQ[2]

N20

DDR_DQ[3]

F22

DDR_DQ[4]

N22

DDR_DQ[5]

F20

DDR_DQ[6]

N21

DDR_DQ[7]

F21

DDR_DQ[8]

H21

DDR_DQ[9]

L22

DDR_DQ[10]

G22

DDR_DQ[11]

M20

DDR_DQ[12]

H22

DDR_DQ[13]

L21

DDR_DQ[14]

H20

DDR_DQ[15]

L20

DDR_CK

E22

DDR_CK_N

E21

DDR_DQS[0]

K22

DDR_DQS_N[0]

K21

DDR_DQS[1]

J22

DDR_DQS_N[1]

J21

DDR_CKE

E20

DDR_WE_N

R20

DDR_RAS_N

P20

DDR_CAS_N

P21

DDR_ODT

P22

DDR_DM[0]

G21

DDR_DM[1]

M21

DDR_BA[0]

R21

DDR_BA[1]

D21

DDR_BA[2]

R22

DDR_RST_N

U20

DDR_ZQ_CAL

A20

DDR_VREF0

V22

DDR_VREF1

A21

DDR_VDDQ_1

E19

DDR_VDDQ_2

F19

DDR_VDDQ_3

G19

DDR_VDDQ_4

H19

DDR_VDDQ_5

J19

DDR_VDDQ_6

J20

DDR_VDDQ_7

K19

DDR_VDDQ_8

K20

DDR_VDDQ_9

L19

DDR_VDDQ_10

M19

DDR_VDDQ_11

N19

DDR_VDDQ_12

P19

DDR_VDDQ_13

R19

R9400

200

LG1132 DDR3

LG1132 DDR3

2011. 06 .28

Connect A13 for

Using 2Gbit Memory

Using 2Gbit Memory

DDR0 PHY VREF

DDR3 1.5V Decaps - Place these caps near Memory

Connect A13 for

Using 2Gbit Memory

Using 2Gbit Memory

DDR3 1.5V/0.75V Decap

- Place these caps near IC101

- Place these caps near IC101

THERMAL

THERMAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+1.0VDC

+1.5V_LG1132

+1.5V_DDR

L9500

BLM18PG121SN1D

+1.0V_VDD

R9500

10K

10K

+5V_USB

2200pF

C9501

50V

+3.3V_NORMAL

C9513

10uF

10V

10uF

C9500

10V

+2.5V_LG1132

C9514

0.1uF

16V

R9501

2K

1%

2K

1%

R9502

4.3K

1%

1%

IC9500

AP7173-SPG-13 HF(DIODES)

3

VCC

2

PG

4

EN

1

IN

5

GND

6

SS

7

FB

8

OUT

9

[EP]

C9502

10uF

16V

10uF

16V

UD

L9503

3.6uH

3.6uH

UD

C9504

1uF

10V

1uF

10V

UD

L9501

BLM18PG121SN1D

UD

C9503

100pF

50V

UD

+12V

C9508

22uF

10V

10V

OPT

C9507

22uF

10V

22uF

10V

UD

IC9501

TPS54327DDAR

UD

3

VREG5

2

VFB

4

SS

1

EN

5

GND

6

SW

7

VBST

8

VIN

9

[EP]GND

C9506

0.1uF

16V

UD

POWER_ON/OFF2_3

R9504

10K

UD

C9505

3300pF

50V

3300pF

50V

UD

+1.0VDC

L9502

CIC21J501NE

NON_UD

+1.0V_VDD

R9503

11K

1%

UD

R9505

33K

1%

UD

ZD9500

5.48VTO5.76V

LG1132 POWER

LG1132 Power

2011. 06. 28

Max 2000 mA

LG1152 for 1.0V

Vout=0.8*(1+R1/R2)

1.5A

3D-Depth Analog for 2.5V

+2.5V

R2

R1

Max 600 mA

3A

Switching freq: 700K

R2

L9 CORE for 1.0V

Vout=0.765*(1+R1/R2)

R1

Max 2000 mA

READY

(UD Model only / LG1132 DDR=792Mh)

**NON UD Model

LG1132 DDR = 668Mhz

LG1152 1.0V ==> IC2306

LG1132 1.0V ==> IC2306

LG1132 1.0V ==> IC2306

LG1132 DDR = 792Mhz

LG1152 1.0V ==> IC2501

LG1132 1.1V ==> IC2306

LG1132 1.1V ==> IC2306

**UD Model

Place near USB JACK

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

C9304

0.1uF

16V

0.1uF

16V

OPT

TXDCLKN

C9318

4.7uF

10V

4.7uF

10V

+3.3V_NORMAL

TXC3N

R9318

33

TDI

TXD3N

TXA0P

TXD4N

C9353

4.7uF

10V

4.7uF

10V

L9302

BLM18SG121TN1D

TXD4P

P9300

12507WR-10L

DEBUG

1

2

3

4

5

6

7

8

9

10

11

TXC3N

TXBCLKN

TMODE1

TXA1N

SPI_SCLK

MDS62110213

M9302

OPT

TXA2P

TXB3N

R9324

10K

OPT

SPI_DO

SPI_DO

TXA1P

R9321

10K

NON_72INCH_LVDS_AB

R9328

10K

OPT

TXACLKP

R9339

100

OPT

R9313

33

TXC2N

TXB2P

TXC1N

TXB2P

+2.5V_LVDS_TX

+1.0V_PLL_VDD

L9309

BLM18SG121TN1D

R9322

10K

OPT

C9303

4.7uF

10V

4.7uF

10V

3D_DEPTH_RESET

R9325

10K

C9308

0.1uF

16V

0.1uF

16V

OPT

R9343

3.3K

XTAL_OUT

3D_DEPTH_RESET

C9330

0.1uF

16V

0.1uF

16V

C9314

0.1uF

16V

0.1uF

16V

C9321

0.1uF

16V

0.1uF

16V

OPT

TXA4P

C9323

0.1uF

16V

0.1uF

16V

OPT

+2.5V_LG1132

C9310

4.7uF

10V

4.7uF

10V

R9330

0

OPT

TXC4N

I2C_SDA2

IC9301

W25X40BVSSIG

LG1132_FLASH

3

WP

2

DO[IO1]

4

GND

1

CS

5

DI[IO0]

6

CLK

7

HOLD

8

VCC

TXC2P

TXD2N

C9300

0.1uF

16V

0.1uF

16V

OPT

TMS

TXCCLKP

TXD1N

TXACLKN

TMODE0

TMODE2

TXD1P

SPI_DI

R9332

0

OPT

TXA4P

TXA3P

3D_DEPTH_RESET

TXA0N

TXD4N

+3.3V_XTAL_AVDD

TXB1P

TXC4N

TCK

TXCCLKN

TXC1P

I2C_SDA2

TXB4P

C9357

4.7uF

10V

4.7uF

10V

TRST_N

L9304

BLM18SG121TN1D

TXBCLKN

TDO

R9345

0

OPT

SPI_CS

R9320

10K

72INCH_LVDS_CD

IC9300

LG1132

LG1132

RXA0P

AB17

RXA0N

AA17

RXA1P

Y16

RXA1N

Y17

RXA2P

AA16

RXA2N

AB16

RXACLKP

AB15

RXACLKN

AA15

RXA3P

Y14

RXA3N

Y15

RXA4P

AA14

RXA4N

AB14

RXB0P

AB13

RXB0N

AA13

RXB1P

Y12

RXB1N

Y13

RXB2P

AA12

RXB2N

AB12

RXBCLKP

AB11

RXBCLKN

AA11

RXB3P

Y10

RXB3N

Y11

RXB4P

AA10

RXB4N

AB10

RXC0P

AB9

RXC0N

AA9

RXC1P

Y8

RXC1N

Y9

RXC2P

AA8

RXC2N

AB8

RXCCLKP

AB7

RXCCLKN

AA7

RXC3P

Y6

RXC3N

Y7

RXC4P

AA6

RXC4N

AB6

RXD0P

AB5

RXD0N

AA5

RXD1P

Y4

RXD1N

Y5

RXD2P

AA4

RXD2N

AB4

RXDCLKP

AB3

RXDCLKN

AA3

RXD3P

Y2

RXD3N

Y3

RXD4P

AA2

RXD4N

AB2

UART_RXD

D3

UART_TXD

D2

SPI_SCLK

C2

SPI_CS

C1

SPI_DI

B1

SPI_DO

B2

SDA_M

E2

SCL_M

E1

SDA_S

D1

SCL_S

E3

SMODE

F2

TMODE0

F1

TMODE1

G3

TMODE2

G2

TMODE3

G1

TRST_N

H1

TDO

H3

TDI

H2

TCK

J3

TMS

J2

PORES_N

F3

XTALO

AB21

XTALI

AA21

TXA0P

A10

TXA0N

B10

TXA1P

C9

TXA1N

C10

TXA2P

B9

TXA2N

A9

TXACLKP

A8

TXACLKN

B8

TXA3P

C7

TXA3N

C8

TXA4P

B7

TXA4N

A7

TXB0P

A6

TXB0N

B6

TXB1P

C5

TXB1N

C6

TXB2P

B5

TXB2N

A5

TXBCLKP

A4

TXBCLKN

B4

TXB3P

C3

TXB3N

C4

TXB4P

B3

TXB4N

A3

TXC0P

A18

TXC0N

B18

TXC1P

C17

TXC1N

C18

TXC2P

B17

TXC2N

A17

TXCCLKP

A16

TXCCLKN

B16

TXC3P

C15

TXC3N

C16

TXC4P

B15

TXC4N

A15

TXD0P

A14

TXD0N

B14

TXD1P

C13

TXD1N

C14

TXD2P

B13

TXD2N

A13

TXDCLKP

A12

TXDCLKN

B12

TXD3P

C11

TXD3N

C12

TXD4P

B11

TXD4N

A11

GPIO[0]

Y1

GPIO[1]

W3

GPIO[2]

W2

GPIO[3]

W1

GPIO[4]

V3

GPIO[5]

V2

GPIO[6]

V1

GPIO[7]

U3

GPIO[8]

U2

GPIO[9]

U1

GPIO[10]

T3

GPIO[11]

T2

GPIO[12]

T1

GPIO[13]

R3

GPIO[14]

R2

GPIO[15]

R1

GPIO[16]

P3

GPIO[17]

P2

GPIO[18]

P1

GPIO[19]

N3

GPIO[20]

N2

GPIO[21]

N1

GPIO[22]

M3

GPIO[23]

M2

GPIO[24]

M1

GPIO[25]

L1

GPIO[26]

L2

GPIO[27]

L3

GPIO[28]

K1

GPIO[29]

K2

GPIO[30]

K3

GPIO[31]

J1

SPI_DI

SW9300

JTP-1127WEM

DEBUG

1

2

4

3

IC9300

LG1132

LG1132

VDD_1

H8

VDD_2

H9

VDD_3

H14

VDD_4

H15

VDD_5

J8

VDD_6

J15

VDD_7

K8

VDD_8

K15

VDD_9

L8

VDD_10

L15

VDD_11

M8

VDD_12

M15

VDD_13

N8

VDD_14

N15

VDD_15

P8

VDD_16

P15

VDD_17

R8

VDD_18

R9

VDD_19

R10

VDD_20

R11

VDD_21

R12

VDD_22

R13

VDD_23

R14

VDD_24

R15

VDD33_1

F4

VDD33_2

G4

VDD33_3

H4

VDD33_4

J4

VDD33_5

K4

VDD33_6

L4

VDD33_7

M4

VDD33_8

N4

VDD33_9

P4

VDD33_10

R4

VDD33_11

T4

VDD33_12

U4

LVRX_VDD25_1

W7

LVRX_VDD25_2

W8

LVRX_VDD25_3

W9

LVRX_VDD25_4

W10

LVRX_VDD25_5

W11

LVRX_VDD25_6

W12

LVRX_VDD25_7

W13

LVRX_VDD25_8

W14

LVTX_VDD10_1

H10

LVTX_VDD10_2

H11

LVTX_VDD10_3

H12

LVTX_VDD10_4

H13

LVTX_VDD25_1

D7

LVTX_VDD25_2

D8

LVTX_VDD25_3

D9

LVTX_VDD25_4

D10

LVTX_VDD25_5

D11

LVTX_VDD25_6

D12

LVTX_VDD25_7

D13

LVTX_VDD25_8

D14

LVTX_VDD25_9

D15

LVTX_VDD25_10

D16

DISP_VDD

Y21

DR3P_VDD

Y22

SSP_VDD

AA22

XTAL_VDD

Y20

DISP_AVDD

AA19

DR3P_AVDD

AA20

SSP_AVDD

AB20

XTAL_AVDD

AB19

VSS_1

A2

VSS_2

A19

VSS_3

B19

VSS_4

C19

VSS_5

D4

VSS_6

D5

VSS_7

D6

VSS_8

D17

VSS_9

D18

VSS_10

D19

VSS_11

E4

VSS_12

E5

VSS_13

E6

VSS_14

E7

VSS_15

E8

VSS_16

E9

VSS_17

E10

VSS_18

E11

VSS_19

E12

VSS_20

E13

VSS_21

E14

VSS_22

E15

VSS_23

E16

VSS_24

E17

VSS_25

E18

VSS_26

F5

VSS_27

F18

VSS_28

G5

VSS_29

G18

VSS_30

H5

VSS_31

H18

VSS_32

J5

VSS_33

J9

VSS_34

J10

VSS_35

J11

VSS_36

J12

VSS_37

J13

VSS_38

J14

VSS_39

J18

VSS_40

K5

VSS_41

K9

VSS_42

K10

VSS_43

K11

VSS_44

K12

VSS_45

K13

VSS_46

K14

VSS_47

K18

VSS_48

L5

VSS_49

L9

VSS_50

L10

VSS_51

L11

VSS_52

L12

VSS_53

L13

VSS_54

L14

VSS_55

L18

VSS_56

M5

VSS_57

M9

VSS_58

M10

VSS_59

M11

VSS_60

M12

VSS_61

M13

VSS_62

M14

VSS_63

M18

VSS_64

N5

VSS_65

N9

VSS_66

N10

VSS_67

N11

VSS_68

N12

VSS_69

N13

VSS_70

N14

VSS_71

N18

VSS_72

P5

VSS_73

P9

VSS_74

P10

VSS_75

P11

VSS_76

P12

VSS_77

P13

VSS_78

P14

VSS_79

P18

VSS_80

R5

VSS_81

R18

VSS_82

T5

VSS_83

T18

VSS_84

T19

VSS_85

U5

VSS_86

U18

VSS_87

U19

VSS_88

V4

VSS_89

V5

VSS_90

V6

VSS_91

V7

VSS_92

V8

VSS_93

V9

VSS_94

V10

VSS_95

V11

VSS_96

V12

VSS_97

V13

VSS_98

V14

VSS_99

V15

VSS_100

V16

VSS_101

V17

VSS_102

V18

VSS_103

V19

VSS_104

W4

VSS_105

W5

VSS_106

W6

VSS_107

W15

VSS_108

W16

VSS_109

W17

VSS_110

W18

VSS_111

W19

VSS_112

W20

VSS_113

W21

VSS_114

W22

VSS_115

Y18

VSS_116

Y19

VSS_117

AA1

VSS_118

AA18

VSS_119

AB18

TXB3N

TXACLKN

C9317

4.7uF

10V

4.7uF

10V

R9331

0

DEBUG

TXB1N

TXB3P

C9366

0.1uF

16V

0.1uF

16V

OPT

+1.0V_PLL_VDD

R9334

4.7K

TXC1N

R9326

10K

OPT

I2C_SCL1

TXC0N

C9333

30pF

50V

30pF

50V

TXC3P

TXC2N

C9311

10uF

10V

10uF

10V

TXD2P

C9327

0.1uF

16V

0.1uF

16V

OPT

MDS62110213

M9300

OPT

TXD3N

TMODE0

XTAL_IN

+3.3V_XTAL_AVDD

TXD3P

TXA2N

TXB0P

L9303

BLM18SG121TN1D

R9319

33

+2.5V_LVDS_RX

+1.0VDC

TXB3P

TMODE1

C9316

4.7uF

10V

4.7uF

10V

TXB2N

C9348

0.1uF

16V

0.1uF

16V

OPT

I2C_SDA2

TXD2P

TXC3P

C9361

4.7uF

10V

4.7uF

10V

TXA2N

TXBCLKP

TXC4P

TMODE3

TCK

R9340

100

OPT

+3.3V_NORMAL

R9314

33

C9363

0.1uF

16V

0.1uF

16V

TXACLKP

C9365

0.1uF

0.1uF

C9360

10uF

10V

10uF

10V

R9342

100

I2C_SCL2

SPI_DI

TXA1N

C9315

4.7uF

10V

4.7uF

10V

R9329

1M

1M

TRST_N

SMODE

TXA0N

C9301

4.7uF

10V

4.7uF

10V

+2.5V_LG1132

+2.5V_AVDD

+1.0VDC

L9300

BLM18SG121TN1D

+1.0VDC

TXC4P

TXD3P

TXC1P

R9317

33

TXD1P

TXD0P

TXD4P

C9324

0.1uF

16V

0.1uF

16V

R9327

10K

+3.3V_IO

TXCCLKP

I2C_SDA1

+2.5V_LG1132

TXA3N

C9307

4.7uF

10V

4.7uF

10V

TMODE3

TXD1N

SMODE

TMODE2

TXA3P

+3.3V_NORMAL

MDS62110213

M9301

OPT

TMODE0

TXA0P

TXD2N

+3.3V_IO

XTAL_IN

TXB1P

+3.3V_NORMAL

TXC0P

+2.5V_LVDS_TX

R9323

10K

+1.0V_PLL_VDD

+1.0VDC

TXB0N

TXB2N

+3.3V_IO

X9300

24.75MHz

4

GND_2

1

X-TAL_1

2

GND_1

3

X-TAL_2

C9352

4.7uF

10V

4.7uF

10V

R9312

33

TXA1P

+3.3V_XTAL_AVDD

SPI_CS

C9359

0.1uF

16V

0.1uF

16V

+2.5V_AVDD

C9364

0.1uF

16V

0.1uF

16V

OPT

+3.3V_NORMAL

FLASH_WP

P9301

12507WS-04L

DEBUG

1

2

3

4

5

TXCCLKN

TXD0P

SPI_SCLK

TXDCLKP

MDS62110213

M9303

OPT

R9333

0

OPT

TXC0P

SPI_DO

TXD0N

C9320

4.7uF

10V

4.7uF

10V

TXD0N

TXDCLKN

I2C_SCL2

TXA4N

R9344

0

OPT

TMS

SPI_CS

TXC0N

TDI

TXBCLKP

TXDCLKP

+2.5V_LVDS_RX

XTAL_OUT

TXB4N

L9305

BLM18SG121TN1D

TXC2P

C9356

10uF

10V

10uF

10V

TXB4N

FLASH_WP

R9338

100

OPT

TXB0N

C9339

30pF

50V

30pF

50V

TXA4N

+2.5V_LVDS_TX

TXB4P

TXB1N

C9328

0.1uF

16V

0.1uF

16V

C9322

0.1uF

16V

0.1uF

16V

OPT

TDO

R9336

100K

1/16W

R9315

33

C9319

4.7uF

10V

4.7uF

10V

R9337

33

+3.3V_IO

R9341

100

OPT

C9336

4.7uF

4.7uF

+2.5V_AVDD

+2.5V_LVDS_RX

TXA3N

SPI_SCLK

R9335

10K

OPT

C9354

0.1uF

16V

0.1uF

16V

OPT

+1.0VDC

R9316

33

C9326

0.1uF

16V

0.1uF

16V

OPT

TXB0P

+3.3V_NORMAL

I2C_SCL2

C9312

10uF

10V

10uF

10V

TXA2P

R9306

100

100

SOC_TXA3P

SOC_TXB1N

SOC_TXB1P

R9301

100

100

SOC_TXB3N

R9302

100

100

SOC_TXB4N

SOC_TXB2P

SOC_TXACLKP

SOC_TXA0P

SOC_TXB3P

SOC_TXA2P

SOC_TXA0N

R9305

100

100

R9309

100

100

R9300

100

100

R9311

100

100

SOC_TXBCLKP

SOC_TXA2N

SOC_TXACLKN

R9303

100

100

R9310

100

100

SOC_TXA3N

SOC_TXB2N

SOC_TXA1P

SOC_TXA1N

SOC_TXB0N

SOC_TXB0P

SOC_TXB4P

SOC_TXBCLKN

R9307

100

100

SOC_TXA4N

SOC_TXA4P

R9304

100

100

R9308

100

100

+1.0V_XTAL/DDR3 PLL/SS PLL/DIS PLL_VDD

+2.5V DDR PLL/SS PLL/DIS PLL AVDD Decaps

+3.3V XTAL AVDD Decaps

3D Depth

2011. 11. 28

+3.3V Power Separation

+1.0VDC Decaps

SPI FLASH(4M Bit)

TEST MODE Configuration

XTAL(24.75MHz)

System Configuration

+2.5V LVDS_RX Decaps

SPI/I2C For Aardvak Interface

LG1152 B0

Default Setting

All ’H’ = Normal Operation Mode

All ’H’ = Normal Operation Mode

LG1132 HW RESET

Monitoring Pins for

3D-Depth Interanl status

3D-Depth Interanl status

+3.3V_IO Decaps

+2.5V LVDS_TX Decaps

+1.0V Power Separation

TMODE[3:0]

0000 => System PLL Test

0001 => LVDS Rx Isolation Test

0010 => LVDS Tx Isolation Test

0011 => LVDS Bypass Test

0100 => ALL PLL Test

1001 => DDR PLL IsolationTest

1010 => Functional Test

1011 => MBIST

1100 => Scan Test(Normal)

1101 => Scan Test (Adaptive)

1110 => Display PLL Test

1111 => Normal Operation

0000 => System PLL Test

0001 => LVDS Rx Isolation Test

0010 => LVDS Tx Isolation Test

0011 => LVDS Bypass Test

0100 => ALL PLL Test

1001 => DDR PLL IsolationTest

1010 => Functional Test

1011 => MBIST

1100 => Scan Test(Normal)

1101 => Scan Test (Adaptive)

1110 => Display PLL Test

1111 => Normal Operation

For Heat Sink

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+3.5V_ST

P13002

12507WR-10L

GP4_IR_10P

1

2

3

4

5

6

7

8

9

10

11

R13011

10K

COMMERCIAL_IR_EU

D13005-*1

20V

CDS2C20GTHB

DEV_EPCOS_20V

D13000

5.6V

AMOTECH CO., LTD.

OPT

R13014

100

100

R13023

100

100

EEPROM_SDA

EEPROM_SCL

C13007

100pF

50V

R13001

1K

COMMERCIAL_IR

IR_OUT

Q13001

MMBT3904(NXP)

COMMERCIAL_IR

E

B

C

D13006

20V

ADUC 20S 02 010L

OPT

R13003

3.3K

COMMERCIAL_IR

+3.5V_ST

D13006-*1

20V

CDS2C20GTHB

DEV_EPCOS_20V

KEY2

IR

C13004

1000pF

50V

D13001

5.6V

AMOTECH CO., LTD.

OPT

R13009

1K

COMMERCIAL_IR_EU

L13000

BLM18PG121SN1D

Q13004

MMBT3904(NXP)

COMMERCIAL_IR

E

B

C

+3.5V_ST

R13000

0

0

IR_BYPASS

R13018

10K

5%

C13002

0.1uF

R13024

100

100

R13019

47K

COMMERCIAL_IR

R13007

10K

IR_BYPASS

R13004

47K

COMMERCIAL_IR

C13000

0.1uF

D13005

20V

ADUC 20S 02 010L

OPT

LED_B/GP4_LED_R

R13005

22

COMMERCIAL_IR

+3.5V_ST

+3.5V_ST

R13002

10K

COMMERCIAL_IR

R13025

1.5K

R13015

3.3K

COMMERCIAL_IR

Q13000

MMBT3904(NXP)

COMMERCIAL_IR

COMMERCIAL_IR

E

B

C

R13013

100

100

R13008

0

0

COMMERCIAL_IR_US

R13017

10K

5%

+3.5V_ST

Q13002

MMBT3904(NXP)

COMMERCIAL_IR_EU

E

B

C

D13004

5.6V

AMOTECH CO., LTD.

OPT

KEY1

+3.5V_ST

P13003

12507WR-15L

IR_15P

1

EEPROM_SCL

2

EEPROM_SDA

3

GND

4

KEY1

5

KEY2

6

3.5V

7

GND

8

LED_B/LOGO

9

IR

10

GND

11

3.3V

12

LED_R/BUZZ

13

GND

14

S/T_SCL

16

.

15

ST_SDA

D13000-*1

5.6V

ESD_MTK

ADMC 5M 02 200L

200pF

D13001-*1

5.6V

ESD_MTK

ADMC 5M 02 200L

200pF

D13004-*1

5.6V

ESD_MTK

ADMC 5M 02 200L

200pF

D13004-*2

5.6V

ESD_LG1152

ADMC 5M 02 200L

200pF

D13001-*2

5.6V

ESD_LG1152

ADMC 5M 02 200L

200pF

D13000-*2

5.6V

ESD_LG1152

ADMC 5M 02 200L

200pF

D13005-*2

20V

ADUC 20S 02 010L

ESD_MTK

10pF

D13006-*2

20V

ADUC 20S 02 010L

ESD_MTK

10pF

+3.3V_NORMAL

D13003

5.6V

CDS3C05HDMI1

L13001

BLM18PG121SN1D

S/T_SCL

C13006

0.1uF

16V

R13021

100

100

R13022

100

100

D13002

5.6V

CDS3C05HDMI1

S/T_SDA

C13005

0.1uF

16V

130

IR / KEY For LM9900

2011.10. 28

close to wafer

COMMERCIAL

RGB Sensor

COMMERCIAL

Zener Diode is

IR & KEY

Soft Touch Micom D/L

ESD for LG1152

ESD for MTK

Soft Touch Micom D/L

Click on the first or last page to see other 72LM9500-DA (CHASSIS:LT23J) service manuals if exist.