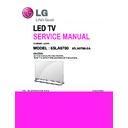

LG 65LA9700-SA (CHASSIS:LJ34N) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

TXBCLKP/TX2P

R7217

0

0

UD

TXC3N

TXB0N/TX5N

TXC2P

TXB3N/TX1N

TXBCLKN/TX2N

BPL_IN

C7201

10uF

16V

10uF

16V

OPT

R7208

0

OLED

TXA0N/TX11N

TXC0P

I2C_SDA1

TXC0N

TXA0P/TX11P

R7214

10K

10K

LVDS_BIT_SEL_LOW

TXC2N

R7204

0

OLED

TXA4P/TX6P

TXCCLKP

L7201

120-ohm

LVDS

R7215

10K

UD_OLED

TXACLKP/TX8P

TXB4N/TX0N

TXA1P/TX10P

R7209

0

OLED

TXB3P/TX1P

TXB2P/TX3P

P7202

FI-RE41S-HF-J-R1500

LVDS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

TXC4N

TXC4P

TXC1P

TXA4N/TX6N

TXC3P

T_CON_SYS_POWER_OFF

TXA2N/TX9N

TXACLKN/TX8N

TXB0P/TX5P

R7216

0

OLED

TXA2P/TX9P

TXA3P/TX7P

TXCCLKN

TXC1N

T_CON_SYS_POWER_OFF

P7201

FI-RE51S-HF-J-R1500

LVDS

1

NC

2

NC

3

NC

4

NC

5

NC

6

NC

7

LVDS_SEL

8

NC

9

NC

10

L/DIM_ENABLE

11

GND

12

RA0N

13

RA0P

14

RA1N

15

RA1P

16

RA2N

17

RA2P

18

GND

19

RACLKN

20

RACLKP

21

GND

22

RA3N

23

RA3P

24

RA4N

25

RA4P

26

GND

27

BIT_SEL

28

RB0N

29

RB0P

30

RB1N

31

RB1P

32

RB2N

33

RB2P

34

GND

35

RBCLKN

36

RBCLKP

37

GND

38

RB3N

39

RB3P

40

RB4N

41

RB4P

42

GND

43

GND

44

GND

45

GND

46

GND

47

NC

48

VLCD

49

VLCD

50

VLCD

51

VLCD

52

GND

PA168_RESET

TXA3N/TX7N

R7213

0

ALEF

TXB1N/TX4N

TXB1P/TX4P

TXB4P/TX0P

I2C_SCL1

LED_R

C7203

0.1uF

16V

0.1uF

16V

LVDS

TXB2N/TX3N

FRC_FLASH_WP

INV_CTL

PANEL_VCC

TXA1N/TX10N

TXA1N

TXB2P

TXA4P

TXB2N

TXB1P

TXACLKN

TXA1P

TXB0P

TXB1N

TXA4N

TXACLKP

TXB0N

R7201 0

UD_CPBOX

I2C_SCL1

R7200 0

UD_CPBOX

I2C_SDA1

URSA7_RESET

FRC_DONE

R7202

0

UD

R7203

0

UD

R7205

0

UD

LVDS INTERFACE

[41Pin LVDS OUTPUT Connector]

[51Pin LVDS OUTPUT Connector]

BIT_SEL

LVDS

TXD3N/TX13N

TXD2P/TX15P

TXD0N/TX17N

TXD1P/TX16P

TXD2N/TX15N

TXD3P/TX13P

TXD4P/TX12P

TXDCLKN/TX14N

TXD4N/TX12N

TXD1N/TX16N

TXDCLKP/TX14P

TXD0P/TX17P

H13 BALL NAME

BSD-NC4_H072-HD

2012-10-15

OLED : FRC_RESET = LVDS_VAL

INV_CTL = ELVDD_ON

INV_CTL = ELVDD_ON

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

D13_SPI_DO_M

D13_SPI_SCLK_M

D13_SPI_DI_M

D13_HDMI_TX0N

D13_HDMI_TX0P

D13_HDMI_TX1N

D13_HDMI_TX1P

D13_HDMI_TXCN

D13_HDMI_TXCP

D13_HDMI_TX2N

D13_HDMI_TX2P

D13_STPO_CLK

D13_STPO_SOP

D13_STPO_VAL

D13_STPO_ERR

D13_STPO_DATA

XTAL_OUT

XTAL_IN

R12007

1M

1M

XTAL_OUT

XTAL_IN

SPI_DL_MODE

+3.3V_NORMAL

3.3K

R12016

D13_TDO_1

D13_TDI_1

P12000

12507WS-08L

HEVC_DEBUG

1

2

3

4

5

6

7

8

9

+3.3V_NORMAL

D13_TRST_N_1

C12001

0.1uF

16V

0.1uF

16V

HEVC_DEBUG

R12004

33

HEVC_DEBUG

R12003

33

HEVC_DEBUG

R12002

33

HEVC_DEBUG

R12000

33

HEVC_DEBUG

R12001

33

HEVC_DEBUG

D13_TCK_1

D13_TMS_1

D13_UART_RX_1

D13_UART_TX_1

P12001

12507WS-04L

HEVC_DEBUG

1

2

3

4

5

+3.3V_NORMAL

R12006

33

HEVC_DEBUG

R12005

33

HEVC_DEBUG

C12002

0.1uF

16V

0.1uF

16V

HEVC_DEBUG

D13_SPI_CS/GPIO[0]

R12018

10K

10K

OPT

R12015

0

0

1/16W

5%

5%

D13_SPI_DO_M

D13_SPI_DI_M

C12005

0.1uF

0.1uF

D13_FLASH_WP

D13_SPI_SCLK_M

R12032

3.3K

R12017

10K

IC12001

MX25L3206EM2I-12G

3

WP#

2

SO/SIO1

4

GND

1

CS#

5

SI/SIO0

6

SCLK

7

HOLD#

8

VCC

R12019

33

+3.3V_NORMAL

D13_SPI_CS/GPIO[0]

R12010

10K

+3.3V_NORMAL

R12011

10K

OPT

D13_UART_RX_1

D13_UART_RX_0

D13_UART_TX_1

D13_UART_TX_0

D13_TMS_1

D13_TCK_0

D13_TCK_1

D13_TMS_0

D13_TDI_0

D13_TDI_1

D13_TRST_N_0

D13_TDO_0

D13_TRST_N_1

D13_TDO_1

R12027

33

R12026

33

R12025

33

SOC_SPI0_MOSI

SOC_SPI0_MISO

D13_TMS_0

D13_TDI_0

D13_TCK_0

D13_TRST_N_0

D13_TDO_0

D13_UART_TX_0

D13_UART_RX_0

R12037

1.6K 1%

D13_HDMI_DDC_DA

D13_HDMI_HPD

D13_HDMI_DDC_CK

R12024

33

SOC_SPI0_SCLK

SOC_SPI0_CS0

R12028

33

OPT

R12030

33

OPT

I2C_SCL2

R12029

33

OPT

R12031

33

OPT

I2C_SDA2

D13_SPI_CS/GPIO[0]

C12004

0.01uF

D13_FLASH_WP

I2C_SDA2

D13_SPI_SCLK_M

R12046

0

HEVC_DEBUG

+3.3V_NORMAL

R12039

0

HEVC_DEBUG

I2C_SCL2

R12043

1K

HEVC_DEBUG

R12038

0

HEVC_DEBUG

D13_SPI_DI_M

R12042

0

HEVC_DEBUG

P12002

12507WS-10L

HEVC_DEBUG

1

2

3

4

5

6

7

8

9

10

11

R12044

0

OPT

R12040

0

HEVC_DEBUG

R12047

0

HEVC_DEBUG

R12041

0

HEVC_DEBUG

SPI_DL_MODE

R12045

0

OPT

D13_SPI_CS/GPIO[0]

D13_SPI_DO_M

D13_FLASH_WP

X12000

24.75MHz

4

GND_2

1

X-TAL_1

2

GND_1

3

X-TAL_2

C12003

27pF

50V

27pF

50V

C12000

27pF

50V

27pF

50V

D13_RESET

R12008

33

R12012

33

R12022

33

R12023

33

R12033

33

C12261

10pF

10pF

R12014

33

D13_SMODE[0]

D13_SMODE[1]

R12013

10K

+3.3V_NORMAL

R12021

10K

R12009

10K

OPT

D13_SMODE[1]

+3.3V_NORMAL

D13_SMODE[0]

R12020

10K

OPT

+3.3V_NORMAL

R12034

3.3K

R12035

3.3K

R12036

3.3K

OPT

R12048

3.3K

D13_INT

R12049

10

10

33

R12050

R12051

33

IC12000

LG1153

HEVC

XTALI

R2

XTALO

R1

PORES_N

A18

TRST_N0

E1

TMS0

C3

TCK0

D1

TDI0

B1

TDO0

D3

TRST_N1

E2

TMS1

B3

TCK1

D2

TDI1

B2

TDO1

C2

UART_RXD0

B10

UART_TXD0

A10

UART_RXD1

B9

UART_TXD1

A9

SPI_SCLK_S

C20

SPI_CS_S

D20

SPI_DO_S

D19

SPI_DI_S

C19

SPI_SCLK_M

A14

SPI_CS_M

B14

SPI_DO_M

B13

SPI_DI_M

A13

SCL_S

A11

SDA_S

B11

SCL_M

A12

SDA_M

B12

STPI_CLK

G20

STPI_SOP

H19

STPI_VAL

G19

STPI_ERR

H20

STPI_DATA[0]

J19

STPI_DATA[1]

J20

STPI_DATA[2]

K19

STPI_DATA[3]

K20

STPI_DATA[4]

L19

STPI_DATA[5]

L20

STPI_DATA[6]

M19

STPI_DATA[7]

M20

GPIO[7]

B7

GPIO[6]

A7

GPIO[5]

B6

GPIO[4]

A6

GPIO[3]

B5

GPIO[2]

A5

GPIO[1]

B4

GPIO[0]

A4

HDMI_DDC_CK

G1

HDMI_DDC_DA

G2

HDMI_HPD

J2

HDMI_REXT

J1

HDMI_CEC

H2

HDMI_DDCCEC

H1

HDMI_TX0N

M1

HDMI_TX0P

M2

HDMI_TX1N

L1

HDMI_TX1P

L2

HDMI_TX2N

K1

HDMI_TX2P

K2

HDMI_TXCN

N1

HDMI_TXCP

N2

SMODE[0]

F2

SMODE[1]

E3

TMODE[0]

A16

TMODE[1]

B16

TMODE[2]

A17

TMODE[3]

B17

XTAL(24.75MHz)

JTAG for HEVC

UART For HEVC

Write Protection

- HIGH : Normal Operation

- LOW : Write Protection

- HIGH : Normal Operation

- LOW : Write Protection

SPI FLASH(4MByte)

GPIO[0]

- 1 : Serial Flash Boot

- 0 : Live Boot

- 1 : Serial Flash Boot

- 0 : Live Boot

Closed to D13

Serial Flash Boot Test

HEVC option sheet

SMODE[1:0]

- 00 : Normal Mode

- Other : Test Mode

- 00 : Normal Mode

- Other : Test Mode

H/W Option : default low

SPI Clock Frq. &

DDR density

(High:512MB, LOW:256MB)

SPI Clock Frq. &

DDR density

(High:512MB, LOW:256MB)

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

D13_DDR_A[12]

D13_DDR_A[11]

D13_DDR_A[10]

D13_DDR_A[9]

D13_DDR_A[8]

D13_DDR_A[7]

D13_DDR_A[6]

D13_DDR_A[5]

D13_DDR_A[4]

D13_DDR_A[3]

D13_DDR_A[2]

D13_DDR_A[1]

D13_DDR_A[0]

D13_DDR_A[0]

D13_DDR_A[1]

D13_DDR_A[2]

D13_DDR_A[3]

D13_DDR_A[4]

D13_DDR_A[5]

D13_DDR_A[6]

D13_DDR_A[7]

D13_DDR_A[8]

D13_DDR_A[9]

D13_DDR_A[10]

D13_DDR_A[11]

D13_DDR_A[12]

D13_DDR_A[0]

D13_DDR_A[1]

D13_DDR_A[2]

D13_DDR_A[3]

D13_DDR_A[4]

D13_DDR_A[5]

D13_DDR_A[6]

D13_DDR_A[7]

D13_DDR_A[8]

D13_DDR_A[9]

D13_DDR_A[10]

D13_DDR_A[11]

D13_DDR_A[12]

D13_DDR_DQ[15]

D13_DDR_DQ[14]

D13_DDR_DQ[13]

D13_DDR_DQ[12]

D13_DDR_DQ[11]

D13_DDR_DQ[10]

D13_DDR_DQ[9]

D13_DDR_DQ[8]

D13_DDR_DQ[7]

D13_DDR_DQ[6]

D13_DDR_DQ[5]

D13_DDR_DQ[4]

D13_DDR_DQ[3]

D13_DDR_DQ[2]

D13_DDR_DQ[1]

D13_DDR_DQ[0]

D13_DDR_DQ[0]

D13_DDR_DQ[1]

D13_DDR_DQ[2]

D13_DDR_DQ[3]

D13_DDR_DQ[4]

D13_DDR_DQ[5]

D13_DDR_DQ[6]

D13_DDR_DQ[7]

D13_DDR_DQ[8]

D13_DDR_DQ[9]

D13_DDR_DQ[10]

D13_DDR_DQ[11]

D13_DDR_DQ[12]

D13_DDR_DQ[13]

D13_DDR_DQ[14]

D13_DDR_DQ[15]

D13_DDR_DQ[16]

D13_DDR_DQ[17]

D13_DDR_DQ[18]

D13_DDR_DQ[19]

D13_DDR_DQ[20]

D13_DDR_DQ[21]

D13_DDR_DQ[22]

D13_DDR_DQ[23]

D13_DDR_DQ[24]

D13_DDR_DQ[25]

D13_DDR_DQ[26]

D13_DDR_DQ[27]

D13_DDR_DQ[28]

D13_DDR_DQ[29]

D13_DDR_DQ[30]

D13_DDR_DQ[31]

D13_DDR_DQ[18]

D13_DDR_DQ[19]

D13_DDR_DQ[20]

D13_DDR_DQ[21]

D13_DDR_DQ[22]

D13_DDR_DQ[23]

D13_DDR_DQ[24]

D13_DDR_DQ[25]

D13_DDR_DQ[26]

D13_DDR_DQ[27]

D13_DDR_DQ[28]

D13_DDR_DQ[29]

D13_DDR_DQ[30]

D13_DDR_DQ[31]

D13_DDR_DQ[17]

D13_DDR_DQ[16]

D13_DDR_A[13]

D13_DDR_A[13]

D13_DDR_A[13]

D13_DDR_DQ[0-15]

D13_DDR_DQS[0]

D13_DDR_DQ[0-15]

D13_DDR_DQ[16-31]

D13_DDR_A[0-13]

D13_DDR_DQS[0]

D13_DDR_DQS[1]

D13_DDR_DQS[1]

D13_DDR_DQS[2]

D13_DDR_DQS[2]

D13_DDR_DQS[3]

D13_DDR_DQS[3]

D13_DDR_DQS[1]

D13_DDR_DQS[1]

D13_DDR_DQS[0]

D13_DDR_DQS[0]

D13_DDR_DQS[2]

D13_DDR_DQS[3]

D13_DDR_DQS[2]

D13_DDR_DQS[3]

D13_DDR_BA[0]

D13_DDR_BA[1]

D13_DDR_BA[2]

D13_D1_CLK

D13_D1_CLK

D13_D0_CLK

D13_D0_CLK

D13_DDR_CKE

D13_DDR_RAS

D13_DDR_WE

D13_DDR_ODT

D13_DDR_CAS

D13_DDR_RESET

D13_DDR_DM[1]

D13_DDR_DM[3]

D13_DDR_DM[0]

D13_DDR_DM[2]

D13_DDR_BA[0]

D13_DDR_BA[1]

D13_DDR_BA[2]

D13_D0_CLK

D13_DDR_CKE

D13_D0_CLK

D13_DDR_RAS

D13_DDR_ODT

D13_DDR_CAS

D13_DDR_RESET

D13_DDR_WE

D13_DDR_DM[0]

D13_DDR_DM[1]

D13_D1_CLK

D13_DDR_RESET

D13_D1_CLK

D13_DDR_BA[0]

D13_DDR_ODT

D13_DDR_WE

D13_DDR_BA[2]

D13_DDR_BA[1]

D13_DDR_CKE

D13_DDR_RAS

D13_DDR_CAS

D13_DDR_DM[2]

D13_DDR_DM[3]

D13_DDR_DQ[16-31]

D13_DDR_A[0-13]

D13_DDR_A[0-13]

R12100

240

240

1%

R12114

240

240

1%

R12109

240

240

1%

C12100

0.1uF

R12104

1K

1%

D13_D1_CLK

R12108

10K

C12102

0.1uF

R12105

1K

1%

R12112

1K

1%

R12101

100

R12111

1K

1%

R12110

1K

1%

D13_D0_CLK

VDDC15_D13_DDR

C12101

0.1uF

R12107

1K

1%

R12106

1K

1%

C12103

0.1uF

D13_D1_CLK

D13_DDR_CKE

D13_D0_CLK

D13_DDR_RESET

R12102

10K

R12103

100

R12113

1K

1%

D13_DDR0_VREFCA

D13_DDR0_VREFDQ

D13_DDR1_VREFCA

D13_DDR1_VREFDQ

VDDC15_D13_DDR

VDDC15_D13_DDR

C12104

0.1uF

C12105

0.1uF

C12106

0.1uF

C12107

0.1uF

D13_DDR1_VREFDQ

VDDC15_D13_DDR

D13_DDR1_VREFCA

VDDC15_D13_DDR

D13_DDR0_VREFDQ

VDDC15_D13_DDR

D13_DDR0_VREFCA

VDDC15_D13_DDR

H5TQ2G63DFR-PBC

IC12100

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

H5TQ2G63DFR-PBC

IC12101

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

IC12000

LG1153

HEVC

DDR_A[0]

T11

DDR_A[1]

T13

DDR_A[2]

T9

DDR_A[3]

T7

DDR_A[4]

U16

DDR_A[5]

U8

DDR_A[6]

U15

DDR_A[7]

T8

DDR_A[8]

T15

DDR_A[9]

T10

DDR_A[10]

U17

DDR_A[11]

U14

DDR_A[12]

U13

DDR_A[13]

U10

DDR_A[14]

T14

DDR_A[15]

T12

DDR_BA[0]

U7

DDR_BA[1]

T16

DDR_BA[2]

U11

DDR_U_CK

V15

DDR_U_CK_N

W15

DDR_D_CK

V6

DDR_D_CK_N

W6

DDR_CKE

U12

DDR_ODT

T5

DDR_RAS_N

U5

DDR_CAS_N

U6

DDR_WE_N

T6

DDR_RST_N

U9

DDR_ZQ_CALIB

T17

DDR_DQS[0]

W5

DDR_DQS_N[0]

V5

DDR_DQS[1]

W7

DDR_DQS_N[1]

Y7

DDR_DQS[2]

W14

DDR_DQS_N[2]

V14

DDR_DQS[3]

W16

DDR_DQS_N[3]

Y16

DDR_DM[0]

Y8

DDR_DM[1]

Y5

DDR_DM[2]

Y17

DDR_DM[3]

Y14

DDR_DQ[0]

W3

DDR_DQ[1]

W10

DDR_DQ[2]

V2

DDR_DQ[3]

V9

DDR_DQ[4]

Y2

DDR_DQ[5]

Y10

DDR_DQ[6]

W2

DDR_DQ[7]

V10

DDR_DQ[8]

W9

DDR_DQ[9]

W4

DDR_DQ[10]

V8

DDR_DQ[11]

V3

DDR_DQ[12]

V7

DDR_DQ[13]

Y4

DDR_DQ[14]

W8

DDR_DQ[15]

V4

DDR_DQ[16]

W12

DDR_DQ[17]

V18

DDR_DQ[18]

V11

DDR_DQ[19]

W19

DDR_DQ[20]

Y11

DDR_DQ[21]

Y19

DDR_DQ[22]

W11

DDR_DQ[23]

V19

DDR_DQ[24]

W18

DDR_DQ[25]

W13

DDR_DQ[26]

V17

DDR_DQ[27]

V12

DDR_DQ[28]

V16

DDR_DQ[29]

Y13

DDR_DQ[30]

W17

DDR_DQ[31]

V13

HEVC option sheet

Click on the first or last page to see other 65LA9700-SA (CHASSIS:LJ34N) service manuals if exist.