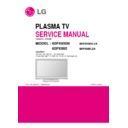

LG 60PX950N-ZA / 60PX960-ZA (CHASSIS:PD02D) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

DVB-CI SLOT

10/01

BCM3556-C0

CI_A[10]

CI_A[8]

CI_D[1]

CI_A[6]

CI_A[2]

CI_D[4]

CI_A[11]

FE_TS_DATA[4]

FE_TS_DATA[1]

CI_A[9]

CI_D[7]

CI_OUTDATA[7]

FE_TS_DATA[0]

FE_TS_DATA[5]

CI_OUTDATA[6]

CI_A[1]

CI_OUTCLK

CI_A[13]

CI_A[5]

FE_TS_DATA[6]

CI_OUTDATA[5]

FE_TS_DATA[3]

CI_A[5]

CI_A[3]

CI_D[5]

CI_A[12]

NAND_DATA[4]

NAND_DATA[7]

CI_A[4]

CI_A[6]

CI_D[0]

NAND_DATA[5]

CI_A[0]

CI_A[12]

CI_A[3]

CI_OUTVALID

CI_A[7]

CI_OUTDATA[4]

NAND_DATA[1]

CI_A[13]

NAND_DATA[0]

CI_A[10]

CI_OUTDATA[3]

FE_TS_DATA[2]

CI_A[8]

CI_OUTDATA[1]

CI_D[5]

CI_D[6]

CI_A[2]

CI_D[4]

NAND_DATA[2]

NAND_DATA[3]

CI_OUTDATA[0]

CI_D[0]

CI_A[0]

CI_A[4]

NAND_DATA[6]

FE_TS_DATA[7]

CI_D[3]

CI_OUTDATA[2]

CI_A[1]

CI_D[2]

CI_D[2]

CI_A[7]

CI_A[9]

CI_D[6]

CI_D[3]

CI_D[7]

CI_A[14]

CI_OUTSTART

CI_D[1]

CI_A[11]

CI_A[14]

C1301

0.1uF

16V

EBI_RW

007:E6

/CI_INPACK

016:O9

AR1302

10K

10K

R1313

10K

10K

AR1312

33

/CI_WAIT

007:E6;016:S10

/CI_IOWR

016:T12

R1300

47

/CI_CD1

007:H6;016:AJ3

/CI_CD2

007:H5;016:S7

R1310

100

C1305

0.1uF

0.1uF

R1301

47

EBI_CS

007:E7;007:E6;016:K26

R1314

22K

+5V_CI

FE_TS_DATA[0-7]

R1306

100

READY

R1319

10K

READY

/CI_CE1

016:G13;016:H26

AR1311

33

/CI_SEL 007:H5

P1300

10067972-000LF

G1

G2

57

21

52

16

10

47

41

5

36

59

23

45

54

18

49

43

13

7

38

2

25

56

20

51

15

9

46

40

4

35

58

22

53

17

11

48

42

12

6

37

1

24

55

19

50

44

14

8

39

3

26

60

27

61

28

62

29

63

30

64

31

32

33

34

65

66

67

68

69

/CI_OE

/CI_CE1

CI_A[0-14]

R1302

47

/CI_CE2

016:H25;016:T13

/CI_IOWR

016:H25

/CI_VS1

016:T13

FE_TS_SYNC

/CI_CD1

007:H6;016:S15

CI_D[0-7]

016:F16

IC1300

MC74LCX541DTR2G

3

D1

2

D0

4

D2

1

OE1

6

D4

5

D3

7

D5

8

D6

9

D7

10

GND

11

O7

12

O6

13

O5

14

O4

15

O3

16

O2

17

O1

18

O0

19

OE2

20

VCC

+5V_CI_Vs

NAND_RE

007:C3;007:E6

NAND_ALE

007:C2;007:E6

/CI_CE2

016:T13;016:AJ2

/CI_VS1

[GP26] 016:AJ3

NAND_WE

007:C2;007:E5

NAND_DATA[0-7]

CI_A[0-14]

007:E7;016:C13

AR1307

33

R1325

10K

READY

IC1301

74LVC245A

3

A1

2

A0

4

A2

1

DIR

6

A4

5

A3

7

A5

8

A6

9

A7

10

GND

11

B7

12

B6

13

B5

14

B4

15

B3

16

B2

17

B1

18

B0

19

OE

20

VCC

Q1301

RSR025P03

S

D

G

/CI_INPACK

016:AL9

AR1306

33

CI_OUTCLK,CI_OUTDATA[0-7],CI_OUTSTART,CI_OUTVALID

AR1317

33

R1322

10K

/CI_IORD

016:T13

C1304

0.1uF

+3.3V_MULTI

/CI_WE

+3.3V_MULTI

R1315

10K

READY

AR1314

33

Q1300

2SC3052

2SC3052

E

B

C

R1320

10K

AR1309

33

/CI_OE

016:G13

R1303

10K

/CI_IORD

016:H24

+3.3V_MULTI

CI_OUTCLK

007:H5;016:V14

R1323

10K

READY

/CI_CE2

016:H25;016:AJ2

AR1313

33

C1303

0.1uF

R1317

10K

READY

C1300

0.1uF

16V

/CI_CD2

007:H5;016:AJ2

[GP38]

C1302

0.1uF

R1321

10K

AR1310

33

R1304

100

READY

FE_TS_VAL_ERR

AR1316

33

/CI_IREQ

007:H5;016:G11

/CI_CE1

016:G13;016:AJ2

R1324

10K

READY

/CI_IREQ

[GP39]

007:H5;016:AJ3

/CI_WE

016:H12

AR1305

33

AR1315

33

AR1303

10K

10K

EBI_CS

007:E7;007:E6;016:AL23

C1306

0.1uF

16V

16V

AR1304

33

/CI_WAIT 007:E6;016:AJ3

CI_D[0-7]

016:AG22

/CI_IOIS16

[GP41]

016:AJ3

CI_5V_CTL

[GP27]

007:H7

AR1300

10K

10K

EBI_WE

007:E6

CI_MOD_RESET [GP49]

007:G6;016:AJ2

R1307

100

READY

AR1301

10K

10K

+5V_CI_Vs

CI_MOD_RESET

007:G6;016:S10

/CI_IOIS16

016:I8

R1311

47

R1309

100

C1307

0.1uF

16V

R

1

3

1

8

2

2

K

+5V_CI

R1312

10K

R1316

10K

FE_TS_DATA_CLK

C1309

4.7uF

10V

4.7uF

10V

READY

C1310

0.1uF

16V

16V

C1308

22uF

10V

10V

IC1302

NL17SZ08DFT2G

READY

3

GND

2

IN_A

4

OUT_Y

1

IN_B

5

VCC

FE_TS_VAL

FE_TS_ERR

GND

C1311

0.1uF

16V

READY

FE_TS_VAL_ERR

+3.3V_MULTI

R1305

0

R1308

0

R1327

0

READY

R1326

0

5 13

DVB-CI SLOT

Option For External Demod.

DVB-CI PULL-DOWN (Near CI Slot)

DVB-CI PULL-UP (Near CI Slot)

CI POWER ENABLE CONTROL

CI CONTROL BUFFER

External Demod.

DVB-CI DETECT

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

R120

100

RA2-

C102

0.1uF

50V

0.1uF

50V

R122

100

RD1+

RCLK1-

RD2+

RB1-

/3D_FPGA_RESET

RC2+

R111

100

RA2+

R113

100

RE1-

RCLK1+

R103

0

C101

10uF

16V

10uF

16V

RE2-

R115

100

RB1+

RCLK2-

R117

100

RB2-

R119

100

R121

100

RE1+

RE2+

RC1-

RCLK2+

RA1-

RB2+

R112

100

R114

100

RD1-

RC1+

RD2-

R116

100

C103

100pF

50V

100pF

50V

RA1+

RC2-

R118

100

+5V

PC_SER_CLK

R101

0

R102

0

R104

0

PC_SER_DATA

SCL3_3.3V

R105

0

R106

0

R107

0

DISP_EN

SDA3_3.3V

MOD_ROM_TX

MOD_ROM_RX

R108

0

3D_SYNC_OUT

R123

0

R124

0

TCK

TDI

P104

YFDW254-10S

1

2

3

4

5

6

7

8

9

10

2V5

R130

22

R128

1K

R125

22

C125

0.1uF

16V

R126

1K

TMS

R129

1K

R127

22

TDO

R131

22

TB2-

TA2+

TD3+

TC3+

TA4-

TD4-

TB1+

TB4+

TCLK4-

TCLK4+

TCLK2-

TB3+

TB1-

TE2+

TE2-

TD1-

TA1+

TB3-

TC3-

TB2+

TD2-

TD4+

TC1+

TCLK3-

TE3-

TCLK3+

TA4+

TC4-

TD2+

TD1+

TE4+

TE3+

TCLK2+

TE1-

TA2-

TC4+

TA1-

TC2+

TE1+

TA3-

TE4-

TD3-

TCLK1+

TA3+

TCLK1-

TB4-

TC2-

TC1-

PC_SER_CLK

PC_SER_DATA

DISP_EN

R850

0

R849

4.7K

2N7002(F)

Q800

G

D

S

R846

4.7K

2N7002(F)

Q801

G

D

S

R851

4.7K

R847

0

R848

4.7K

SDA3_3.3V

SCL3_3.3V

TRE2-

C901

0.1uF

16V

0.1uF

16V

TCLK3-

TE2+

MSEL[3]

TB1+

TE4-

TRB2-

DATA0

TC3+

TRA2-

TC2+

TCLK1+

TA1+

TCLK2+

/CE

TRCLK2-

SCL3_3.3V

TMS

TB3-

TB3+

1V2

TD4+

TRD2+

TA2-

TC4+

TRE2+

1V2

1V2

SDA3_3.3V

TD3-

TRD2-

TCLK1-

TRE1-

TDO

TD4-

TRB1+

TC1+

TB2+

2V5

TE1-

TRD1-

TB4+

TE3+

TCK

TA1-

C902

0.1uF

16V

0.1uF

16V

TB4-

TCLK4+

TRA1-

TB2-

TA3-

TD3+

TB1-

TRA1+

TC2-

TRB1-

MSEL[2]

TDI

TRC1+

R4059

0

READY

TE4+

CONFIG_DONE

TC4-

2V5

2V5

1V2

TRCLK1-

TCLK4-

DCLK

TRA2+

TRD1+

TCLK2-

C904

0.1uF

16V

0.1uF

16V

/STATUS

C905

0.1uF

16V

0.1uF

16V

TRCLK2+

C908

0.1uF

16V

0.1uF

16V

TD1+

TA4+

TA3+

C906

0.1uF

16V

TA2+

TC1-

TRC2-

ASDO

MSEL[0]

TRC1-

TE3-

TD2-

2V5

SYSCLK

TCLK3+

TC3-

TE1+

TD1-

TRE1+

C907

0.1uF

16V

0.1uF

16V

MSEL[1]

C903

0.1uF

16V

0.1uF

16V

/CONFIG

/3D_FPGA_RESET

TE2-

TRC2+

/CSO

TD2+

TRB2+

TRCLK1+

TA4-

3D_SYNC_OUT

X901

54.0000MHz

4

VDD

1

TRISTATE/OPEN

2

GND

3

OUTPUT

R944

10K

R949

22

22

C909

0.1uF

16V

0.1uF

16V

SYSCLK

R950

10K

10K

/STATUS

R951

10K

10K

2V5

/CE

CONFIG_DONE

R952

10K

10K

R953

1K

1K

/CONFIG

DCLK

R964

22

22

L902

BLM18PG121SN1D

C920

100pF

50V

100pF

50V

C919

0.1uF

16V

0.1uF

16V

R968

22

22

ASDO

/CSO

C917

10uF

16V

10uF

16V

R967

22

22

IC904

EPCS16SI8N_

3

VCC

2

DATA

4

GND

1

NCS

5

ASDI

6

DCLK

7

VCC_1

8

VCC_2

C921

10pF

10pF

DATA0

2V5

R965

27

27

AR901

22

1/16W

2V5

R987

0

OPT

R982

0

OPT

R988

0

MSEL[3]

MSEL[0]

MSEL[2]

MSEL[1]

R984

0

OPT

3V3

3V3

L/R_DETECT

MOD_ROM_TX

MOD_ROM_RX

R704

0

R705

0

R702

0

R703

0

R701

0

R700

0

L/R_DETECT

3V3

R4060

22

22

R4061

22

22

R4062

22

22

R4063

22

22

P101

FI-R51S-HF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

R141

100

R142

100

R143

100

R144

100

R145

100

R146

100

R147

100

R148

100

R149

100

R150

100

R151

100

R152

100

P2001

104060-8017

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

3D_SYNC_OUT

E_TDI

E_TMS

E_TDO

E_TCK

R161

22

TCK_FLASH

E_TCK

R159

2K

Q151

FDV301N

G

D

S

R160

4.7K

2V5

R158

5.6K

OPT

R157

0

R162

0

Q152

FDV301N

G

D

S

R163

5.6K

OPT

R166

22

2V5

TDO_FLASH

E_TDO

R164

2K

R165

4.7K

R169

2K

Q153

FDV301N

G

D

S

R168

5.6K

OPT

TMS_FLASH

2V5

E_TMS

R167

0

R171

22

R170

4.7K

R172

0

R174

2K

R176

22

Q154

FDV301N

G

D

S

2V5

R175

4.7K

E_TDI

R173

5.6K

OPT

TDI_FLASH

3V3

3V3

3V3

3V3

R986

0

R983

0

R985

0

R989

0

OPT

3V3

L151

BLM18PG121SN1D

OPT

R153

0

0

TMS_FLASH

R154

0

0

TDI_FLASH

R155

0

0

TCK_FLASH

R156

0

0

TDO_FLASH

FPGA_D/L

2V5

R181

4.7K

FPGA_D/L

R178

10K

R179

10K

R182

22

22

Q156

2SC3052

2SC3052

E

B

C

R180

10K

Q155

2SC3052

2SC3052

E

B

C

R183

0

R185

4.7K

R184

10K

2V5

/CE

Q157

2SC3052

2SC3052

E

B

C

R186

22

/CONFIG

3V3

IC1000

EP3C55F484C6N_SHRINK

A11

B8_IO[0]

B11

B8_IO[1]

D10

B8_IO[2]

E10

B8_IO[3]

A10

B8_IO[4]

B10

B8_IO[5]

A9

B8_IO[6]

B9

B8_IO[7]

C10

B8_IO[8]

G11

B8_IO[9]

A8

B8_IO[10]

B8

B8_IO[11]

A7

B8_IO[12]

B7

B8_IO[13]

A6

B8_IO[14]

B6

B8_IO[15]

E9

B8_IO[16]

C8

B8_IO[17]

C7

B8_IO[18]

D8

B8_IO[19]

E8

B8_IO[20]

A5

B8_IO[21]

B5

B8_IO[22]

G10

B8_IO[23]

F10

B8_IO[24]

C6

B8_IO[25]

D7

B8_IO[26]

A4

B8_IO[27]

B4

B8_IO[28]

F8

B8_IO[29]

G8

B8_IO[30]

A3

B8_IO[31]

B3

B8_IO[32]

D6

B8_IO[33]

E7

B8_IO[34]

C3

B8_IO[35]

C4

B8_IO[36]

F7

B8_IO[38]

G7

B8_IO[39]

F9

B8_IO[40]

E6

B8_IO[41]

E5

B8_IO[42]

G9

B8_IO[43]

IC1000

EP3C55F484C6N_SHRINK

F6

VCCD_PLL3

F5

GNDA3

G6

VCCA3

G4

B1_IO[0]

G3

B1_IO[1]

B2

B1_IO[2]

B1

B1_IO[3]

G5

B1_IO[4]

E4

B1_IO[5]

E3

B1_IO[6]

C2

B1_IO[7]

C1

B1_IO[8]

D2

B1_IO[9]

D1

B1_IO[10]

H7

B1_IO[11]

H6

B1_IO[12]

J6

B1_IO[13]

H4

B1_IO[14]

H3

B1_IO[15]

E2

B1_IO[16]

E1

B1_IO[17]

F2

B1_IO[18]

F1

B1_IO[19]

J5

B1_IO[20]

H5

B1_IO[21]

K6

nSTATUS

J7

B1_IO[22]

K7

B1_IO[23]

J4

B1_IO[24]

H2

B1_IO[25]

H1

B1_IO[26]

J3

B1_IO[27]

J2

B1_IO[28]

J1

B1_IO[29]

K2

DCLK

K1

B1_IO[30]

K5

nCONFIG

L5

TDI

L2

TCK

L1

TMS

L4

TDO

L3

nCE

G2

CLK0

G1

CLK1

IC1000

EP3C55F484C6N_SHRINK

T2

CLK2

T1

CLK3

L6

B2_IO[0]

M6

B2_IO[1]

M2

B2_IO[2]

M1

B2_IO[3]

M4

B2_IO[4]

M3

B2_IO[5]

N2

B2_IO[6]

N1

B2_IO[7]

M5

B2_IO[8]

P2

B2_IO[9]

P1

B2_IO[10]

R2

B2_IO[11]

R1

B2_IO[12]

N5

B2_IO[13]

P4

B2_IO[14]

P3

B2_IO[15]

U2

B2_IO[16]

U1

B2_IO[17]

V2

B2_IO[18]

V1

B2_IO[19]

P5

B2_IO[20]

N6

B2_IO[21]

R4

B2_IO[22]

R3

B2_IO[23]

W2

B2_IO[24]

W1

B2_IO[25]

Y2

B2_IO[26]

Y1

B2_IO[27]

T3

B2_IO[28]

N7

B2_IO[29]

P7

B2_IO[30]

AA2

B2_IO[31]

AA1

B2_IO[32]

V4

B2_IO[33]

V3

B2_IO[34]

P6

B2_IO[35]

R5

B2_IO[36]

T4

B2_IO[37]

T5

B2_IO[38]

R6

B2_IO[39]

T6

VCCA1

U5

GNDA1

U6

VCCD_PLL1

IC1000

EP3C55F484C6N_SHRINK

F16

B7_IO[0]

E16

B7_IO[1]

F15

B7_IO[2]

G16

B7_IO[3]

G15

B7_IO[4]

F14

B7_IO[5]

C18

B7_IO[6]

D18

B7_IO[7]

D17

B7_IO[8]

C19

B7_IO[9]

D19

B7_IO[10]

A20

B7_IO[11]

B20

B7_IO[12]

C17

B7_IO[13]

B19

B7_IO[14]

A19

B7_IO[15]

A18

B7_IO[16]

B18

B7_IO[17]

D15

B7_IO[18]

E15

B7_IO[19]

G14

B7_IO[20]

G13

B7_IO[21]

A17

B7_IO[22]

B17

B7_IO[23]

A16

B7_IO[24]

B16

B7_IO[25]

C15

B7_IO[26]

E14

B7_IO[27]

F13

B7_IO[28]

A15

B7_IO[29]

B15

B7_IO[30]

C13

B7_IO[31]

D13

B7_IO[32]

E13

B7_IO[33]

A14

B7_IO[34]

B14

B7_IO[35]

A13

B7_IO[36]

B13

B7_IO[37]

E12

B7_IO[38]

E11

B7_IO[39]

F11

B7_IO[40]

A12

CLK8

B12

CLK9

IC1000

EP3C55F484C6N_SHRINK

G22

CLK5

G21

CLK4

M18

CONF_DONE

M17

MSEL0

L18

MSEL1

L17

MSEL2

K20

MSEL3

L22

B6_IO[0]

L21

B6_IO[1]

K19

B6_IO[2]

K22

B6_IO[3]

K21

B6_IO[4]

J22

B6_IO[5]

J21

B6_IO[6]

H22

B6_IO[7]

H21

B6_IO[8]

K17

B6_IO[9]

K18

B6_IO[10]

J18

B6_IO[11]

F22

B6_IO[12]

F21

B6_IO[13]

J20

B6_IO[14]

J19

B6_IO[15]

J17

B6_IO[16]

H20

B6_IO[17]

H19

B6_IO[18]

E22

B6_IO[19]

E21

B6_IO[20]

H18

B6_IO[21]

H16

B6_IO[22]

D22

B6_IO[23]

D21

B6_IO[24]

F20

B6_IO[25]

F19

B6_IO[26]

G18

B6_IO[27]

H17

B6_IO[28]

C22

B6_IO[29]

C21

B6_IO[30]

B22

B6_IO[31]

B21

B6_IO[32]

C20

B6_IO[33]

D20

B6_IO[34]

F17

B6_IO[35]

G17

B6_IO[36]

F18

VCCA2

E18

GNDA2

E17

VCCD_PLL2

IC1000

EP3C55F484C6N_SHRINK

V17

VCCD_PLL4

V18

GNDA4

U18

VCCA4

AA22

B5_IO[0]

AA21

B5_IO[1]

T17

B5_IO[2]

T18

B5_IO[3]

W20

B5_IO[4]

W19

B5_IO[5]

Y22

B5_IO[6]

Y21

B5_IO[7]

U20

B5_IO[8]

U19

B5_IO[9]

W22

B5_IO[10]

W21

B5_IO[11]

T20

B5_IO[12]

T19

B5_IO[13]

R17

B5_IO[14]

P17

B5_IO[15]

V22

B5_IO[16]

V21

B5_IO[17]

R20

B5_IO[18]

U22

B5_IO[19]

U21

B5_IO[20]

R18

B5_IO[21]

R19

B5_IO[22]

N16

B5_IO[23]

R22

B5_IO[24]

R21

B5_IO[25]

P20

B5_IO[26]

P22

B5_IO[27]

P21

B5_IO[28]

N20

B5_IO[29]

N19

B5_IO[30]

N17

B5_IO[31]

N18

B5_IO[32]

N22

B5_IO[33]

N21

B5_IO[34]

M22

B5_IO[35]

M21

B5_IO[36]

M20

B5_IO[37]

M19

B5_IO[38]

M16

B5_IO[39]

T22

CLK7

T21

CLK6

3V3

R187

10K

3DTV

2010. 02. 11

3DF_INPUT/OUTPUT

1

3

LVDS OUTPUT

LVDS INPUT

<3D_SYNC_OUT>

TP[0]

TP[1]

TP[2]

TP[3]

TP[4]

TP[5]

FPGA DOWNLOAD CONTROL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

DDR_A[3]

SDDR_DQ[23]

DDR_A[6]

SDDR_DQ[1]

DDR_A[9]

DDR_DQ[23]

DDR_A[7]

DDR_DQ[18]

DDR_A[12]

SDDR_DQ[6]

DDR_A[5]

DDR_DQ[12]

DDR_A[3]

SDDR_DQ[15]

DDR_DQ[17]

DDR_DQ[8]

SDDR_DQ[0]

SDDR_DQ[31]

SDDR_DQ[31]

DDR_DQ[2]

SDDR_DQ[10]

SDDR_DQ[24]

DDR_A[0]

SDDR_DQ[14]

SDDR_DQ[11]

SDDR_DQ[29]

1V8

DDR_DQ[15]

SDDR_DQ[27]

1V8

DDR_DQ[22]

DDR_DQ[7]

SDDR_DQ[21]

DDR_DQ[1]

DDR_DQ[14]

DDR_DQ[16]

SDDR_DQ[26]

SDDR_DQ[4]

DDR_DQ[14]

DDR_A[10]

SDDR_DQ[19]

DDR_DQ[29]

DDR_DQ[15]

DDR_DQ[18]

DDR_A[12-0]

SDDR_DQ[30]

DDR_A[7]

DDR_DQ[7]

DDR_DQ[27]

SDDR_DQ[30]

SDDR_DQ[16]

DDR_DQ[13]

SDDR_DQ[16]

DDR_DQ[19]

DDR_DQ[20]

DDR_DQ[1]

SDDR_DQ[9]

SDDR_DQ[22]

DDR_DQ[0]

DDR_A[4]

DDR_DQ[31]

DDR_DQ[3]

SDDR_DQ[17]

DDR_DQ[31]

SDDR_DQ[25]

DDR_DQ[30]

DDR_A[10]

DDR_A[0]

DDR_DQ[19]

DDR_DQ[30]

SDDR_DQ[26]

SDDR_DQ[12]

DDR_DQ[20]

SDDR_DQ[6]

DDR_DQ[26]

SDDR_DQ[7]

SDDR_DQ[5]

DDR_DQ[2]

SDDR_DQ[10]

SDDR_DQ[8]

SDDR_DQ[22]

DDR_A[11]

DDR_DQ[26]

DDR_DQ[12]

SDDR_DQ[20]

SDDR_DQ[2]

DDR_A[4]

SDDR_DQ[1]

DDR_DQ[13]

DDR_DQ[6]

DDR_A[12-0]

SDDR_DQ[3]

DDR_DQ[28]

DDR_DQ[5]

DDR_DQ[6]

DDR_DQ[25]

SDDR_DQ[3]

SDDR_DQ[4]

DDR_DQ[8]

DDR_A[12]

SDDR_DQ[28]

DDR_A[8]

DDR_DQ[25]

DDR_DQ[0]

DDR_DQ[9]

SDDR_DQ[18]

DDR_A[1]

DDR_DQ[10]

DDR_DQ[24]

DDR_A[11]

DDR_DQ[17]

DDR_A[2]

SDDR_DQ[2]

DDR_DQ[28]

SDDR_DQ[25]

SDDR_DQ[17]

DDR_A[1]

SDDR_DQ[15]

DDR_DQ[15-0]

SDDR_DQ[24]

DDR_DQ[5]

DDR_DQ[4]

SDDR_DQ[13]

SDDR_DQ[21]

SDDR_DQ[20]

SDDR_DQ[29]

DDR_A[9]

SDDR_DQ[8]

DDR_DQ[11]

SDDR_DQ[28]

SDDR_DQ[12]

DDR_DQ[22]

SDDR_DQ[7]

DDR_DQ[31-16]

DDR_DQ[29]

SDDR_DQ[18]

SDDR_DQ[9]

DDR_DQ[4]

DDR_A[8]

DDR_A[2]

DDR_DQ[10]

SDDR_DQ[27]

SDDR_DQ[11]

DDR_A[6]

DDR_DQ[21]

DDR_DQ[3]

DDR_DQ[16]

SDDR_DQ[23]

SDDR_DQ[14]

DDR_DQ[24]

SDDR_DQ[13]

DDR_DQ[23]

SDDR_DQ[0]

SDDR_DQ[19]

DDR_DQ[27]

DDR_DQ[21]

DDR_DQ[9]

SDDR_DQ[5]

DDR_A[5]

DDR_DQ[11]

C1006

470pF

50V

470pF

50V

C1078

0.1uF

16V

0.1uF

16V

DDR2_CKE

C1047

10uF

16V

10uF

16V

AR1015

56

AR1010

56

DDR2_CKE

R1012

56

AR1018

56

/DDR2_CLK

/DDR_CS

C1025

0.1uF

16V

0.1uF

16V

C1087

0.1uF

16V

0.1uF

16V

C2014

0.1uF

16V

0.1uF

16V

DDR2_ODT

SDDR_DQ[15-0]

C2004

0.1uF

16V

0.1uF

16V

DDR2_ODT

DDR_BA[0]

C1024

0.1uF

16V

0.1uF

16V

/DDR_CS

SDDR_DQ[31-16]

C1045

0.1uF

16V

0.1uF

16V

AR1002

33

C1090

0.1uF

16V

0.1uF

16V

C2017

0.1uF

16V

0.1uF

16V

DDR_UDQS[1]

R1008 33

/DDR_CS

/DDR_CAS

C1054

0.1uF

16V

0.1uF

16V

DDR_UDQS[0]

C1049

0.1uF

16V

0.1uF

16V

C1098

0.1uF

16V

0.1uF

16V

DDR_BA[1]

C1089

0.1uF

16V

0.1uF

16V

C1063

0.1uF

16V

0.1uF

16V

2V5

C2008

0.1uF

16V

0.1uF

16V

C1033

0.1uF

16V

0.1uF

16V

AR1014

56

1V8

DDR_A[2]

C1084

0.1uF

16V

0.1uF

16V

DDR_A[7]

C1064

0.1uF

16V

0.1uF

16V

C1005

0.1uF

16V

0.1uF

16V

C1016

0.1uF

16V

0.1uF

16V

AR1004

33

DDR_A[12]

C1019

100pF

100pF

50V

C1076

0.1uF

16V

0.1uF

16V

AR1012

56

DDR_BA[0]

C1012

0.1uF

16V

0.1uF

16V

C1036

0.1uF

16V

0.1uF

16V

DDR_UDM[0]

IC1001

H5PS5162FFR-S6C

J2

VREF

J8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

DDR_A[5]

C1095

0.1uF

16V

0.1uF

16V

DDR_BA[0]

SDDR_DQ[31-16]

DDR_LDM[1]

C2013

0.1uF

16V

0.1uF

16V

R1007 33

C1096

0.1uF

16V

0.1uF

16V

/DDR_CAS

R1010 1K

/DDR_CS

R1002 33

DDR_A[10]

/DDR_RAS

AR1007

33

DDR_A[9]

C1079

0.1uF

16V

0.1uF

16V

C1013

0.1uF

16V

0.1uF

16V

DDR_A[6]

2V5

C1046

0.1uF

16V

0.1uF

16V

1V8

DDR_A[9]

DDR_VREF1

DDR_LDQS[0]

DDR_VREF0

C1057

0.1uF

16V

0.1uF

16V

R1011

56

56

C1059

0.1uF

16V

0.1uF

16V

C1050

0.1uF

16V

0.1uF

16V

C1071

10uF

16V

C1039

0.1uF

16V

0.1uF

16V

DDR_UDQS[0]

C1037

0.1uF

16V

0.1uF

16V

DDR_A[11]

DDR_A[8]

DDR_UDM[1]

C1091

0.1uF

16V

0.1uF

16V

DDR2_ODT

DDR2_CKE

DDR_LDQS[0]

R1003 33

DDR_A[5]

C1060

0.1uF

16V

0.1uF

16V

1V2

C1056

0.1uF

16V

0.1uF

16V

AR1005

33

C1043

0.1uF

16V

0.1uF

16V

AR1009

56

DDR_A[11]

C1088

0.1uF

16V

0.1uF

16V

C1041

0.1uF

16V

0.1uF

16V

DDR_LDQS[1]

C1001

10uF

16V

10uF

16V

DDR_A[10]

C2005

0.1uF

16V

0.1uF

16V

DDR_A[1]

C1068

0.1uF

0.1uF

16V

1V8

C1007

0.1uF

16V

0.1uF

16V

C2003

0.1uF

16V

0.1uF

16V

DDR_A[3]

DDR_A[12-0]

DDR2_ODT

C2011

0.1uF

16V

0.1uF

16V

/DDR_CAS

C1099

0.1uF

16V

0.1uF

16V

DDR_BA[0]

C1051

0.1uF

16V

0.1uF

16V

2V5

1V2

AR1003

33

DDR2_CLK

C1002

0.1uF

16V

0.1uF

16V

C2002

0.1uF

16V

0.1uF

16V

C2016

0.1uF

16V

0.1uF

16V

C1017

0.1uF

16V

0.1uF

16V

AR1016

56

DDR_A[6]

DDR_A[0]

C1080

0.1uF

16V

0.1uF

16V

C1058

0.1uF

16V

0.1uF

16V

DDR2_CKE

DDR2_ODT

C1093

0.1uF

16V

0.1uF

16V

IC1002

H5PS5162FFR-S6C

J2

VREF

J8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

C1070

10uF

16V

DDR2_CKE

C1011

470pF

50V

470pF

50V

C1081

0.1uF

16V

0.1uF

16V

C1038

0.1uF

16V

0.1uF

16V

DDR_A[3]

DDR_UDM[0]

DDR_BA[1]

R1004 1K

C1022

0.1uF

16V

0.1uF

16V

DDR_A[2]

DDR2_CLK

DDR_VTT

R1009 1K

/DDR2_CLK

C1097

0.1uF

16V

0.1uF

16V

DDR_A[3]

/DDR_WE

C2007

0.1uF

16V

0.1uF

16V

C1042

100pF

100pF

50V

SDDR_DQ[15-0]

DDR_A[4]

DDR_A[12-0]

DDR_A[8]

AR1017

56

C2001

0.1uF

16V

0.1uF

16V

DDR_A[9]

DDR_A[0]

DDR_VREF1

C1027

0.1uF

16V

0.1uF

16V

DDR_BA[1]

DDR_BA[1]

/DDR2_CLK

DDR_BA[1]

C2006

0.1uF

16V

0.1uF

16V

C2018

0.1uF

16V

0.1uF

16V

C1077

0.1uF

16V

0.1uF

16V

DDR_A[10]

C1021

0.1uF

16V

0.1uF

16V

DDR_A[5]

C1015

0.1uF

16V

0.1uF

16V

C1053

100pF

50V

100pF

50V

C1074

0.1uF

16V

0.1uF

16V

DDR_UDQS[1]

C1029

0.1uF

16V

0.1uF

16V

DDR_LDQS[1]

/DDR_RAS

DDR_VTT

C1004

0.1uF

16V

0.1uF

16V

AR1006

33

C1094

0.1uF

16V

0.1uF

16V

C1044

0.1uF

16V

0.1uF

16V

C1018

0.1uF

16V

0.1uF

16V

C1023

0.1uF

16V

0.1uF

16V

/DDR_CS

C1092

0.1uF

16V

0.1uF

16V

DDR_A[7]

R1001

100

DDR_A[11]

C1048

0.1uF

16V

0.1uF

16V

AR1001

33

AR1008

33

/DDR_WE

1V2

C1073

0.1uF

16V

0.1uF

16V

C1061

0.1uF

16V

0.1uF

16V

/DDR_RAS

C1082

0.1uF

16V

0.1uF

16V

DDR2_CLK

C1062

0.1uF

16V

0.1uF

16V

C1020

0.1uF

16V

0.1uF

16V

DDR_VTT

/DDR_WE

C1069

0.1uF

0.1uF

16V

C1065

0.1uF

16V

0.1uF

16V

AR1013

56

/DDR_RAS

C1066

100pF

100pF

50V

DDR_A[1]

/DDR_WE

C1010

0.1uF

16V

0.1uF

16V

DDR_UDM[1]

AR1011

56

DDR_A[0]

C2009

0.1uF

16V

0.1uF

16V

C2010

0.1uF

16V

0.1uF

16V

DDR_A[8]

C1083

0.1uF

16V

0.1uF

16V

DDR_A[12]

DDR_A[4]

C1035

0.1uF

16V

0.1uF

16V

C1085

0.1uF

16V

0.1uF

16V

C1040

0.1uF

16V

0.1uF

16V

C1075

0.1uF

16V

0.1uF

16V

C1009

0.1uF

16V

0.1uF

16V

/DDR_WE

C1008

0.1uF

16V

0.1uF

16V

C1034

0.1uF

16V

0.1uF

16V

DDR_VREF0

C1067

100pF

100pF

50V

C1031

470pF

50V

470pF

50V

R1005 1K

DDR_LDM[1]

C1072

0.1uF

16V

0.1uF

16V

C1003

0.1uF

16V

0.1uF

16V

R1006

100

DDR_A[6]

1V8

/DDR_RAS

DDR_A[1]

DDR_LDM[0]

DDR_A[4]

C1028

0.1uF

16V

0.1uF

16V

C1014

0.1uF

16V

0.1uF

16V

1V8

DDR_BA[0]

DDR_A[12]

C1055

0.1uF

16V

0.1uF

16V

DDR_LDM[0]

DDR_A[7]

C2000

0.1uF

16V

0.1uF

16V

C1030

470pF

50V

470pF

50V

C1052

0.1uF

16V

0.1uF

16V

C1032

0.1uF

16V

0.1uF

16V

C1026

0.1uF

16V

0.1uF

16V

/DDR_CAS

/DDR_CAS

C2015

0.1uF

16V

0.1uF

16V

C2012

0.1uF

16V

0.1uF

16V

1V8

DDR_A[2]

C1086

0.1uF

16V

0.1uF

16V

3V3

3V3

C2019

0.1uF

16V

0.1uF

16V

IC1000

EP3C55F484C6N_SHRINK

AA12

CLK13

AB12

CLK12

AA13

B4_IO[0]

AB13

B4_IO[1]

AA14

B4_IO[2]

AB14

B4_IO[3]

V12

B4_IO[4]

W13

B4_IO[5]

Y13

B4_IO[6]

AA15

B4_IO[7]

AB15

B4_IO[8]

U12

B4_IO[9]

Y14

B4_IO[10]

Y15

B4_IO[11]

AA16

B4_IO[12]

AB16

B4_IO[13]

V13

B4_IO[14]

W14

B4_IO[15]

U13

B4_IO[16]

V14

B4_IO[17]

U14

B4_IO[18]

U15

B4_IO[19]

V15

B4_IO[20]

W15

B4_IO[21]

T14

B4_IO[22]

T15

B4_IO[23]

AB18

B4_IO[24]

AA17

B4_IO[25]

AB17

B4_IO[26]

AA18

B4_IO[27]

AA19

B4_IO[28]

AB19

B4_IO[29]

W17

B4_IO[30]

Y17

B4_IO[31]

AA20

B4_IO[32]

AB20

B4_IO[33]

V16

B4_IO[34]

U16

B4_IO[35]

U17

B4_IO[36]

T16

B4_IO[37]

R16

B4_IO[38]

R14

B4_IO[39]

R15

B4_IO[40]

IC1000

EP3C55F484C6N_SHRINK

V6

B3_IO[0]

V5

B3_IO[1]

U7

B3_IO[2]

U8

B3_IO[3]

Y4

B3_IO[4]

Y3

B3_IO[5]

Y6

B3_IO[6]

AA3

B3_IO[7]

AB3

B3_IO[8]

W6

B3_IO[9]

V7

B3_IO[10]

AA4

B3_IO[11]

AB4

B3_IO[12]

AA5

B3_IO[13]

AA6

B3_IO[14]

AB6

B3_IO[15]

AB5

B3_IO[16]

W7

B3_IO[17]

Y7

B3_IO[18]

U9

B3_IO[19]

V8

B3_IO[20]

W8

B3_IO[21]

AA7

B3_IO[22]

AB7

B3_IO[23]

Y8

B3_IO[24]

T10

B3_IO[25]

T11

B3_IO[26]

V9

B3_IO[27]

V10

B3_IO[28]

U10

B3_IO[29]

AA8

B3_IO[30]

AB8

B3_IO[31]

AA9

B3_IO[32]

AB9

B3_IO[33]

U11

B3_IO[34]

V11

B3_IO[35]

W10

B3_IO[36]

Y10

B3_IO[37]

AA10

B3_IO[38]

AB10

B3_IO[39]

AA11

CLK15

AB11

CLK14

IC1000

EP3C55F484C6N_SHRINK

J11

VCCINT[0]

J12

VCCINT[1]

L14

VCCINT[2]

M14

VCCINT[3]

P11

VCCINT[4]

P12

VCCINT[5]

L9

VCCINT[6]

M9

VCCINT[7]

J13

VCCINT[8]

J14

VCCINT[9]

K14

VCCINT[10]

J10

VCCINT[11]

K9

VCCINT[12]

N9

VCCINT[13]

P9

VCCINT[14]

P10

VCCINT[15]

P13

VCCINT[16]

P14

VCCINT[17]

N14

VCCINT[18]

J16

VCCINT[19]

K15

VCCINT[20]

L16

VCCINT[21]

M15

VCCINT[22]

R12

VCCINT[23]

R10

VCCINT[24]

R8

VCCINT[25]

H9

VCCINT[26]

G12

VCCINT[27]

J8

VCCINT[28]

M8

VCCINT[29]

T7

VCCINT[30]

T9

VCCINT[31]

T13

VCCINT[32]

P15

VCCINT[33]

H15

VCCINT[34]

H11

VCCINT[35]

K8

VCCINT[36]

L7

VCCINT[37]

D4

VCCIO1[0]

F4

VCCIO1[1]

K4

VCCIO1[2]

N4

VCCIO2[0]

U4

VCCIO2[1]

W4

VCCIO2[2]

AB2

VCCIO3[0]

W5

VCCIO3[1]

W9

VCCIO3[2]

W11

VCCIO3[3]

AB21

VCCIO4[0]

W12

VCCIO4[1]

W16

VCCIO4[2]

W18

VCCIO4[3]

P18

VCCIO5[0]

V19

VCCIO5[1]

Y19

VCCIO5[2]

E19

VCCIO6[0]

G19

VCCIO6[1]

L19

VCCIO6[2]

A21

VCCIO7[0]

D12

VCCIO7[1]

D14

VCCIO7[2]

D16

VCCIO7[3]

A2

VCCIO8[0]

D5

VCCIO8[1]

D9

VCCIO8[2]

D11

VCCIO8[3]

IC1000

EP3C55F484C6N_SHRINK

L10

GND[0]

L11

GND[1]

M10

GND[2]

M11

GND[3]

L12

GND[4]

L13

GND[5]

M12

GND[6]

M13

GND[7]

N11

GND[8]

K11

GND[9]

N12

GND[10]

K12

GND[11]

K13

GND[12]

N13

GND[13]

N10

GND[14]

K10

GND[15]

J9

GND[16]

F12

GND[17]

H12

GND[18]

H13

GND[19]

J15

GND[20]

K16

GND[21]

L15

GND[22]

N15

GND[23]

R13

GND[24]

R11

GND[25]

R9

GND[26]

P8

GND[27]

H14

GND[28]

H10

GND[29]

H8

GND[30]

N8

GND[31]

R7

GND[32]

T8

GND[33]

T12

GND[34]

P16

GND[35]

L8

GND[36]

M7

GND[37]

A1

GND[38]

C5

GND[39]

C9

GND[40]

C11

GND[41]

C12

GND[42]

C14

GND[43]

C16

GND[44]

A22

GND[45]

E20

GND[46]

G20

GND[47]

L20

GND[48]

P19

GND[49]

V20

GND[50]

Y20

GND[51]

AB22

GND[52]

Y18

GND[53]

Y16

GND[54]

Y12

GND[55]

Y11

GND[56]

Y9

GND[57]

Y5

GND[58]

AB1

GND[59]

N3

GND[60]

U3

GND[61]

W3

GND[62]

D3

GND[63]

F3

GND[64]

K3

GND[65]

3DTV

3DF_DDR2

2

3

2010. 02. 11

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

R4031

1M

READY

C4039

0.1uF

16V

0.1uF

16V

READY

DDR_VREF0

C4051

0.1uF

16V

0.1uF

16V

FPGA_RESET

IC4006

AZ1085S-ADJTR/E1

1

ADJ/GND

2

OUTPUT

3

INPUT

L4008

BLM18PG121SN1D

C4057

0.1uF

16V

0.1uF

16V

C4041

22uF

25V

25V

C4034

0.1uF

16V

0.1uF

16V

L4011

MLB-201209-0120P-N2

SW4001

JTP-1127WEM

FPGA_RESET

1

2

4

3

DDR_VTT

C4047

0.1uF

16V

0.1uF

16V

FPGA_RESET

C4036

0.1uF

16V

0.1uF

16V

1V2

3V3

/3D_FPGA_RESET

IC4007

KIA7029AF

FPGA_RESET

2

G

3

O

1

I

L4009

BLM18PG121SN1D

C4045

0.1uF

16V

0.1uF

16V

R4039

4.7K

FPGA_RESET

R4032

1K

FPGA_RESET

C4052

10uF

25V

25V

R4035

62

1V8

C4055

0.1uF

16V

0.1uF

16V

R4038

220

220

R4029

10K

C4050

22uF

16V

16V

C4035

10uF

16V

10uF

16V

R4037

82

C4037

0.1uF

16V

0.1uF

16V

IC4004

BD35331F-E2

3

VTTS

2

EN

4

VREF

1

GND

5

VDDQ

6

VCC

7

VTT_IN

8

VTT

C4033

0.1uF

16V

0.1uF

16V

C4056

2.2uF

10V

2.2uF

10V

C4032

100uF

16V

16V

C4043

0.1uF

16V

0.1uF

16V

R4030

330

330

FPGA_RESET

3V3

3V3

3V3

DDR_VREF1

C4038

0.1uF

16V

0.1uF

16V

R4034

62

1V8

L408

3.6uH

C454

100uF

16V

R429

39K

1%

C434

0.1uF

0.1uF

R431

13K

13K

1/8W

1%

1%

C431

22uF

10V

22uF

10V

C429

47uF

16V

47uF

16V

C439

0.1uF

C452

0.1uF

16V

R442

47

IC402

MP8706EN-C247-LF-Z

3

SW_2

2

SW_1

4

BST

1

IN

5

EN/SYNC

6

FB

7

VCC

8

GND

C445

22uF

10V

22uF

10V

R428

1.2K

1%

R4040

10K

L

4

0

9

M

L

B

-

2

0

1

2

0

9

-

0

1

2

0

P

-

N

2

+5V

C4040

22uF

16V

22uF

16V

C4044

0.1uF

50V

0.1uF

50V

C4049

22uF

R4042

66.5

1%

L4010

BLM18SG700TN1D

R4036

1K

1K

1%

R4033

910

1%

IC4005

AZ1085S-ADJTR/E1

1

ADJ/GND

2

OUTPUT

3

INPUT

R4041

0

1/10W

5%

C4054

0.1uF

50V

0.1uF

50V

+5V

2V5

C4060

47uF

16V

47uF

16V

C4062

0.1uF

0.1uF

C4066

100uF

16V

R4045

47

C4065

0.1uF

16V

+5V

C4061

22uF

10V

22uF

10V

C4063

0.1uF

R4046

10K

IC4008

MP8706EN-C247-LF-Z

3

SW_2

2

SW_1

4

BST

1

IN

5

EN/SYNC

6

FB

7

VCC

8

GND

L4012

3.6uH

3.6uH

C4064

22uF

10V

22uF

10V

R4049

5.1K

1%

R4048

0

R4047

10K

10K

1/10W

1%

1%

R452

47K

47K

R451

0

0

R4050

0

1/10W

5%

R4051

0

1/10W

5%

R4052

0

1/10W

5%

3DTV

3DF_POWER

3

3

2010. 02. 11

R1

3A

R2

5V TO 3.3V

5V TO 2.5V

3.3V TO 1.8V

DDR VTT

R2

R1

V0 = 1.25(1+R2/R1)

R2

5V TO 1.2V

Vout=0.8*(1+R1/R2)

3A

R1

Click on the first or last page to see other 60PX950N-ZA / 60PX960-ZA (CHASSIS:PD02D) service manuals if exist.