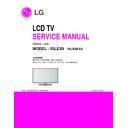

LG 55LEX8-SA (CHASSIS:LJ03S) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

GPIO_1

GPIO_9

GPIO_21

GPIO_12

+3.3V_DVDD

+3.3V_DVDD

GPIO_8

GPIO_2

GPIO_3

GPIO_0

GPIO_11

GPIO_5

STDP_UART_TX

GPIO_7

R3721

4.7K OPT

R3722

4.7K

GPIO_10

GPIO_4

R3723

4.7K

R3726

4.7K

R3727

4.7K

R3730

4.7K

R3732

4.7K

R3724

4.7K OPT

R3725

4.7K OPT

R3728

4.7K OPT

R3729

4.7K OPT

R3731

4.7K OPT

R3705

4.7K

R3708

4.7K

R3709

4.7K

R3707

4.7K

OPT

R3710

4.7K

OPT

R3711

4.7K

OPT

R3713

4.7K

R3717

4.7K

OPT

R3719

4.7K

OPT

R3712

4.7K

R3714

4.7K

OPT

R3715

4.7KOPT

R3718

4.7K

R3720

4.7K

R3706

4.7K

OPT

R3716

4.7K

R3704

12K

1%

+12V

R3701

10K

+1.2V

R3702

3.3K

1%

L3701

3.6uH

3.6uH

NR8040T3R6N

R3703

3.9K

1%

R3700

6.2K

L3700

IC3701

AOZ1072AI

DEV

3

AGND

2

VIN

4

FB

1

PGND

5

COMP

6

EN

7

LX_1

8

LX_2

IC3700

STDP4028AB(REV.C)

E0_LVRX_CH0N

P2

E0_LVRX_CH0P

N2

E0_LVRX_CH1N

P3

E0_LVRX_CH1P

N3

E0_LVRX_CH2N

N4

E0_LVRX_CH2P

M4

E0_LVRX_CLKN

M5

E0_LVRX_CLKP

L5

E0_LVRX_CH3N

N6

E0_LVRX_CH3P

M6

E0_LVRX_CH4N

P7

E0_LVRX_CH4P

N7

E1_LVRX_CH0N

G1

E1_LVRX_CH0P

G2

E1_LVRX_CH1N

H1

E1_LVRX_CH1P

H2

E1_LVRX_CH2N

J2

E1_LVRX_CH2P

J3

E1_LVRX_CLKN

K3

E1_LVRX_CLKP

K4

E1_LVRX_CH3N

L2

E1_LVRX_CH3P

L3

E1_LVRX_CH4N

M1

E1_LVRX_CH4P

M2

O0_LVRX_CH0N

P8

O0_LVRX_CH0P

N8

O0_LVRX_CH1N

N9

O0_LVRX_CH1P

M9

O0_LVRX_CH2N

M10

O0_LVRX_CH2P

L10

O0_LVRX_CLKN

N11

O0_LVRX_CLKP

M11

O0_LVRX_CH3N

P12

O0_LVRX_CH3P

N12

O0_LVRX_CH4N

P13

O0_LVRX_CH4P

N13

O1_LVRX_CH0N

M13

O1_LVRX_CH0P

M14

O1_LVRX_CH1N

L12

O1_LVRX_CH1P

L13

O1_LVRX_CH2N

K12

O1_LVRX_CH2P

K11

O1_LVRX_CLKN

J12

O1_LVRX_CLKP

J13

O1_LVRX_CH3N

H13

O1_LVRX_CH3P

H14

O1_LVRX_CH4N

G13

O1_LVRX_CH4P

G14

E0_LVRX_CH5N

M7

E0_LVRX_CH5P

L6

E0_LVRX_CH6N

M3

E0_LVRX_CH6P

L4

E1_LVRX_CH5N

J5

E1_LVRX_CH5P

H4

E1_LVRX_CH6N

J4

E1_LVRX_CH6P

K5

O0_LVRX_CH5N

M8

O0_LVRX_CH5P

L9

O0_LVRX_CH6N

L11

O0_LVRX_CH6P

M12

O1_LVRX_CH5N

J10

O1_LVRX_CH5P

H11

O1_LVRX_CH6N

K10

O1_LVRX_CH6P

J11

POWER_ON/OFF2_1

C3703

3300pF

C3702

0.1uF

16V

0.1uF

16V

C3701

10uF

25V

10uF

25V

C3706

0.1uF

16V

0.1uF

16V

C3704

22uF

10V

22uF

10V

C3705

100pF

50V

OPT

C3700

10uF

25V

10uF

25V

TC1+

TC1-

TA1+

TCLK1-

TE1-

TD1+

TB1+

TB1-

TD1-

TA1-

TE1+

TCLK1+

TB2+

TCLK2+

TA2+

TC2+

TD2-

TB2-

TE2-

TCLK2-

TC2-

TA2-

TE2+

TD2+

(BS_3)

(BS_6)

(BS_7)

(Pixel Width)

(Gain)

(Pre-Emphasis)

(BS_2)

(BS_4)

(LVDS Format)

(Down Spread Enable)

(LVDS Format)

(BS_5)

(BS_1)

STDP4020 DPRx Hardware Bootstraps

STDP4028 DPTX Firmware Bootstraps

(BS_0)

ALEF M240Hz(TM480Hz) JIG Board

2009. 12. 28

2

3

DP Signal

R2

Vout=0.8*(1+R1/R2)

R1

STDP TX CORE 1.26V

2A

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+3.3V_DVDD

VDD_RPLL_+1.2V

+1.2V_DVDD

+1.2V_AVDD

AVDD_+3.3V

AVDD_OUT_LV_33

AVDD_LVRX_+1.2V

C3805

0.1uF

16V

0.1uF

16V

C3814

0.1uF

16V

0.1uF

16V

VDD_RPLL_+1.2V

C3813

0.1uF

16V

0.1uF

16V

C3826

0.1uF

16V

0.1uF

16V

AVDD_OUT_LV_33

+3.3V_NORMAL

+3.3V_DVDD

AVDD_+3.3V

C3808

0.1uF

16V

0.1uF

16V

L3804

120-ohm

+1.2V_DVDD

VDD_RPLL_+1.2V

C3815

0.1uF

16V

0.1uF

16V

+3.3V_DVDD

+3.3V_DVDD

C3807

0.1uF

16V

0.1uF

16V

L3802

120-ohm

C3810

0.1uF

16V

0.1uF

16V

C3803

0.1uF

16V

0.1uF

16V

L3800

120-ohm

C3801

0.1uF

16V

0.1uF

16V

C3820

0.1uF

16V

0.1uF

16V

C3822

0.1uF

16V

0.1uF

16V

C3812

0.1uF

16V

0.1uF

16V

C3802

0.1uF

16V

0.1uF

16V

C3824

0.1uF

16V

0.1uF

16V

AVDD_OUT_LV_33

C3817

0.1uF

16V

0.1uF

16V

AVDD_+3.3V

C3806

0.1uF

16V

0.1uF

16V

+3.3V_DVDD

L3801

120-ohm

C3818

0.1uF

16V

0.1uF

16V

C3819

0.01uF

25V

0.01uF

25V

DPRX_ML_L0N

+1.2V_AVDD

R3809

33

R3803

240

1/16W

1%

+3.3V_DVDD

C3835

0.1uF

16V

0.1uF

16V

DPRX_ML_L1P

DPRX_ML_L1N

DPRX_ML_L0P

GPIO_10

STDP_SPI_DO

LD3800

SML-210MT

+3.3V_DVDD

C3838

0.1uF

0.1uF

X3801

27MHz

R3816

33

STDP_SPI_CLK

STDP_SPI_DI

R3818

3.3K

R3810

4.7K

STDP_SPI_CS

STDP_UART_TX

STDP_SPI_CLK

R3804

0

C3836 12pF 50V

+3.3V_DVDD

R3824 33

R3815

0

GPIO_7

R3807

33

GPIO_5

AVDD_+3.3V

GPIO_0

GPIO_4

GPIO_12

R3812

0

GPIO_2

R3808

33

STDP_SPI_DI

GPIO_8

GPIO_1

R3814

0

GPIO_11

R3801

2.7K

R3806

0

STDP_SPI_CS

STDP_UART_RX

C3837

12pF 50V

STDP_SPI_DO

R3805

0

GPIO_3

R3813

0

SW3800

JTP-1127WEM

1

2

4

3

R3802

220

220

GPIO_9

GPIO_21

R3817

10K

IC3800

W25X20AVSNIG

3

WP

2

DO

4

GND

1

CS

5

DIO

6

CLK

7

HOLD

8

VCC

C3832

0.1uF

16V

0.1uF

16V

C3827

0.1uF

16V

0.1uF

16V

C3811

0.1uF

16V

0.1uF

16V

C3829

0.1uF

16V

0.1uF

16V

+1.2V_DVDD

+1.2V_AVDD

C3823

0.1uF

16V

0.1uF

16V

C3831

0.1uF

16V

0.1uF

16V

C3833

0.1uF

16V

0.1uF

16V

C3809

0.1uF

16V

0.1uF

16V

C3804

0.1uF

16V

0.1uF

16V

+1.2V

C3830

0.1uF

16V

0.1uF

16V

C3816

0.1uF

16V

0.1uF

16V

L3806

120-ohm

C3821

0.1uF

16V

0.1uF

16V

+1.2V

+1.2V_DVDD

L3803

120-ohm

+1.2V_AVDD

STDP_UART_RX

STDP_UART_TX

R3800

33

+5V_NORMAL

C3800

0.1uF

50V

0.1uF

50V

L3805

120-ohm

+1.2V_AVDD

AVDD_LVRX_+1.2V

C3828

0.1uF

16V

0.1uF

16V

C3825

0.1uF

16V

0.1uF

16V

R3821

0

+3.3V_DVDD

SCL3_3.3V

SDA3_3.3V

R3823 0

R3822 0

R3826

4.7K

C3834

0.1uF

16V

0.1uF

16V

OPT

C3839

0.1uF

16V

16V

OPT

DPRX_AUX_N

DPRX_AUX_P

IC3700

STDP4028AB(REV.C)

PVDD1_1

E7

PVDD1_2

E8

PVDD1_3

K6

PVDD1_4

K9

PVDD21

G11

PVDD22

G5

DPTX_VDDA_1V2_1

B11

DPTX_VDDA_1V2_2

C7

DPTX_VDDA_1V2_3

C8

DPTX_VDDA_1V2_4

D9

VDDA_3V3

D6

VDD33_TX

D5

VDD_RPLL

A3

AVDD_LVRX_12

L7

AVDD_OUT_LVRX_33_1

H3

AVDD_OUT_LVRX_33_2

H12

AVDD_OUT_LVRX_33_3

L8

AVDD_OUT_LVRX_33_4

N1

AVDD_OUT_LVRX_33_5

N14

PVSS3_1

A1

PVSS3_2

A14

PVSS3_3

F6

PVSS3_4

F7

PVSS3_5

F8

PVSS3_6

F9

PVSS3_7

G6

PVSS3_8

G7

PVSS3_9

G8

PVSS3_10

G9

PVSS3_11

H6

PVSS3_12

H7

PVSS3_13

H8

PVSS3_14

H9

PVSS3_15

J6

PVSS3_16

J7

PVSS3_17

J8

PVSS3_18

J9

DPTX_VSSA_1

D7

DPTX_VSSA_2

D8

DPTX_VSSA_3

E9

DPTX_VSSA_4

E10

VSS_RPLL

A2

VSSA_TX

C5

AVSS_LVRX

K7

AVSS_OUT_LVRX_6

P1

AVSS_OUT_LVRX_1

F2

AVSS_OUT_LVRX_2

F13

AVSS_OUT_LVRX_3

H5

AVSS_OUT_LVRX_4

H10

AVSS_OUT_LVRX_5

K8

AVSS_OUT_LVRX_7

P14

IC3700

STDP4028AB(REV.C)

DPTX_REXT

C11

DPTX_HDP_IN_GPIO_23

C12

DPTX_AUXN

C10

DPTX_AUXP

D10

DPTX_ML_L0N

B6

DPTX_ML_L0P

C6

DPTX_ML_L1N

A7

DPTX_ML_L1P

B7

DPTX_ML_L2N

A8

DPTX_ML_L2P

B8

DPTX_ML_L3N

B9

DPTX_ML_L3P

C9

TX_XTAL

B4

TX_TCLK

C4

RESETn

E6

SPI_DI

D13

SPI_DO

C14

SPI_CLK

E12

SPI_CSn

F10

IR_IN_GPIO_6

G4

IRQ_BOOT7_GPIO_12

D12

VBUFC_RPLL

C3

TESTMODE0

F3

TESTMODE1

G3

AUX_I2C_SCL_GPIO_15

C13

AUX_I2C_SDA_GPIO_16

B14

I2C_SCL_GPIO_24

B13

I2C_SDA_GPIO_25

A13

UART_TX_BOOT1_GPIO_13

C2

UART_RX_GPIO_14

B1

AUX_UART_TX_BOOT2_GPIO_21

B12

AUX_UART_RX_GPIO_22

A12

I2S_0_GPIO_8

D2

I2S_1_GPIO_9

F5

I2S_2_GPIO_10

F4

I2S_3_GPIO_11

D3

I2S_BCLK_GPIO_7

C1

I2S_WCLK_GPIO_4

E4

CLK_OUT_GPIO_5

E3

NC_1

B2

NC_2

B3

NC_3

D11

NC_4

E11

NC_5

F12

NC_6

G12

PWM0_GPIO_0_BOOT3

E5

GPIO_1

D4

GPIO_2_BOOT_5

G10

GPIO_3_BOOT6

F11

STDP_SPI_CLK

STDP_SPI_CS

STDP_SPI_DI

R3832

22

22

R3829

22

22

R3830

22

22

STDP_SPI_DO

R3831

22

22

P3802

12505WR-05A00

1

STDP_SPI_DI

2

STDP_SPI_CKL

3

STDP_SPI_DO

4

STDP_SPI_CS

5

6

R3819 0

R3820 0

P3800

12507WS-04L

1

+3.3V

2

GND

3

RX

4

TX

5

.

C3840

47uF

25V

25V

OPT

C3841

22uF

16V

22uF

16V

OPT

DP_RESET

ALEF M240Hz(TM480Hz) JIG Board

DP Signal

2009. 12. 28

3

3

[DPRX Firmware Bootstraps]

[SPI FLASH(2Mbit)]

[DPRX Hardware Bootstraps]

UART JIG

Temporary STDP TX SPI DOWNLOAD

THERMAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

09.10

AMP_SUB_NTP

21 100

GP2_BCM_ATSC

AUD_SCK

D3901

100V

1N4148W

OPT

R3915

12

C3926

22000pF

50V

TP3900

+1.8V_AMP

TP3902

SPK2_L+

R3918

12

AUD_LRCH

C3925

22000pF

50V

C3932

390pF

50V

0.1uF

C3927

50V

R3922

4.7K

0.01uF

C3942

50V

OPT

AMP_MUTE1

L3901

BLM18PG121SN1D

L3903

AD-9060

15uH

2S

1S

1F

2F

R3926

3.3

OPT

+3.3V_NORMAL

C3905

1000pF

50V

C3918

1000pF

50V

1000pF

50V

R3928

10K

0.1uF

C3917

50V

0.1uF

C3904

16V

R3912

12

0.1uF

C3915

16V

C3935

0.47uF

50V

R3916

12

C3903

100pF

50V

0.01uF

C3941

50V

OPT

C3902

10uF

10V

OPT

+1.8V_AMP

C3922

1uF

25V

L3902

BLM18PG121SN1D

AUD_LRCK

0.1uF

C3939

50V

R3914

12

R3925

3.3

OPT

SDA2_3.3V

C3920

22000pF

50V

R3921

4.7K

C3913

1uF

25V

C3924

1uF

25V

SPK2_R+

C3907

1000pF

50V

0.1uF

C3938

50V

R3919

12

L3900

BLM18PG121SN1D

R3917

12

R3929

0

0

OPT

+24V_AMP

SPK2_R-

D3902

100V

1N4148W

OPT

C3928

0.01uF

50V

0.01uF

50V

0.1uF

C3908

R3920

4.7K

R3909

3.3K

D3903

100V

1N4148W

OPT

C3919

1uF

25V

R3927

3.3

OPT

0.1uF

C3937

50V

R3923

4.7K

TP3903

C3934

0.47uF

50V

+1.8V_AMP

R3924

3.3

OPT

C3923

10uF

35V

10uF

35V

C3900

10uF

10V

OPT

C3916

22000pF

50V

+24V_AMP

C3914

22pF

50V

22pF

50V

OPT

C3929

10uF

35V

10uF

35V

R3913

12

C3931

390pF

50V

AMP_RESET_N

L3904

AD-9060

15uH

2S

1S

1F

2F

0.01uF

C3940

50V

OPT

C3910

22pF

50V

22pF

50V

OPT

C3930

390pF

50V

C3901

0.1uF

16V

AUD_MASTER_CLK

POWER_DET

C3933

390pF

50V

C3911

22pF

50V

22pF

50V

OPT

0.01uF

C3943

50V

OPT

SCL2_3.3V

SPK2_L-

R

3

9

1

1

1

0

0

IC3900

NTP-7000

EAN60969601

DEV

1

BST1A

2

VDR1A

3

/RESET

4

AD

5

DGND_1

6

GND_IO

7

CLK_I

8

VDD_IO

9

DGND_PLL

10

AGND_PLL

11

LF

12

AVDD_PLL

13

DVDD_PLL

14

GND

15

DGND_2

16

DVDD

17

SDATA

18

WCK

19

BCK

20

SDA

21

SCL

22

MONITOR0

23

MONITOR1

24

MONITOR2

25

/FAULT

26

VDR2B

27

BST2B

28

PGND2B_1

29

PGND2B_2

30

OUT2B_1

31

OUT2B_2

32

PVDD2B_1

33

PVDD2B_2

34

PVDD2A_1

35

PVDD2A_2

36

OUT2A_1

37

OUT2A_2

38

PGND2A_1

39

PGND2A_2

40

BST2A

41

VDR2A

42

NC

43

VDR1B

44

BST1B

45

PGND1B_1

46

PGND1B_2

47

OUT1B_1

48

OUT1B_2

49

PVDD1B_1

50

PVDD1B_2

51

PVDD1A_1

52

PVDD1A_2

53

OUT1A_1

54

OUT1A_2

55

PGND1A_1

56

PGND1A_2

57

EP_PAD

D3900

100V

1N4148W

OPT

C3912

10uF

10uF

10V

OPT

0.1uF

C3936

50V

R3931

3.3

3.3

SPK2_L+

R3908

0

0

R3907-*1

CIS21J121

R3905

0

0

SPK_OUTPUT_RESISTER

SPK2_R+

R3908-*1

CIS21J121

SPK2_L-

R3907

0

0

SPK2_R-

R3905-*1

CIS21J121

SPK_OUTPUT_COIL

R3906-*1

CIS21J121

R3906

0

0

R3901

0

R3903

0

R3900

0

R3902

0

R3904

0

R3930

100

C3906

15pF

50V

15pF

50V

C3909

15pF

50V

15pF

50V

JK3900

TJC2508-4A

1

VCC

2

SCL

3

SDA

4

GND

SPEAKER2_R

Sub AMP.

SPEAKER2_L

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

Non_CI

2009.10.19

CI_A[0]

CI_A[1]

CI_A[2]

CI_A[3]

CI_A[4]

CI_A[5]

CI_A[6]

CI_A[7]

CI_A[8]

CI_A[9]

CI_A[10]

CI_A[11]

CI_A[12]

CI_A[13]

CI_OUTDATA[4]

CI_OUTDATA[5]

CI_OUTDATA[6]

CI_OUTDATA[7]

CI_OUTCLK

CI_OUTVALID

CI_OUTSTART

CI_OUTDATA[0]

CI_OUTDATA[1]

CI_OUTDATA[2]

CI_OUTDATA[3]

CI_OUTCLK

/CI_WAIT

CI_MOD_RESET [GP49]

/CI_CD2 [GP38]

CI_MOD_RESET

/CI_CD1

FE_TS_DATA_CLK

FE_TS_VAL_ERR

/CI_WAIT

/CI_IREQ

[GP39]

007:H5;016:AJ3

/CI_CD1

CI_OUTCLK,CI_OUTDATA[0-7],CI_OUTSTART,CI_OUTVALID

FE_TS_SYNC

/CI_CD2

EBI_RW

007:E6

CI_5V_CTL

[GP27]

007:H7

CI_A[0-13]

EBI_WE

/CI_SEL

CI_A[14]

EBI_CS

SC_RE2

SC1_ID

SC1_FB

SCART1_Lout_P

SC_RE1

DTV_ATV_SELECT

DTV/MNT_V_OUT

SCART1_Rout_N

SC1_CVBS_IN

SCART1_Lout_N

SCART1_Rout_P

SC1_R

SC1_G

SC1_R_IN

SC1_B

SC1_L_IN

SCART1_DET

High_Common(BCM3556)

46

DVB-CI PULL-UP (Near CI Slot)

DVB-CI PULL-DOWN (Near CI Slot)

CI POWER ENABLE CONTROL

CI CONTROL BUFFER

NON_SCART

Click on the first or last page to see other 55LEX8-SA (CHASSIS:LJ03S) service manuals if exist.