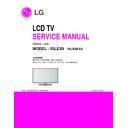

LG 55LEX8-SA (CHASSIS:LJ03S) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

3D_IR_LV9X00

09/11/18

24 100

GP2_BCM_ATSC

R3004

2.7K

2.7K

OPT

L3000

MLB-201209-0120P-N2

120-ohm

OPT

R3001

0

OPT

C3002

10uF

10V

10uF

10V

USB_PWRON3

9:D4;9:G4

+5V_USB

C3001

100uF

16V

R3002

4.7K

OPT

4.7K

OPT

L3001

MLB-201209-0120P-N2

120-ohm

USB_PWRFLT3

9:D3;9:G4

C3003

0.1uF

IC2601

AP2191SG-13

OPT

EAN60921001

3

IN_2

2

IN_1

4

EN

1

GND

5

FLG

6

OUT_1

7

OUT_2

8

NC

+3.3V_NORMAL

MODEL_OPT_4

R3003

100

OPT

USB_PWRON3

9:D4;9:G4

+5V_EMITTER

P2600

12507WR-03L

Inner_Emitter

1

2

3

4

R3000

0

+5V_EMITTER

R3005

0

1/10W

C3000

0.1uF

D3000

30V

SIDE IR Emitter sync PHONE JACK

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

LVDS_TX_0_CLK_N

C2838

0.1uF

16V

0.1uF

16V

C2803

0.1uF

16V

0.1uF

16V

IC2800

EP3C55F484C8N

NC_1

A11

NC_2

A12

NC_3

A20

NC_4

AA1

NC_5

AA2

NC_6

AA11

NC_7

AA12

NC_8

AA20

NC_9

AB5

NC_10

AB6

NC_11

AB11

NC_12

AB12

NC_13

B4

NC_14

B11

NC_15

B12

NC_16

B21

NC_17

B22

NC_18

C3

NC_19

C4

NC_20

C10

NC_21

C15

NC_22

C20

NC_23

C21

NC_24

C22

NC_25

D2

NC_26

D6

NC_27

D17

NC_28

D20

NC_29

D21

NC_30

D22

NC_31

E1

NC_32

E3

NC_33

E4

NC_34

E5

NC_35

E6

NC_36

E7

NC_37

E8

NC_38

E9

NC_39

E11

NC_40

E12

NC_41

E13

NC_42

E14

NC_43

E15

NC_44

F7

NC_45

F8

NC_46

F9

NC_47

F10

NC_48

F11

NC_49

F13

NC_50

F14

NC_51

F15

NC_52

F16

NC_53

F17

NC_54

F21

NC_55

F22

NC_56

G3

NC_57

G4

NC_58

G5

NC_59

G7

NC_60

G8

NC_61

G9

NC_62

G10

NC_63

G11

NC_64

G13

NC_65

G14

NC_66

G15

NC_67

G16

NC_68

G17

NC_69

G18

NC_70

H3

NC_71

H4

NC_72

H5

NC_73

H6

NC_74

H7

NC_75

H16

NC_76

H17

NC_77

J3

NC_78

J4

NC_79

J5

NC_80

J6

NC_81

J7

NC_82

J17

NC_83

K7

NC_84

K19

NC_85

L6

NC_86

M1

NC_87

M2

NC_88

M3

NC_89

M4

NC_90

M5

NC_91

M6

NC_92

N5

NC_93

N6

NC_94

N7

NC_95

N16

NC_96

N17

NC_97

P3

NC_98

P4

NC_99

P5

NC_100

P6

NC_101

P7

NC_102

P20

NC_103

R3

NC_104

R4

NC_105

R5

NC_106

R6

NC_107

R15

NC_108

T3

NC_109

T4

NC_110

T5

NC_111

T10

NC_112

T11

NC_113

T14

NC_114

T21

NC_115

T22

NC_116

U7

NC_117

U8

NC_118

U13

NC_119

U19

NC_120

V3

NC_121

V4

NC_122

V6

NC_123

V7

NC_124

W1

NC_125

W2

NC_126

Y1

NC_127

Y2

C2809

0.1uF

16V

0.1uF

16V

R2838

100

C2839

0.1uF

16V

0.1uF

16V

R2814

10K

C2827

0.1uF

16V

0.1uF

16V

2V5

LVDS_TX_1_DATA0_N

MSEL[2]

IC2801

EPCS16SI8N_

3

VCC

2

DATA

4

GND

1

NCS

5

ASDI

6

DCLK

7

VCC_1

8

VCC_2

MSEL[3]

LVDS_TX_0_CLK_N

LVDS_TX_1_DATA1_N

TDI_FPGA

LVDS_TX_1_DATA1_P

R2801

22

22

LVDS_TX_0_DATA4_N

LVDS_TX_0_DATA4_P

TA1-

TCLK2-

IC2800

EP3C55F484C8N

NSTATUS

K6

NCONFIG

K5

CONFIG_DONE

M18

DCLK

K2

TCK

L2

TDO

L4

TMS

L1

TDI

L5

DATA0

K1

MSEL0

M17

MSEL1

L18

MSEL2

L17

MSEL3

K20

NCE

L3

ASDO

D1

NCSO

E2

SYSCLK54

G21

RST_N

G22

SCL

A3

SDA

B3

TEST7

J21

TEST6

J20

TEST5

J19

TEST4

J18

TEST3

H21

TEST2

H20

TEST1

H19

TEST0

H18

LED3

E21

LED2

E22

LED1

F19

LED0

F20

R2810

22

R2813

22

R2812

22

TA2+

R2845

100

R2843

100

SDA1_3.3V

R2822

1K

C2856

0.1uF

16V

0.1uF

16V

/CONFIG

C2847

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA3_P

C2866

0.1uF

16V

0.1uF

16V

C2812

0.1uF

16V

0.1uF

16V

C2831

0.1uF

16V

0.1uF

16V

A2.5V

C2808

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA1_P

SYSCLK

C2850

100pF

50V

100pF

50V

SCL1_3.3V

R2844

100

C2825

0.1uF

16V

0.1uF

16V

R2835

4.7K

OPT

C2824

0.1uF

16V

0.1uF

16V

LVDS_TX_0_DATA2_N

TE1+

TDO_FPGA

TP[0]

C2845

0.1uF

16V

0.1uF

16V

C2822

0.1uF

16V

0.1uF

16V

LVDS_TX_0_DATA0_P

R2802

27

27

LVDS_TX_1_DATA0_P

C2853

0.1uF

16V

MSEL[0]

LVDS_TX_0_DATA0_N

C2842

0.1uF

16V

0.1uF

16V

3V3

TE2+

TCLK1-

C2854

0.1uF

16V

0.1uF

16V

C2816

0.1uF

16V

0.1uF

16V

C2821

0.1uF

16V

0.1uF

16V

R2804

22

R2803

22

2V5

C2833

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA4_N

L2801

R2817

10K

10K

LVDS_TX_0_CLK_P

C2869

10uF

16V

16V

R2842

100

R2824

4.7K

TC1-

LVDS_TX_0_DATA3_P

C2836

0.1uF

16V

0.1uF

16V

R2821

0

OPT

+1.2V

LVDS_TX_0_DATA0_N

/CE_FPGA

R2815

0

OPT

2V5

LVDS_TX_1_DATA0_P

LVDS_TX_0_CLK_P

2V5

3V3

DATA0

LVDS_TX_0_DATA4_N

LVDS_TX_1_DATA2_N

LVDS_TX_1_DATA1_N

/CSO

X2801

54.0000MHz

4

VDD

1

TRISTATE/OPEN

2

GND

3

OUTPUT

C2828

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA2_N

L2804

BLM18PG121SN1D

TP[5]

TB1-

LVDS_TX_0_DATA1_P

C2864

100pF

50V

100pF

50V

TDI_FPGA

TMS_FPGA

MSEL[2]

C2860

0.1uF

16V

0.1uF

16V

1V2

C2814

0.1uF

16V

0.1uF

16V

/RESET_FPGA

R2834

4.7K

TD1+

LVDS_TX_1_DATA3_N

C2807

0.1uF

16V

0.1uF

16V

TCK_FPGA

IC2800

EP3C55F484C8N

VCCA1

T6

VCCA2

F18

VCCA3

G6

VCCA4

U18

VCCD_PLL1

U6

VCCD_PLL2

E17

VCCD_PLL3

F6

VCCD_PLL4

V17

VCCIO1_1

D4

VCCIO1_2

F4

VCCIO1_3

K4

VCCIO2_1

N4

VCCIO2_2

U4

VCCIO2_3

W4

VCCIO3_1

AB2

VCCIO3_2

W5

VCCIO3_3

W9

VCCIO3_4

W11

VCCIO4_1

AB21

VCCIO4_2

W12

VCCIO4_3

W16

VCCIO4_4

W18

VCCIO5_1

P18

VCCIO5_2

V19

VCCIO5_3

Y19

VCCIO6_1

E19

VCCIO6_2

G19

VCCIO6_3

L19

VCCIO7_1

A21

VCCIO7_2

D12

VCCIO7_3

D14

VCCIO7_4

D16

VCCIO8_1

A2

VCCIO8_2

D5

VCCIO8_3

D9

VCCIO8_4

D11

VCCINT_1

J11

VCCINT_2

J12

VCCINT_3

L14

VCCINT_4

M14

VCCINT_5

P11

VCCINT_6

P12

VCCINT_7

L9

VCCINT_8

M9

VCCINT_9

J13

VCCINT_10

J14

VCCINT_11

K14

VCCINT_12

J10

VCCINT_13

K9

VCCINT_14

N9

VCCINT_15

P9

VCCINT_16

P10

VCCINT_17

P13

VCCINT_18

P14

VCCINT_19

N14

VCCINT_20

J16

VCCINT_21

K15

VCCINT_22

L16

VCCINT_23

M15

VCCINT_24

R12

VCCINT_25

R10

VCCINT_26

R8

VCCINT_27

H9

VCCINT_28

G12

VCCINT_29

J8

VCCINT_30

M8

VCCINT_31

T7

VCCINT_32

T9

VCCINT_33

T13

VCCINT_34

P15

VCCINT_35

H15

VCCINT_36

H11

VCCINT_37

K8

VCCINT_38

L7

DDR_VREF_1

AA18

DDR_VREF_2

AB4

DDR_VREF_3

U11

DDR_VREF_4

V9

DDR_VREF_5

V12

DDR_VREF_6

V16

3V3

C2865

0.1uF

16V

0.1uF

16V

C2823

0.1uF

16V

0.1uF

16V

TP[1]

DCLK

TCK_FPGA

2V5

C2862

0.1uF

16V

0.1uF

16V

LVDS_TX_0_DATA3_P

LVDS_TX_1_DATA0_N

LVDS_TX_1_CLK_N

C2837

0.1uF

16V

0.1uF

16V

R2829

22

22

OPT

LVDS_TX_0_DATA3_N

TP[3]

TP[3]

MSEL[0]

R2825

0

OPT

R2839

100

TA2-

R2837

100

C2844

0.1uF

16V

0.1uF

16V

/CONFIG

TCLK1+

LVDS_TX_1_CLK_N

+3.3V_NORMAL

TA1+

R2805

22

22

R2827

0

OPT

TD2-

TP[0]

ASDO

TE2-

LVDS_TX_1_DATA3_P

R2840

100

ASDO

C2826

0.1uF

16V

0.1uF

16V

/STATUS

C2861

0.1uF

16V

0.1uF

16V

2V5

R2823

22

22

2V5

C2863

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA4_N

/CE_FPGA

TP[4]

2V5

C2858

10uF

16V

10uF

16V

LVDS_TX_0_DATA1_N

C2820

0.1uF

16V

0.1uF

16V

LVDS_TX_0_DATA0_P

C2801

0.1uF

16V

0.1uF

16V

/STATUS

R2846

100

LVDS_TX_1_DATA2_P

C2849

0.1uF

16V

0.1uF

16V

TP[2]

LVDS_TX_0_DATA1_P

C2817

0.1uF

16V

0.1uF

16V

TC2+

TC1+

LVDS_TX_1_CLK_P

R2819

10K

10K

C2815

0.1uF

16V

0.1uF

16V

DATA0

C2852

10uF

16V

10uF

16V

CONFIG_DONE

P2801

12505WS-10A00

1

2

3

4

5

6

7

8

9

10

11

2V5

L2803

/CSO

C2870

0.1uF

16V

0.1uF

16V

C2834

0.1uF

16V

0.1uF

16V

1V2

IC2800

EP3C55F484C8N

RXA0

N2

RXA0(N)

N1

RXA1

P2

RXA1(N)

P1

RXA2

R2

RXA2(N)

R1

RXA3

U2

RXA3(N)

U1

RXA4

V2

RXA4(N)

V1

RXACLK

T2

RXACLK(N)

T1

RXB0

B2

RXB0(N)

B1

RXB1

C2

RXB1(N)

C1

RXB2

F2

RXB2(N)

F1

RXB3

H2

RXB3(N)

H1

RXB4

J2

RXB4(N)

J1

RXBCLK

G2

RXBCLK(N)

G1

LVDS_TX_0_DATA1_N

AR2848

22

R2828

22

22

OPT

C2840

0.1uF

16V

0.1uF

16V

L2802

SYSCLK

TP[5]

IC2800

EP3C55F484C8N

GND_1

L10

GND_2

L11

GND_3

M10

GND_4

M11

GND_5

L12

GND_6

L13

GND_7

M12

GND_8

M13

GND_9

N11

GND_10

K11

GND_11

N12

GND_12

K12

GND_13

K13

GND_14

N13

GND_15

N10

GND_16

K10

GND_17

J9

GND_18

F12

GND_19

H12

GND_20

H13

GND_21

J15

GND_22

K16

GND_23

L15

GND_24

N15

GND_25

R13

GND_26

R11

GND_27

R9

GND_28

P8

GND_29

H14

GND_30

H10

GND_31

H8

GND_32

N8

GND_33

R7

GND_34

T8

GND_35

T12

GND_36

P16

GND_37

L8

GND_38

M7

GND_39

A1

GND_40

C5

GND_41

C9

GND_42

C11

GND_43

C12

GND_44

C14

GND_45

C16

GND_46

A22

GND_47

E20

GND_48

G20

GND_49

L20

GND_50

P19

GND_51

V20

GND_52

Y20

GND_53

AB22

GND_54

Y18

GND_55

Y16

GND_56

Y12

GND_57

Y11

GND_58

Y9

GND_59

Y5

GND_60

AB1

GND_61

N3

GND_62

U3

GND_63

W3

GND_64

D3

GND_65

F3

GND_66

K3

GNDA1

U5

GNDA2

E18

GNDA3

F5

GNDA4

V18

TP[2]

C2806

0.1uF

16V

0.1uF

16V

ASEL

TB2+

R2826

4.7K

MSEL[3]

C2804

0.1uF

16V

0.1uF

16V

TMS_FPGA

2V5

MSEL[1]

C2846

0.1uF

16V

0.1uF

16V

TP[4]

C2859

0.1uF

16V

0.1uF

16V

LVDS_TX_1_CLK_P

R2818

10K

10K

TP[1]

C2802

0.1uF

16V

0.1uF

16V

CONFIG_DONE

LVDS_TX_0_DATA4_P

LVDS_TX_0_DATA3_N

C2810

0.1uF

16V

0.1uF

16V

R2808

1K

R2816

1K

R2841

100

3V3

R2847

100

C2841

0.1uF

16V

0.1uF

16V

IC2800

EP3C55F484C8N

RAM_ADDR[12]

W10

RAM_ADDR[11]

Y15

RAM_ADDR[10]

AA6

RAM_ADDR[9]

U14

RAM_ADDR[8]

T16

RAM_ADDR[7]

AB10

RAM_ADDR[6]

R16

RAM_ADDR[5]

R14

RAM_ADDR[4]

Y17

RAM_ADDR[3]

U9

RAM_ADDR[2]

AB17

RAM_ADDR[1]

W14

RAM_ADDR[0]

AA17

RAM_LDQS_2

V10

RAM_LDQS_1

V13

RAM_UDQS_2

AB9

RAM_UDQS_1

Y13

RAM_CLK

U16

RAM_CLKN

U17

RAM_CKE

AA3

RAM_CSN

AB19

RAM_RASN

U15

RAM_CASN

Y14

RAM_WEN

Y4

RAM_BA[1]

AB3

RAM_BA[0]

Y6

RAM_ODT

AA19

RAM_LDM_2

V5

RAM_UDM_2

AA7

RAM_LDM_1

AA16

RAM_UDM_1

AA10

RAM_DATA[31]

AA9

RAM_DATA[30]

AA8

RAM_DATA[29]

V11

RAM_DATA[28]

AB8

RAM_DATA[27]

AB7

RAM_DATA[26]

U10

RAM_DATA[25]

Y8

RAM_DATA[24]

Y10

RAM_DATA[23]

V8

RAM_DATA[22]

W6

RAM_DATA[21]

W7

RAM_DATA[20]

Y3

RAM_DATA[19]

AA4

RAM_DATA[18]

Y7

RAM_DATA[17]

AA5

RAM_DATA[16]

W8

RAM_DATA[15]

AB14

RAM_DATA[14]

AA13

RAM_DATA[13]

AA15

RAM_DATA[12]

W13

RAM_DATA[11]

U12

RAM_DATA[10]

AB15

RAM_DATA[9]

AB13

RAM_DATA[8]

AA14

RAM_DATA[7]

T15

RAM_DATA[6]

W15

RAM_DATA[5]

AB20

RAM_DATA[4]

AB16

RAM_DATA[3]

V15

RAM_DATA[2]

AB18

RAM_DATA[1]

V14

RAM_DATA[0]

W17

LVDS_TX_0_DATA2_N

R2830

22

22

OPT

1V2

C2855

100pF

50V

100pF

50V

C2813

0.1uF

16V

0.1uF

16V

DCLK

C2868

0.1uF

16V

3V3

R2833

22

22

OPT

C2848

10uF

16V

10uF

16V

C2830

0.1uF

16V

0.1uF

16V

R2820

1K

1K

C2867

100pF

50V

C2819

0.1uF

16V

0.1uF

16V

TD1-

LVDS_TX_1_DATA2_P

R2809

1K

MSEL[1]

C2818

0.1uF

16V

0.1uF

16V

R2807

1K

LVDS_TX_0_DATA2_P

C2811

0.1uF

16V

0.1uF

16V

1V2

R2832

22

22

OPT

TE1-

LVDS_TX_1_DATA3_N

TDO_FPGA

TCLK2+

R2831

22

22

OPT

C2835

0.1uF

16V

0.1uF

16V

LVDS_TX_1_DATA4_P

3V3

ASEL

C2832

0.1uF

16V

0.1uF

16V

TC2-

R2806

22

22

C2857

0.1uF

16V

0.1uF

16V

R2811

22

TD2+

TB2-

TB1+

1V2

C2843

0.1uF

16V

0.1uF

16V

IC2800

EP3C55F484C8N

LVDS_OUT_R1[9]

D13

LVDS_OUT_R1[8]

A10

LVDS_OUT_R1[7]

B10

LVDS_OUT_R1[6]

D10

LVDS_OUT_R1[5]

E10

LVDS_OUT_R1[4]

A9

LVDS_OUT_R1[3]

B9

LVDS_OUT_R1[2]

A8

LVDS_OUT_R1[1]

B8

LVDS_OUT_R1[0]

C8

LVDS_OUT_G1[9]

A16

LVDS_OUT_G1[8]

B16

LVDS_OUT_G1[7]

A15

LVDS_OUT_G1[6]

B15

LVDS_OUT_G1[5]

D15

LVDS_OUT_G1[4]

A14

LVDS_OUT_G1[3]

B14

LVDS_OUT_G1[2]

A13

LVDS_OUT_G1[1]

B13

LVDS_OUT_G1[0]

C13

LVDS_OUT_B1[9]

C19

LVDS_OUT_B1[8]

D19

LVDS_OUT_B1[7]

A18

LVDS_OUT_B1[6]

B18

LVDS_OUT_B1[5]

C18

LVDS_OUT_B1[4]

D18

LVDS_OUT_B1[3]

A17

LVDS_OUT_B1[2]

B17

LVDS_OUT_B1[1]

C17

LVDS_OUT_B1[0]

E16

LVDS_OUT_PIXCLK1

A4

LVDS_OUT_DE1

B20

LVDS_OUT_HS1

A19

LVDS_OUT_VS1

B19

GPIO_0

D8

GPIO_1

A7

GPIO_2

B7

GPIO_3

C7

GPIO_4

D7

GPIO_5

A6

GPIO_6

B6

GPIO_7

C6

GPIO_8

A5

GPIO_9

B5

LVDS_OUT_R2[9]

M20

LVDS_OUT_R2[8]

M21

LVDS_OUT_R2[7]

M22

LVDS_OUT_R2[6]

L21

LVDS_OUT_R2[5]

L22

LVDS_OUT_R2[4]

K17

LVDS_OUT_R2[3]

K18

LVDS_OUT_R2[2]

K21

LVDS_OUT_R2[1]

K22

LVDS_OUT_R2[0]

J22

LVDS_OUT_G2[9]

P17

LVDS_OUT_G2[8]

P21

LVDS_OUT_G2[7]

P22

LVDS_OUT_G2[6]

N18

LVDS_OUT_G2[5]

N19

LVDS_OUT_G2[4]

N20

LVDS_OUT_G2[3]

N21

LVDS_OUT_G2[2]

N22

LVDS_OUT_G2[1]

M16

LVDS_OUT_G2[0]

M19

LVDS_OUT_B2[9]

T17

LVDS_OUT_B2[8]

T18

LVDS_OUT_B2[7]

T19

LVDS_OUT_B2[6]

T20

LVDS_OUT_B2[5]

R17

LVDS_OUT_B2[4]

R18

LVDS_OUT_B2[3]

R19

LVDS_OUT_B2[2]

R20

LVDS_OUT_B2[1]

R21

LVDS_OUT_B2[0]

R22

LVDS_OUT_PIXCLK2

H22

LVDS_OUT_DE2

U20

LVDS_OUT_HS2

U22

LVDS_OUT_VS2

U21

GPIO_10

V21

GPIO_11

V22

GPIO_12

AA21

GPIO_13

W21

GPIO_14

W22

GPIO_15

AA22

GPIO_16

W20

GPIO_17

Y21

GPIO_18

W19

GPIO_19

Y22

C2829

0.1uF

16V

0.1uF

16V

C2805

0.1uF

16V

0.1uF

16V

LVDS_TX_0_DATA2_P

R2836

100

LVDS_TX_1_DATA4_P

C2851

10pF

10pF

From STDP core power

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

10/01/xx

Jack B/D wafer

33 100

GP2_BCM_ATSC

+3.3V_NORMAL

DSUB_R

DSUB_G

DSUB_B

DSUB_VSYNC

DSUB_HSYNC

PC_R_IN

PC_L_IN

RGB_DDC_SDA

RGB_DDC_SCL

DSUB_DET

DSUB_5V

SPDIF_OUT

P3301

10022HS-25A02

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

JACK_B_VID_INCM

JACK_R_VID_INCM

JACK_G_VID_INCM

JACK_PC_LR_INCM

C3306

0.1uF

C3307

0.1uF

JACK_AV_CVBS_INCM

COMP1_Y

JACK_COMP1_VID_INCM

REAR_AV_L_IN

REAR_AV_CVBS

JACK_REAR_AV_LR_INCM

002:C6

COMP1_Pr

COMP1_DET

9:F5;9:G5

REAR_AV_R_IN

COMP1_Pb

REAR_AV_DET

9:G5;85:N23

C3304

0.1uF

R3302

0

FRC_RESET

232C_TXD

R3312

0

FPGA_DL

R3315

10K

1/16W

5%

P3302

TF05-41S

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

R3309

0

RESET_GPIO

R3301

0

R3307

0

I2C_NORMAL

LG5111_RESET

R3316

2.7K

OPT

POWER_CTRL_24V

C3302

0.1uF

D3301

5.5V

R3303

0

R3305

0

OPT

SDA3_3.3V

R3311

0

FPGA_DL

C3300

0.1uF

E_TMS

+3.5V_ST

E_TCK

C3301

0.1uF

DPRX_ML_L0P

INV_CTL

R3308

0

I2C_NORMAL

E_TDI

PWM_DIM

R3319

2.7K

OPT

AD1

RCLAMP0544T.TCT

DEVELOPMENT

1

8

2

7

3

6

4

5

9

R3317

2.7K

OPT

R3306

0

DPRX_ML_L1P

DP_CABLE_DET

AD2

RCLAMP0544T.TCT

DEVELOPMENT

1

8

2

7

3

6

4

5

9

R3318

2.7K

OPT

DPRX_AUX_N

PANEL_CTL

R3300

0

DPRX_ML_L0N

L/R_SYNC

R3314

0

FPGA_DL

C3303

0.1uF

232C_RXD

BLU_ON/OFF

R3304

0

OPT

R3310 33

RESET_GPIO

R3313

0

FPGA_DL

SCL3_3.3V

C3305

0.1uF

E_TDO

DPRX_AUX_P

DPRX_ML_L1N

D3.3V

Jack Board WAFER

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

09/10/xx

COMMON

RGB

84 100

RGB_DDC_SDA

D3500

ENKMC2838-T112

A1

C

A2

EDID_WP

RGB_HSYNC

IC3502

M24C02-RMN6T

RGB_EDID_ST

0IMMR00014A

3

E2

2

E1

4

VSS

1

E0

5

SDA

6

SCL

7

WC

8

VCC

RGB_DDC_SCL

+5V_NORMAL

RGB_VSYNC

IC3501

74F08D

74F08D

3

Q0

2

D0B

4

D1A

1

D0A

6

Q1

5

D1B

7

GND

8

Q2

9

D2A

10

D2B

11

Q3

12

D3A

13

D3B

14

VCC

R3505

22

+5V_NORMAL

R3510

2.7K

R3506

22

R

3

5

0

9

2

.

7

K

R3507

22

R3508

22

C3501

0.1uF

0.1uF

C3502

0.1uF 16V

C3503

18pF

50V

C3504

18pF

50V

R3512

22

R3511

22

R3514

100

R3513

10K

IC3502-*1

R1EX24002ASAS0A

RGB_EDID_RENESAS

DEV

3

A2

2

A1

4

VSS

1

A0

5

SDA

6

SCL

7

WP

8

VCC

DSUB_5V

DSUB_HSYNC

DSUB_VSYNC

RGB PC

BCM Reference

Click on the first or last page to see other 55LEX8-SA (CHASSIS:LJ03S) service manuals if exist.