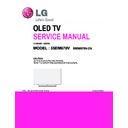

LG 55EM970V-ZA (CHASSIS:ED23E) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

R10204

4.7K

+2.5V_FPGA

+2.5V_FPGA

+2.5V_FPGA

C10207

0.47uF

25V

0.47uF

25V

C10205

0.47uF

25V

C10206

0.47uF

25V

FPGA_SPI_DO

C10203

10uF

16V

C10208

10uF

16V

OPT

+2.5V_FPGA

+2.5V_FPGA

/RESET2V5

R10216

0

OPT

+2.5V_FPGA

L10203

BLM18PG121SN1D

+2.5V_NORMAL

+3.3V_FPGA

+3.3V_NORMAL

L10204

BLM18PG121SN1D

R10209

22

R10205

4.7K

R

1

0

2

1

4

4

.

7

K

OPT

R

1

0

2

0

6

4

.

7

K

R10215

4.7K

OPT

FPGA_SPI_DI

FPGA_SPI_CLK

FPGA_SPI_CZ

FPGA_LINK3A_TXIN4_P

FPGA_LINK3A_TXIN3_P

FPGA_LINK3A_TXIN1_N

FPGA_LINK3A_TXIN1_P

FPGA_LINK3A_TXIN0_N

FPGA_LINK3A_TXIN0_P

FPGA_LINK3A_TXIN2_P

FPGA_LINK3A_TXCLKIN_N

FPGA_LINK3A_TXIN3_N

FPGA_LINK3A_TXIN4_N

FPGA_LINK3A_TXCLKIN_P

FPGA_LINK4A_TXIN4_N

FPGA_LINK4A_TXIN4_P

FPGA_LINK5A_TXIN1_N

FPGA_LINK4A_TXIN3_P

FPGA_LINK4A_TXIN1_N

FPGA_LINK4A_TXIN1_P

FPGA_LINK4A_TXIN0_N

FPGA_LINK4A_TXIN0_P

FPGA_LINK3A_TXIN2_N

FPGA_LINK5A_TXIN1_P

FPGA_LINK4A_TXIN3_N

FPGA_LINK5A_TXIN4_N

FPGA_LINK5A_TXIN3_N

FPGA_LINK5A_TXIN2_N

FPGA_LINK5A_TXIN0_N

FPGA_LINK5A_TXIN0_P

FPGA_LINK5A_TXIN2_P

FPGA_LINK5A_TXIN3_P

FPGA_LINK5A_TXIN4_P

R10217

22

R10220

22

+3.3V_FPGA

L10205

L10206

OPT

C10204

4.7uF

10V

R10221

10K

OPT

C10213

0.1uF

0.1uF

IC10202

AOZ1072AI-3

EAN60922902

3

AGND

2

VIN

4

FB

1

PGND

5

COMP

6

EN

7

LX_1

8

LX_2

C10211

22uF

10V

22uF

10V

+3.3V_NORMAL

L10207

CIC21J501NE

C10210

10uF

25V

10uF

25V

R10223

27K

1%

R10225

14K

1%

+12V

R10222

20K

C10209

10uF

25V

10uF

25V

C10215

100pF

50V

OPT

R10224

4.3K

1%

R10226

10K

L10209

3.6uH

NR8040T3R6N

C10214

2200pF

POWER_ON/OFF2_2

C10212

22uF

10V

22uF

10V

L10208

CIC21J501NE

OPT

+2.5V_FPGA

IC10101

XC6SLX16-3CSG324I

IO_L62P_D5_2

R3

IO_L65P_INIT_B_2

U3

IO_L63P_2

T4

IO_L49P_D3_2

U5

IO_L48N_RDWR_B_VREF_2

T5

IO_L43N_2

V7

IO_L43P_2

U7

IO_L46N_2

T7

IO_L41N_VREF_2

V8

IO_L41P_2

U8

IO_L31N_GCLK30_D15_2

T8

IO_L30N_GCLK0_USERCCLK_2

V10

IO_L30P_GCLK1_D13_2

U10

IO_L29N_GCLK2_2

T10

IO_L23P_2

U11

IO_L16N_VREF_2

T11

IO_L14N_D12_2

V13

IO_L14P_D11_2

U13

IO_L3N_MOSI_CSI_B_MISO0_2

T13

IO_L12N_D2_MISO3_2

V14

IO_L12P_D1_MISO2_2

T14

IO_L1N_M0_CMPMISO_2

T15

IO_L2N_CMPMOSI_2

V16

IO_L2P_CMPCLK_2

U16

IO_L45N_2

V6

IO_L65N_CSO_B_2

V3

IO_L63N_2

V4

IO_L49N_D4_2

V5

IO_L32N_GCLK28_2

V9

IO_L45P_2

T6

IO_L23N_2

V11

IO_L62N_D6_2

T3

IO_L1P_CCLK_2

R15

IO_L3P_D0_DIN_MISO_MISO1_2

R13

IO_L13P_M1_2

N12

IO_L13N_D10_2

P12

IO_L16P_2

R11

IO_L29P_GCLK3_2

R10

IO_L31P_GCLK31_D14_2

R8

IO_L32P_GCLK29_2

T9

IO_L46P_2

R7

IO_L48P_D7_2

R5

IO_L64P_D8_2

N5

IO_L64N_D9_2

P6

VCCO_2_1

P9

VCCO_2_3

R12

VCCO_2_2

R6

VCCO_2_6

U14

VCCO_2_4

U4

VCCO_2_5

U9

L3101

CIS21J121

OPT

R3115

2.4K

+2.5V_FPGA

R3114

22

FPGA_SPI_CLK

R3113

1K

1/16W

1%

OPT

C3107

0.1uF

L3102

CIS21J121

FPGA_SPI_DO

FPGA_SPI_CZ

R3112

1.8K

FPGA_SPI_DI

R3116

1K

1/16W

1%

OPT

+3.3V_FPGA

IC3101

W25Q40CLSNIG

3

WP[IO2]

2

DO[IO1]

4

GND

1

CS

5

DI[IO0]

6

CLK

7

HOLD[IO3]

8

VCC

Decouplingcapacitors forVCCO Bank2

FPGA Bank_2 :

2.5V Power Rail should be applied.

2.5V Power Rail should be applied.

Mode Pins --> determine configuration mode

Parallel configuration mode bus is auto-detected by the configuration logic.

M[1:0] = 10

CCLK Direction : Input

Bus Width : 8, 16

Parallel configuration mode bus is auto-detected by the configuration logic.

M[1:0] = 10

CCLK Direction : Input

Bus Width : 8, 16

R2

Vout=0.8*(1+R1/R2)

TYPICAL ? mA

+2.5V_FPGA

R1

2A

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

FPGA_A_SDA

FPGA_A_SCK

FPGA_LINK2A_SMB_CS

I2C_SCL2

I2C_SDA2

FPGA_LINK1A_SMB_CS

AUD_SCK

FRC3_RESET

AUD_LRCH

AUD_LRCK

EXT_COMPENSATION_DONE

I2C_BE_SCL1

+3.3V_FPGA

+3.3V_FPGA

FPGA_LINK2A_TXCLKIN_N

FPGA_LINK2A_TXIN2_N

FPGA_LINK2A_TXIN3_N

FPGA_LINK2A_TXIN1_N

FPGA_LINK2A_TXIN0_N

FPGA_LINK2A_TXIN4_N

FPGA_LINK1A_TXIN2_N

FPGA_LINK1A_TXIN1_N

FPGA_LINK1A_TXIN4_N

FPGA_LINK1A_TXIN3_N

FPGA_LINK1A_TXIN0_N

FPGA_LINK1A_TXCLKIN_N

FPGA_LINK1A_TXCLKIN_P

FPGA_LINK1A_TXIN2_P

FPGA_LINK1A_TXIN1_P

FPGA_LINK1A_TXIN0_P

FPGA_LINK1A_TXIN3_P

FPGA_LINK1A_TXIN4_P

FPGA_LINK2A_TXCLKIN_P

FPGA_LINK2A_TXIN0_P

FPGA_LINK2A_TXIN1_P

FPGA_LINK2A_TXIN3_P

FPGA_LINK2A_TXIN2_P

FPGA_LINK2A_TXIN4_P

+2.5V_FPGA

+2.5V_FPGA

R10303

100

1/16W

1%

+2.5V_FPGA

R10301

0

R10302

0

OPT

C10306

0.01uF

R10304

33

33

1/16W

1%

1%

C10303

0.47uF

25V

C10304

0.47uF

25V

C10305

0.47uF

25V

0.47uF

25V

C10311

0.47uF

25V

0.47uF

25V

C10309

0.47uF

25V

C10310

0.47uF

25V

AMP_MUTE

AMP_RESET_N

M_RFModule_RESET

R10305

0

M_REMOTE_TX

M_REMOTE_RX

M_RFModule_ISP

R10306

0

R10307

0

R10308

0

R10311

0

R10312

0

OPT

R10314

0

R10315

0

FPGA_XTAL_OUT

LINK1A_LOCK_N

C10301

10uF

16V

C10307

10uF

16V

R10317 0 OPT

R10316 0

OPT

IR

R10318

0

R10313

0

OPT

LINK2A_LOCK_N

LINK5A_LOCK_N

FPGA_XTAL_OUT

FPGA_LINK5A_SMB_CS

FPGA_LINK4A_SMB_CS

FPGA_LINK3A_SMB_CS

I2C_SCL3

I2C_SDA3

FPGA_DEBUG_1

FPGA_DEBUG_2

BACK_CHANNEL_LINK_READY

R10319

0

OPT

R10321

0

INV_CTL

R10323

0

OPT

OPTIC_GPIO1

BACK_CHANNEL_LINK_READY

OPTIC_BACK_CHANNEL

COMMERCIAL_12V_CTL

EL_VDD_ON_20V

EL_VDD_ON_20V

R10324

0

R10325

0

R10326

0

FPGA_LVDS_INFO

FRC3_FLASH_WP

AUD_MASTER_CLK

R10320

0

R10322

0

BACK_CHANNEL_P

R10218

10K

1/16W

1%

+2.5V_FPGA

C10313

0.1uF

R10219 10K

BACK_CHANNEL_N

C10314

0.1uF

I2C_BE_SDA1

C10302

4.7uF

10V

C10308

4.7uF

10V

R10338

0

OPT

R10339

0

OPT

I2C_SCL2

I2C_SDA2

Q10201

2N7002K

S

D

G

Q10202

2N7002K

S

D

G

R10340

0

OPT

R10341

0

OPT

+3.3V_FPGA

R10342

3.3K

R10343

3.3K

X10301

78.125MHz

4

VCC

1

EN/DIS

2

GND

3

OUTPUT

OPTIC_SERDES_RESET

C10312

5pF

50V

5pF

50V

IC10101

XC6SLX16-3CSG324I

IO_L44N_A2_M1DQ7_1

J18

IO_L45N_A0_M1LDQSN_1

K18

IO_L45P_A1_M1LDQS_1

K17

IO_L41N_GCLK8_M1CASN_1

K16

IO_L44P_A3_M1DQ6_1

J16

IO_L42P_GCLK7_M1UDM_1

L15

IO_L41P_GCLK9_IRDY1_M1RASN_1

K15

IO_L36N_A8_M1BA1_1

H14

IO_L29P_A23_M1A13_1

C17

IO_L29N_A22_M1A14_1

C18

IO_L31P_A19_M1CKE_1

D17

IO_L31N_A18_M1A12_1

D18

IO_L33P_A15_M1A10_1

E16

IO_L33N_A14_M1A4_1

E18

IO_L35N_A10_M1A2_1

F18

IO_L35P_A11_M1A7_1

F17

IO_L1N_A24_VREF_1

F16

IO_L1P_A25_1

F15

IO_L38N_A4_M1CLKN_1

G18

IO_L38P_A5_M1CLK_1

G16

IO_L43N_GCLK4_M1DQ5_1

H18

IO_L43P_GCLK5_M1DQ4_1

H17

IO_L37N_A6_M1A1_1

H16

IO_L37P_A7_M1A0_1

H15

IO_L49N_M1DQ11_1

P18

IO_L49P_M1DQ10_1

P17

IO_L51P_M1DQ12_1

T17

IO_L52P_M1DQ14_1

U17

IO_L48N_M1DQ9_1

N18

IO_L48P_HDC_M1DQ8_1

N17

IO_L50N_M1UDQSN_1

N16

IO_L74P_AWAKE_1

P15

IO_L74N_DOUT_BUSY_1

P16

IO_L47N_LDC_M1DQ1_1

M18

IO_L47P_FWE_B_M1DQ0_1

M16

IO_L50P_M1UDQS_1

N15

IO_L53N_VREF_1

N14

IO_L46N_FOE_B_M1DQ3_1

L18

IO_L46P_FCS_B_M1DQ2_1

L17

IO_L42N_GCLK6_TRDY1_M1LDM_1

L16

IO_L51N_M1DQ13_1

T18

IO_L52N_M1DQ15_1

U18

IO_L30P_A21_M1RESET_1

F14

IO_L30N_A20_M1A11_1

G14

IO_L32P_A17_M1A8_1

H12

IO_L32N_A16_M1A9_1

G13

IO_L34P_A13_M1WE_1

K12

IO_L34N_A12_M1BA2_1

K13

IO_L36P_A9_M1BA0_1

H13

IO_L39P_M1A3_1

J13

IO_L39N_M1ODT_1

K14

IO_L40P_GCLK11_M1A5_1

L12

IO_L40N_GCLK10_M1A6_1

L13

IO_L53P_1

M14

IO_L61P_1

L14

IO_L61N_1

M13

VCCO_1_1

E17

VCCO_1_2

G15

VCCO_1_3

J14

VCCO_1_4

J17

VCCO_1_5

M15

VCCO_1_6

R17

IC10101

XC6SLX16-3CSG324I

IO_L33N_0

A8

IO_L39N_0

A11

IO_L41N_0

A12

IO_L37N_GCLK12_0

A10

IO_L35N_GCLK16_0

A9

IO_L62N_VREF_0

A14

IO_L64N_SCP4_0

A15

IO_L66N_SCP0_0

A16

IO_L4N_0

A3

IO_L6N_0

A5

IO_L8N_VREF_0

A6

IO_L5N_0

A4

IO_L10N_0

A7

IO_L1P_HSWAPEN_0

D4

IO_L1N_VREF_0

C4

IO_L2P_0

B2

IO_L2N_0

A2

IO_L3P_0

D6

IO_L3N_0

C6

IO_L4P_0

B3

IO_L5P_0

B4

IO_L6P_0

C5

IO_L10P_0

C7

IO_L8P_0

B6

IO_L11P_0

D8

IO_L11N_0

C8

IO_L33P_0

B8

IO_L34P_GCLK19_0

D9

IO_L34N_GCLK18_0

C9

IO_L35P_GCLK17_0

B9

IO_L36P_GCLK15_0

D11

IO_L36N_GCLK14_0

C11

IO_L37P_GCLK13_0

C10

IO_L38P_0

G9

IO_L38N_VREF_0

F9

IO_L39P_0

B11

IO_L41P_0

B12

IO_L62P_0

B14

IO_L63P_SCP7_0

F13

IO_L63N_SCP6_0

E13

IO_L64P_SCP5_0

C15

IO_L65P_SCP3_0

D14

IO_L65N_SCP2_0

C14

IO_L66P_SCP1_0

B16

VCCO_0_2

B10

VCCO_0_3

B15

VCCO_0_1

B5

VCCO_0_5

D13

VCCO_0_4

D7

VCCO_0_6

E10

Decouplingcapacitors forVCCO Bank1

Decouplingcapacitors forVCCO Bank0

This isFPGA_CLINK2.This is anoption.

Control signal input

From main

From main

HEAD MICOM

-FRC & AMP

-FPGA & SERDES Rx/Tx

-FPGA & SERDES Rx/Tx

FPGA Bank_1 :

3,3V Power Rail should be applied.

3,3V Power Rail should be applied.

FPGA Bank_0 :

2.5V Power Rail should be applied.

2.5V Power Rail should be applied.

From MICOM

From L9 Main IC

Receive information from FPGA on DES boardvia ClearLink

MTK Test

To MICOM

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

C10405

5pF

50V

50V

C10404

5pF

50V

50V

BACK_CHANNEL_N

BACK_CHANNEL_P

SIGNAL_DET

TX_ENABLE

C10401

0.1uF

C10402

22uF

10V

22uF

10V

OPT

C10408

5pF

50V

50V

C10409

5pF

50V

50V

DSUB_G+

DSUB_B+

DSUB_R+

RGB_DDC_SCL

EDID_WP

RGB_DDC_SDA

DSUB_DET

RGB_5V

R10407 100

OPTIC_CABLE_DETECT

R10408

10K

+3.5V_ST

R10406

100

R10405

100

C10406

0.1uF

LINK4A_DOUT_N

LINK4A_DOUT_P

LINK3A_DOUT_P

LINK3A_DOUT_N

LINK5A_DOUT_P

LINK5A_DOUT_N

LINK2A_DOUT_N

LINK2A_DOUT_P

LINK1A_DOUT_P

LINK1A_DOUT_N

R10423

100K

OPT

OPTIC_POWER_CTRL

C10410

0.1uF

50V

0.1uF

50V

+3.5V_ST

R10412

0

OPT

R10415

10K

OPTIC_I2C_PULL_UP

Q10400

AO3407A

G

D

S

EEPROM_SDA

Q10403

2N7002K

S

D

G

R10431

33

OPT

C10412

0.1uF

50V

0.1uF

50V

I2C_CTRL

Q10402

2N7002K

S

D

G

C10411

0.1uF

50V

0.1uF

50V

R10427

33

OPT

C10407

1uF

OPTIC_CABLE_SDA

OPTIC_CABLE_SCL

EEPROM_SCL

OPTIC_CABLE_SDA

OPTIC_CABLE_SCL

OPTIC_I2C_PULL_UP

R10424

10K

R10425

10K

OPTIC_CABLE_SDA

OPTIC_CABLE_SCL

+3.3V_NORMAL

R10422

4.7K

OPT

P10401

FCBJS04RC1-LG

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

D10001

5.5V

R10430

20K

R10434

20K

71

LVDS_HIGH_MID

2011.04.30

Close to Pin B9,B10

THERMAL

THERMAL

THERMAL

THERMAL

THERMAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+3.3V_SERDES

+2.5V_SERDES

+2.5V_SERDES

+2.5V_SERDES

FPGA_A_SCK

FPGA_A_SDA

FPGA_LINK1A_SMB_CS

C10502

0.1uF

+3.3V_SERDES

R10500

1

C10543

0.1uF

+2.5V_SERDES

+3.3V_SERDES

R10505

10K

+3.3V_SERDES

R10507

0

+3.3V_SERDES

+3.3V_SERDES

R10512

2.2K

+3.3V_SERDES

+3.3V_SERDES

FPGA_A_SCK

FPGA_A_SDA

R10513

2.2K

R10514

2.2K

C10510

5pF

50V

5pF

50V

C10511

5pF

50V

5pF

50V

FPGA_LINK1A_TXIN1_P

FPGA_LINK1A_TXIN0_P

FPGA_LINK1A_TXIN4_N

FPGA_LINK1A_TXCLKIN_N

FPGA_LINK1A_TXIN1_N

FPGA_LINK1A_TXCLKIN_P

FPGA_LINK1A_TXIN2_P

FPGA_LINK1A_TXIN3_N

FPGA_LINK1A_TXIN0_N

FPGA_LINK1A_TXIN4_P

FPGA_LINK1A_TXIN3_P

FPGA_LINK1A_TXIN2_N

R10559 0

PWM_DIM

LINK1A_LOCK_N

R10533 0

OPTIC_SERDES_RESET

L10506

BLM18PG121SN1D

+3.3V_SERDES

+3.3V_NORMAL

+2.5V_SERDES

+2.5V_FPGA

L10507

BLM18PG121SN1D

R10534

0

OPT

R10503

4.7K

R10504

4.7K

R10506

4.7K

R10508

4.7K

OPT

R10509

4.7K

OPT

R10510

4.7K

OPT

R10537 0

FPGA_LINK3A_TXIN3_P

FPGA_LINK3A_TXIN3_N

FPGA_LINK3A_TXIN1_N

R10570

4.7K

FPGA_LINK3A_SMB_CS

FPGA_LINK3A_TXIN0_P

R10569

4.7K

+2.5V_SERDES

FPGA_A_SDA

SERDES_RESET

R10560

4.7K

OPT

R10557

2.2K

FPGA_LINK3A_TXIN4_P

FPGA_LINK3A_TXIN2_P

+3.3V_SERDES

FPGA_A_SCK

FPGA_LINK3A_TXCLKIN_N

FPGA_LINK3A_TXIN1_P

C10516

0.1uF

R10539

0

R10576

4.7K

OPT

C10514

0.1uF

+3.3V_SERDES

+3.3V_SERDES

R10520 0

+2.5V_SERDES

LINK3A_LOCK_N

+2.5V_SERDES

R10538 0

+3.3V_SERDES

R10575

4.7K

OPT

FPGA_LINK3A_TXIN2_N

FPGA_LINK3A_TXIN0_N

FPGA_LINK3A_TXCLKIN_P

FPGA_LINK3A_TXIN4_N

+3.3V_SERDES

+3.3V_SERDES

R10543

1

R10519 0

+2.5V_SERDES

R10563

4.7K

FPGA_LINK2A_TXIN3_P

FPGA_LINK2A_TXIN3_N

FPGA_LINK2A_TXIN1_N

R10568

4.7K

FPGA_LINK2A_SMB_CS

FPGA_LINK2A_TXIN0_P

R10572

4.7K

+2.5V_SERDES

FPGA_A_SDA

R10577

4.7K

OPT

R10553

2.2K

FPGA_LINK2A_TXIN4_P

FPGA_LINK2A_TXIN2_P

+3.3V_SERDES

FPGA_A_SCK

FPGA_LINK2A_TXCLKIN_N

FPGA_LINK2A_TXIN1_P

C10513

0.1uF

R10518

0

R10565

4.7K

OPT

C10512

0.1uF

+3.3V_SERDES

+3.3V_SERDES

R10541 0

+2.5V_SERDES

LINK2A_LOCK_N

+2.5V_SERDES

R10523 0

+3.3V_SERDES

R10562

4.7K

OPT

FPGA_LINK2A_TXIN2_N

FPGA_LINK2A_TXIN0_N

FPGA_LINK2A_TXCLKIN_P

FPGA_LINK2A_TXIN4_N

+3.3V_SERDES

+3.3V_SERDES

R10544

1

R10542 0

+2.5V_SERDES

R10574

4.7K

FPGA_LINK4A_TXIN3_P

FPGA_LINK4A_TXIN3_N

FPGA_LINK4A_TXIN1_N

R10573

4.7K

FPGA_LINK4A_SMB_CS

FPGA_LINK4A_TXIN0_P

R10571

4.7K

+2.5V_SERDES

FPGA_A_SDA

R10567

4.7K

OPT

R10552

2.2K

FPGA_LINK4A_TXIN4_P

FPGA_LINK4A_TXIN2_P

+3.3V_SERDES

FPGA_A_SCK

FPGA_LINK4A_TXCLKIN_N

FPGA_LINK4A_TXIN1_P

C10517

0.1uF

R10526

0

R10558

4.7K

OPT

C10515

0.1uF

+3.3V_SERDES

+3.3V_SERDES

R10540 0

+2.5V_SERDES

LINK4A_LOCK_N

+2.5V_SERDES

R10524 0

+3.3V_SERDES

R10566

4.7K

OPT

FPGA_LINK4A_TXIN2_N

FPGA_LINK4A_TXIN0_N

FPGA_LINK4A_TXCLKIN_P

FPGA_LINK4A_TXIN4_N

+3.3V_SERDES

+3.3V_SERDES

R10545

1

R10522 0

+2.5V_SERDES

R10564

4.7K

LINK2A_DOUT_N

LINK2A_DOUT_P

LINK1A_DOUT_N

LINK1A_DOUT_P

LINK3A_DOUT_P

LINK3A_DOUT_N

LINK4A_DOUT_P

LINK4A_DOUT_N

PWM_DIM2

ERROR_OUT

LOCAL_DIM_EN

BPL_IN

A_DIM

+3.3V_SERDES

LINK5A_DOUT_P

FPGA_LINK5A_TXIN4_N

FPGA_LINK5A_TXIN2_N

C10525

0.1uF

R10589

4.7K

OPT

R10582 0

FPGA_LINK5A_TXIN4_P

+2.5V_SERDES

FPGA_LINK5A_TXCLKIN_N

R10584

1

R10593

4.7K

OPT

R10590

4.7K

R10580

0

FPGA_LINK5A_SMB_CS

+3.3V_SERDES

+2.5V_SERDES

C10526

0.1uF

R10594

4.7K

OPT

R10591

4.7K

R10592

4.7K

+2.5V_SERDES

FPGA_LINK5A_TXIN3_P

R10587

2.2K

FPGA_LINK5A_TXCLKIN_P

+3.3V_SERDES

R10581 0

LINK5A_LOCK_N

R10583 0

LINK5A_DOUT_N

FPGA_LINK5A_TXIN1_N

FPGA_A_SDA

FPGA_LINK5A_TXIN0_P

FPGA_A_SCK

+3.3V_SERDES

FPGA_LINK5A_TXIN0_N

FPGA_LINK5A_TXIN2_P

FPGA_LINK5A_TXIN1_P

FPGA_LINK5A_TXIN3_N

+3.3V_SERDES

+2.5V_SERDES

+3.3V_SERDES

R10586

2.7K

R10501

2.7K

R10550

2.7K

R10551

2.7K

R10549

2.7K

SERDES_RESET

SERDES_RESET

SERDES_RESET

SERDES_RESET

SERDES_RESET

C10503

22uF

10V

22uF

10V

C10534

22uF

10V

22uF

10V

C10562

22uF

10V

22uF

10V

C10561

22uF

10V

22uF

10V

C10560

22uF

10V

22uF

10V

R10502

22K

R10517

22K

R10516

22K

R10515

22K

R10578

22K

C10507

0.1uF

C10549

0.1uF

C10532

0.1uF

C10551

0.1uF

C10546

0.1uF

C10506

0.1uF

C10552

0.1uF

C10531

0.1uF

C10548

0.1uF

C10545

0.1uF

C10550

0.1uF

C10505

0.1uF

C10529

0.1uF

C10553

0.1uF

C10564

0.1uF

C10558

0.1uF

C10554

0.1uF

C10504

0.1uF

C10533

0.1uF

C10557

0.1uF

C10559

0.1uF

C10555

0.1uF

C10500

0.1uF

C10501

0.1uF

C10544

0.1uF

C10524

0.1uF

C10530

0.1uF

C10563

0.1uF

C10547

0.1uF

C10556

0.1uF

C10537

10uF

16V

10uF

16V

C10538

0.1uF

16V

0.1uF

16V

C10535

10uF

16V

10uF

16V

C10536

0.1uF

16V

0.1uF

16V

C10542

0.1uF

C10539

0.1uF

C10540

0.1uF

C10541

0.1uF

C10565

0.1uF

IC10501

DS32EL0421

1

VDD33_1

2

NC_1

3

GPIO0

4

GPIO1

5

DC_B

6

RS

7

VDD25_1

8

NC_2

9

DE_EMPH0

10

DE_EMPH1

11

GPIO2

12

NC_3

13

NC_4

14

VOD_CTRL

15

VDD25_2

16

TXOUT0+

17

TXOUT0-

18

VDD25_3

19

NC_5

20

NC_6

21

NC_7

22

NC_8

23

NC_9

24

NC_10

25

VDD25_4

26

LF_REF

27

LF_CP

28

VDDPLL

29

RSVD

30

RESET

31

LOCK

32

SDA

33

SCK

34

SMB_CS

35

VDD25_5

36

VDD33_2

37

TXCLKIN+

38

TXCLKIN-

39

TXIN0+

40

TXIN0-

41

TXIN1+

42

TXIN1-

43

TXIN2+

44

TXIN2-

45

TXIN3+

46

TXIN3-

47

TXIN4+

48

TXIN4-

49

[EP]GND

IC10502

DS32EL0421

1

VDD33_1

2

NC_1

3

GPIO0

4

GPIO1

5

DC_B

6

RS

7

VDD25_1

8

NC_2

9

DE_EMPH0

10

DE_EMPH1

11

GPIO2

12

NC_3

13

NC_4

14

VOD_CTRL

15

VDD25_2

16

TXOUT0+

17

TXOUT0-

18

VDD25_3

19

NC_5

20

NC_6

21

NC_7

22

NC_8

23

NC_9

24

NC_10

25

VDD25_4

26

LF_REF

27

LF_CP

28

VDDPLL

29

RSVD

30

RESET

31

LOCK

32

SDA

33

SCK

34

SMB_CS

35

VDD25_5

36

VDD33_2

37

TXCLKIN+

38

TXCLKIN-

39

TXIN0+

40

TXIN0-

41

TXIN1+

42

TXIN1-

43

TXIN2+

44

TXIN2-

45

TXIN3+

46

TXIN3-

47

TXIN4+

48

TXIN4-

49

[EP]GND

IC10504

DS32EL0421

1

VDD33_1

2

NC_1

3

GPIO0

4

GPIO1

5

DC_B

6

RS

7

VDD25_1

8

NC_2

9

DE_EMPH0

10

DE_EMPH1

11

GPIO2

12

NC_3

13

NC_4

14

VOD_CTRL

15

VDD25_2

16

TXOUT0+

17

TXOUT0-

18

VDD25_3

19

NC_5

20

NC_6

21

NC_7

22

NC_8

23

NC_9

24

NC_10

25

VDD25_4

26

LF_REF

27

LF_CP

28

VDDPLL

29

RSVD

30

RESET

31

LOCK

32

SDA

33

SCK

34

SMB_CS

35

VDD25_5

36

VDD33_2

37

TXCLKIN+

38

TXCLKIN-

39

TXIN0+

40

TXIN0-

41

TXIN1+

42

TXIN1-

43

TXIN2+

44

TXIN2-

45

TXIN3+

46

TXIN3-

47

TXIN4+

48

TXIN4-

49

[EP]GND

IC10503

DS32EL0421

1

VDD33_1

2

NC_1

3

GPIO0

4

GPIO1

5

DC_B

6

RS

7

VDD25_1

8

NC_2

9

DE_EMPH0

10

DE_EMPH1

11

GPIO2

12

NC_3

13

NC_4

14

VOD_CTRL

15

VDD25_2

16

TXOUT0+

17

TXOUT0-

18

VDD25_3

19

NC_5

20

NC_6

21

NC_7

22

NC_8

23

NC_9

24

NC_10

25

VDD25_4

26

LF_REF

27

LF_CP

28

VDDPLL

29

RSVD

30

RESET

31

LOCK

32

SDA

33

SCK

34

SMB_CS

35

VDD25_5

36

VDD33_2

37

TXCLKIN+

38

TXCLKIN-

39

TXIN0+

40

TXIN0-

41

TXIN1+

42

TXIN1-

43

TXIN2+

44

TXIN2-

45

TXIN3+

46

TXIN3-

47

TXIN4+

48

TXIN4-

49

[EP]GND

IC10500

DS32EL0421

1

VDD33_1

2

NC_1

3

GPIO0

4

GPIO1

5

DC_B

6

RS

7

VDD25_1

8

NC_2

9

DE_EMPH0

10

DE_EMPH1

11

GPIO2

12

NC_3

13

NC_4

14

VOD_CTRL

15

VDD25_2

16

TXOUT0+

17

TXOUT0-

18

VDD25_3

19

NC_5

20

NC_6

21

NC_7

22

NC_8

23

NC_9

24

NC_10

25

VDD25_4

26

LF_REF

27

LF_CP

28

VDDPLL

29

RSVD

30

RESET

31

LOCK

32

SDA

33

SCK

34

SMB_CS

35

VDD25_5

36

VDD33_2

37

TXCLKIN+

38

TXCLKIN-

39

TXIN0+

40

TXIN0-

41

TXIN1+

42

TXIN1-

43

TXIN2+

44

TXIN2-

45

TXIN3+

46

TXIN3-

47

TXIN4+

48

TXIN4-

49

[EP]GND

72

100

Interface block

LG1152 A0

C10543,R10501 CLOSER TO IC10501

Place Close TO IC10501

R10549,C10516 CLOSER TO IC10503

Place Close TO IC10503

C10517,R10551 CLOSER TO IC10500

Place Close TO IC10500

C10513,R10550 CLOSER TO IC10502

Place Close TO IC10502

C10549,R10516 CLOSER TO IC10503

Place Close TO IC10503

Click on the first or last page to see other 55EM970V-ZA (CHASSIS:ED23E) service manuals if exist.