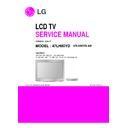

LG 47LH80YD (CHASSIS:LB91F) Service Manual ▷ View online

- 25 -

NTS

C/VSB

Half-NIM

TUN

ER

LCD/PD

P

DIGITAL T

V

P

R

O

C

ES

SOR

[MSD3

36

8

G

V]

HD

M

I

Sw

it

c

h

(4-to-1)

[T

D

A

9996]

IF

MiCOM

[W

T61P8S]

I2C_CH4

I2C_CH1

I2C_CH2

3.3V_2

3.3V_L

3.3V_2

1.8V_1

3.3V_2

5.0V_1

TX

_

S

E

L

1.26V_1

1.8V_D

DR

3.3V_1

I2C_CH4

5.0V_

ST

Composi

te

Video

IN

Componen

t

(Y,Pb,Pr)

IN

AN

T

/

CA

B

L

E

IN

RGB

IN

HD

M

I

IN

(x4)

5.0V_T

U

I2C_CH6

BA

C

K

TX

_

S

E

L

I2C_CH2

VSB

/Q

A

M

De

modu

lator

[L

GD

T3305]

3.3V_

V

S

B

1.2V_

V

S

B

I2C_CH2

TS

I2C_CH2

I2C_CH4

I2C_CH6

1.8V_1

A

/V

A

udio

-1

A

/V

A

udio

-2

CO

M

P

A

udio

-1

CO

M

P

A

udio

-2

RGB

A

udio

AN

A

L

O

G

AU

D

IO

IN

PUT

DIGI

T

A

L

AU

D

IO

IN

PUT

I2S

S/

P

D

IF

S/P

D

IF

OUT

FRONT

FE_S

IF

HD

M

I

Transmitter

[S

iI

9134]

HD

M

I

De

MUX

[PI3HDM

I1210

]

RF

Transcei

v

e

r

[S

B9

1

1

0

]

Ne

tw

ork

Processor

[S

B

9

1

20]

HD

M

I

R

e

ce

iv

er

[S

iI

9125]

HDM

I

SiBEA

M I/

F

Wireless Module

3.3V_L

2.5V_L

1.0V_L

2.5V_L

1.5V_L

1.2V_L

1.0V_L

3.3V_L

1.8V_L

HD

M

I

OUT

HDM

I

S

IF

0

P,

SIF

0

N

FE_S

IF

,

S

IFM

O

AU

L4, AU

R

4

PC_L_IN, PC

_R_IN

AU

L3, AU

R

3

C

O

M

P2_L_IN, C

OM

P

2_R_IN

AU

L2, AU

R

2

AV1_L_IN,

AV1_R_IN

AU

L1, AU

R

1

C

O

M

P1_L_IN, C

OM

P

1_R_IN

AU

L0, AU

R

0

AV2_L_IN,

AV2_R_IN

AUDIO

INPUT

SATURN6

PORT

Audio Path Diagram

BLOCK DIAGRAM_AV BOX

- 26 -

P5.0V_S

T

IC

502, D

DC

-PWR

(

IC

800)

,

IC

802, FR

ON

T-

T

/P

(

P

1103)

,

W

IR

ELES

S-

F

A

N

(

P

1104

),

SY

S

T

EM

-F

A

N

(

P110

5)

,

IC

1200

IC702

AP

1

1

1

7

LDO

D3.3V_L

IC400,

IC401, M

C

U

-RST

(

IC

402)

,

IC1103

L724

Q701

SI4925

M

O

SF

ET

D5.0V_W

W

IR

E

LE

SS_T

X

(

P

1102)

P3.3V

D

3

.3V_

A

V

DD

_M

PLL

IC100

D3.3V_2

IC101,

IC102,

IC104,

IC

80

0,

IC900,

IC1201

L703

L704,

L705

P6.0V

IC704

M

P

2212

DN

DC

/D

C

D3.3V_1

IC100, S6-

R

S

T

(

IC

103)

IC700

BA

50B

C

0

LDO

D5.0V_1

IC

104,

IC105, S

/PD

IF

(

J

K

601

), U

S

B

_

DB

G (

P

1101)

,

IC1101,

IC11

02,

IC1201

D

3

.3V_HDM

I

IC502

L501

IC703

A

P

111

7

LDO

D1.8V_1

IC800

D

1

.8V_HDM

I

IC502

L500

L716

IC705

M

P

2212

DN

DC

/D

C

D

1

.26V_VDDC

IC100

L711

IC1002

BA

50B

C

0

LDO

D5.0V_TU

TU1001

IC1003

BA

50B

C

0

LDO

D

5

.0V_VSB

SY

STEM

-F

A

N

(

P1

105

)

+5

V_

TU

L1009

D

3

.3V_PVSB

D3.3V_FE

L1005

IC1001

SC156

5

LDO

(RE

A

D

Y

)

D

1

.2V_PVSB

IC1000

SC421

5

LDO

IC1004

IC1004

D

3

.3V_

A

V

DD

_PVSB

D

3

.3V_D

V

D

D

_PVSB

L1007

L1008

D

1

.8V_DDR

IC701

SC421

5

LDO

L727

(RE

A

D

Y

)

IC

100,

IC300,

IC301

IC100

D

3

.3V_VDD

P

L101

Power Dissipation Diagram

BLOCK DIAGRAM_AV BOX

- 27 -

EEPR

OM

_SD

A

/S

C

L

CH

1, +

3.3V

I2CM

_SD

A

/S

C

K

0x

A

0

IC104

NVM

A

T

24C

5

1

2

B

W

TOUCHP

A

D

CapSense

IC

??

??

MI

CO

M

88

®

M

ast

er

FRONT

I/

F

H

D

M

I RX

WIHD TX

WiHD_TX

I/

F

FRONT

TOUCH

PA

D

WI

RE

LESS

T

X

HD

M

I_T

X_DDC

H

D

M

I

T

X

S

E

L

SignalSignal

Sw

itc

hing

b

y

by

.

(I

C

802)

WIRE

D c

o

nn

ection

connection

sc

heme

(J

UPII

T

E

R

model) model)

TV

RX

MI

CO

M

0x54

WT6

1

P

8

S

TV

R

X

0x

A

8

IC105

HDC

P

C

A

T

24WC

08W

SD

A

/SCL0

CH

2, +

3.3V

DDCR

_

D

A

/CK

0xFF

(Don’t care)

IC1004

DEMOD

LGD

T3305

0xC0

IC502

HD

M

I

S

W

TD

A

9

996

FE_DEM

OD_SD

A

/S

C

L

SD

A

/SCL_

HD

M

I

0 :

0x72

1 :

0x7

A

IC800

HD

M

I

T

X

Si

I9134C

TU

TD

A

9

996

_SD

A

/S

C

L

FE

_

T

UNER_

S

D

A

/S

C

L

CH

6, +

5.0V

RX1/TX1

0xFF

(Don’t care)

TU1001

TUNE

R

TD

VW-

H

154F

SD

A

/SCL1

CH

4, +

3.3V

GP

IO

60/62

0x50

IC401

MI

CO

M

W

T

61P8S

SD

A

/SC

L_MCU

MICOM_

S

D

A

/SCL_

S

+5

.0

V

GP

IO

A

0

/A

1

HD

M

I

O

U

T

(MONIT

OR)

0 :

0x60

1 :

0x68

Si

I9025

INFO

:

0x

A

0

CTRL : 0x

A

4

RX : 0

x

A

8

TX

: 0x

A

C

SB912

0

SD

A

/SC

L_WIH

D

I2C Map

BLOCK DIAGRAM_AV BOX

- 28 -

MSD3368

SATURN

6 (IC100)

1Gbit

D

DR2

(I

C

300)

A

_

DD

R2

_A

0

A

_

DD

R2

_A

1

A

_

DD

R2

_A

2

A

_

DD

R2

_A

3

A

_

DD

R2

_A

4

A

_

DD

R2

_A

5

A

_

DD

R2

_A

6

A

_

DD

R2

_A

7

A

_

DD

R2

_A

8

A

_

DD

R2

_A

9

A

_

DD

R2

_A

10

A

_

DD

R2

_A

11

A

_

DD

R2

_A

12

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

G8

G2

H7

H3

H1

H9

F1

F9

C8

C2

D7

D3

D1

D9

B1

B9

A

_

DD

R2

_D

Q

0

A

_

DD

R2

_D

Q

1

A

_

DD

R2

_D

Q

2

A

_

DD

R2

_D

Q

3

A

_

DD

R2

_D

Q

4

A

_

DD

R2

_D

Q

5

A

_

DD

R2

_D

Q

6

A

_

DD

R2

_D

Q

7

A

_

DD

R2

_D

Q

8

A

_

DD

R2

_D

Q

9

A

_

DD

R2

_D

Q

1

0

A

_

DD

R2

_D

Q

1

1

A

_

DD

R2

_D

Q

1

2

A

_

DD

R2

_D

Q

1

3

A

_

DD

R2

_D

Q

1

4

A

_

DD

R2

_D

Q

1

5

B

_

DD

R2

_A

0

B

_

DD

R2

_A

1

B

_

DD

R2

_A

2

B

_

DD

R2

_A

3

B

_

DD

R2

_A

4

B

_

DD

R2

_A

5

B

_

DD

R2

_A

6

B

_

DD

R2

_A

7

B

_

DD

R2

_A

8

B

_

DD

R2

_A

9

B

_

DD

R2

_A

10

B

_

DD

R2

_A

11

B

_

DD

R2

_A

12

B

_

DD

R2

_D

Q

0

B

_

DD

R2

_D

Q

1

B

_

DD

R2

_D

Q

2

B

_

DD

R2

_D

Q

3

B

_

DD

R2

_D

Q

4

B

_

DD

R2

_D

Q

5

B

_

DD

R2

_D

Q

6

B

_

DD

R2

_D

Q

7

B

_

DD

R2

_D

Q

8

B

_

DD

R2

_D

Q

9

B

_

DD

R2

_D

Q

1

0

B

_

DD

R2

_D

Q

1

1

B

_

DD

R2

_D

Q

1

2

B

_

DD

R2

_D

Q

1

3

B

_

DD

R2

_D

Q

1

4

B

_

DD

R2

_D

Q

1

5

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

G8

G2

H7

H3

H1

H9

F1

F9

C8

C2

D7

D3

D1

D9

B1

B9

5

1

2Mbit

NA

ND Fl

a

s

h

(I

C

102)

PCM_A

F/RB,

PF_OE,

PF_

C

E0,

PF_

C

E1,PF

_

A

L

E

,P

F_

W

E

,PF_

WP

I/O0

~

I/

O7

R

/B, R

E, C

E

CL

E. A

L

E

,W

E, WP

P

C

M_A[0] ~ A[7]

F-RBZ,

PF_OE,

PF_

C

E0,PF

_C

E

1

,

P

F

_ALE

,

P

F

_W

E

,

P

F

_AD15E

32

M

b

it

EEPR

O

M

(I

C

101)

SP

I_

DI

SP

I_

DO

SP

I_

CK

SP

I_

CS

S

P

I_

D

I

SP

I_

DO

SP

I_

CK

SP

I_

CS

D

I

D

O

C

K

CS

D

3

.3V_2

D1.8V_DDR

D1.8V_DDR

5

1

2

Mbit

DD

R2

(I

C

301)

D

3

.3V_2

Se

rial Flash

For boot

I2C Map

BLOCK DIAGRAM_AV BOX

Click on the first or last page to see other 47LH80YD (CHASSIS:LB91F) service manuals if exist.