LG 37LP1DA-ZA (CHASSIS:ML-03JA) Service Manual ▷ View online

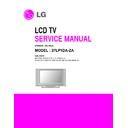

BLOCK DIAGRAM

- 30 -

ICS1

PW181

SCALER

ICF1

FLI2

3

1

0

DE INTE

RLA

CE

IC60

1

SiI9

0

2

1

TMDS R

x

IC760

M62320

P

o

rt

Ext.

IC50

0

X98

014

ADC

IC710

74HCT157

2 I

/p

Mux

IC5

VSP9

4

3

6

VIDEO

DECODER

IC4

M

2

MICOM

SD

A6

0

0

1

IC40

4

TEA51

1

4

A

RGB S/

W

ICS6

FLASH

MEMOR

Y

1M BYTE

IC30

1

NSP6241

DIGIT

AL

SOUND

PROCESSOR

IC90

5

PCA9

5

1

6

IIC HUB

ICIP1

IEP

LGDT4

4

1

0

IC90

2L

V

D

S

TH63

L

VDM3

8R

IC2-Fl

ash

ICF2

SDRAM

8MB

ESMT

ICS8,

9

PCA9

5

1

6

IIC HUB

ICS2

P2781A

SPREAD

IC

IC30

0

T

AS51

2

2

DIGIT

AL

AMP

IC750

M62320

P

o

rt

Ext.

IC700,701,

702

74L

VC244AD

2 I

/p

Mux

Digita

l Boar

d Inte

rface

IC1

AN158

6

5

A

A

V

S/

W

IC60

2

MSP4

4

1

0

k

IC90

7LA

7

2

2

2

IC20

0

H/P A

m

p

IC60

3

I2S S/W

ST32

3

2

CDR

IC207

MC14066B

IC20

6

24C21

IC202

24C21

SCL,SD

A

for EDID

SCL

SD

A(D)

SCL SD

A(A)

IC204

74F14

IC202

24C21

HDMI

EDID

RGB 8/8/8,

DE,

CLK,H/V S

YNC

YUV

CVBS_ SUB

,CVBS_Mai

n,YUV

R,G,B/FB

COM0,1SCL,S

D

A

(P)

COM0,1SCL,S

D

A

(M)

COM0,1SCL,S

D

A

(S)

RX,TX

RX,TX(P)

RX,TX(M)

RX,TX(S)

656 8BI

T

Y/C

,

H/V SYNC

Digital 656

8BIT

Y/

C

,

H/V SYNC

S

W

6

5

6

8BIT

Y/C

,

H/V SYNC

TEXT

R,G,B

FB

M2-CVBS

R,G,B/FB

YUV 4/2/

2 16BIT

CLK,H/V S

YNC

V

G

RGB 8/8/8

DE,CLK,

H/V SYNC

RGB 8/8/8

DE,CLK,

H/V SYNC

RGB

8/8/8

IIC ,PW

R0,1,VFD CS

,D

A,CLK,

P

ANEL S/W

,INV

CTL,A

V

ID

,

IR,SND MUTE,H/V S

YNC

RX,TX

TMDS(D

V

I)

TMDS

(HDMI)

IIS

(LR CLK,LR CH,

SCK,MCLK)

IIS(DTV

)

IIS(HDM

I)

DTV_CV

BS

,DTV

_YUV

A

n

a

lo

g

PC RGB

IIS_

soun

d

PC_a

u

d

io

RGB H/V

Ana

log H

/V

R

F

S

p

litte

r

TV

-In

TV

-In

TV

-In

A

n

a

lo

g

_CVBS

dtv

_sc1 o

u

t

X-stud

io RGB

,H/V

X-stud

io

L

/R

Scar

t2

_

V

Scar

t1

_

V

S1_

L

R

S2_

L

R

A

V

_

L

R

F

ron

t_L

R

Side

_

L

R

F

ron

t_V

Y

,Cb

,Cr

H/P

ou

t

H/P

Y1,2,3

¡

CLK

¡

EEFL

P

ANEL

L

R

PWM

LVDS_CTL,INV_BR,

AI_CTL,

HDMI/DTV SW

, AMP-RESET

,

RX/TX,RGB

SW

, LOGO ON

SCL/SD

A

SCL/SD

A

S_Y

,S_C

DTV_

LRo

u

t

Analog_LR out to S

1

MNT_LR out to S2

S1

S2

DVI-I

HDMI

RS-23

2

T

une

r

Digital Board

Interf

ace

Side A

V

Board

Interf

ace

F

ront A

V

Board

Interf

ace

Scar

t2

Vo

u

t

MNT CV

BS Ou

t

A

u

d

io

Dela

y

I

C

S

D

ATA

Ana

lo

g

_SIF

(F

rom T

uner)

Interf

ace

X-studio Board

BLOCK DIAGRAM DESCRIPTION

- 31 -

1) RF/Analog mode:

- Initially the signal is fed to the Analog Tuner through antenna

cable via RF splitter. Now, here the Audio and Video signals

are separated and sent accordingly (i.e. audio SIF to

MSP4410sound processor and Analog CVBS to AN15865

AV Switch).

are separated and sent accordingly (i.e. audio SIF to

MSP4410sound processor and Analog CVBS to AN15865

AV Switch).

- The video signal is then passed to the VSP9437B colour

decoder and scan rate converter IC as per the user selection

(PiP or Main). VSP9437B chip decodes the video signal and

convert it into ITU-R 656 8bit Y/C signal while, The audio

signal which was transferred to the MSP chip is processed

there and converted into digital audio signal.

(PiP or Main). VSP9437B chip decodes the video signal and

convert it into ITU-R 656 8bit Y/C signal while, The audio

signal which was transferred to the MSP chip is processed

there and converted into digital audio signal.

- The 656 8bit Y/C signal is now fed to the FLI2310 de-

interlacer IC which is used to make the signal progressive

and provides 4:2:2 16bit YC output while, The digital audio

signal is now transferred to the NSP6241 digital sound

processor. It converts the digital audio signal into the PWM

signal.

and provides 4:2:2 16bit YC output while, The digital audio

signal is now transferred to the NSP6241 digital sound

processor. It converts the digital audio signal into the PWM

signal.

- The 16 bit YUV video is then passed to the PW181 image

processor and scalar IC. PW181 supports advanced scaling

and video processing techniques such as format conversion

and producing high quality video for advanced displays while

the audio PWM signal is transferred to the TAS5122 digital

amplifier which amplifies the level of audio signal and feed

them to the left and right speaker output accordingly.

and video processing techniques such as format conversion

and producing high quality video for advanced displays while

the audio PWM signal is transferred to the TAS5122 digital

amplifier which amplifies the level of audio signal and feed

them to the left and right speaker output accordingly.

- The processed 24bit RGB signal from PW181 is passed to

LGDP4410 IC. It is an image enhancement chip which is

used to improve the picture quality.

used to improve the picture quality.

- Finally the improved quality 24bit RGB signal is transferred to

the LVDS chip which convert it into the low voltage

differential signal and interfaces it with the LCD display panel

through LVDS cable.

differential signal and interfaces it with the LCD display panel

through LVDS cable.

2) IDTV mode:

- Initially the signal is fed to the Digital Tuner through antenna

cable via RF splitter. It converts the signal into 8bit digital

data (called TS data) and pass it to the CI MAX chip which is

the hardware controller and PCMCIA card driver.

data (called TS data) and pass it to the CI MAX chip which is

the hardware controller and PCMCIA card driver.

- The 8bit output of CI MAX IC is sent to the buffer 74LVC244

which stores the data and check the validity incase of pay

channels from the information through PCMCIA card.

channels from the information through PCMCIA card.

- The final data is then passed to the STi5516B IC. It is the

MPEG video decoder and audio sub system. It produces the

CVBS signal(for main) and YUV(for PiP) and the audio signal

clocks and controls which are sent accordingly (i.e. audio I2S

to MSP4410 sound processor and DTV_CVBS and YUV to

AN15865 AV Switch).

CVBS signal(for main) and YUV(for PiP) and the audio signal

clocks and controls which are sent accordingly (i.e. audio I2S

to MSP4410 sound processor and DTV_CVBS and YUV to

AN15865 AV Switch).

- After these operations the audio and video signals follow the

same signal flow and processing as in case of RF/Analog

input.

input.

3) AV-1/2/3 mode:

- Initially the signal is fed directly to the AN15865 AV switch

through 3 different inputs (I.e. AV-1 from full SCART, AV-2

from half SCART and AV-3 from front A/V).

from half SCART and AV-3 from front A/V).

- The SCART Audio(AV1,AV2) are fed to MSP4410K through

the LA7222 switch for selecting appropriate mode while Front

LR(AV3) is directly fed to the MSP4410K sound processor

IC.

LR(AV3) is directly fed to the MSP4410K sound processor

IC.

- After these operations the audio and video signals follow the

same signal flow and processing as in case of RF/Analog

input.

input.

4) Component mode:

- Initially the video signal is fed to the AN15865 switch IC and

the audio signal is sent to the MSP4410 sound processor

directly from the component input jack. From here the audio

processing is same as in case of RF mode.

directly from the component input jack. From here the audio

processing is same as in case of RF mode.

- The YUV video signal is transferred to the X98014 ADC

which converts it into 24bit RGB and passes it to the FLI2310

de-interlacer IC and from there it follows the same signal flow

and processing as in case of RF mode.

de-interlacer IC and from there it follows the same signal flow

and processing as in case of RF mode.

5) DVI/DTV mode:

- Initially the TMDS signal is fed to the SiI 9021 TMDS receiver

chip which uses panel link digital technology to support high

resolution digital displays and HDTV.

resolution digital displays and HDTV.

- The TMDS Rxr IC converts the TMDS ssignal to 24 bit RGB

anddirectly transfers it to the PW181 scalar and image

processor and it follows the same processing as in case of

RF mode.

processor and it follows the same processing as in case of

RF mode.

- The audio signal here is fed to the MSP directly from PC

audio input and from here the audio processing is same as in

case of RF mode.

case of RF mode.

6) DVI/PC mode:

- Initially the PC RGB signal is fed to the AN15865 switch from

where it is transferred to X98014 ADC

- There it is converted into 24bit RGB signal and is transferred

to the PW181 scalar and image processor and it follows the

same processing as in case of RF mode.

same processing as in case of RF mode.

- The audio signal here is fed to the MSP directly from PC

audio input and from here the audio processing is same as in

case of RF mode.

case of RF mode.

7) HDMI mode:

- Initially the HDMI TMDS signal is fed to the SiI 9021 TMDS

receiver chip which uses panel link digital technology to

support high resolution digital displays and HDTV.

support high resolution digital displays and HDTV.

- The TMDS Rxr IC splits the HDMI TMDS signal into 24 bit

RGB and I2S audio signal It directly transfers 24bit RGB to

the PW181 scalar and image processor and it follows the

same processing as in case of RF mode.

the PW181 scalar and image processor and it follows the

same processing as in case of RF mode.

- The audio signal is fed to the MSP via I2S switch which

switches between HDMI I2S and DTV I2S. After that the

audio processing follows the same path as in any other

mode.

audio processing follows the same path as in any other

mode.

8) X-Studio mode:

- Initially the RGB/HV signal is fed to the AN15865 switching

IC and from there it follows the same path as in case of PC

RGB signal processing.

RGB signal processing.

- The X-Studio LR signal is directly input to the MSP4410K

sound processor thereafter it follows the same processing

route as in any other mode audio processing.

route as in any other mode audio processing.

9) S-Video mode:

- The S-video YC signal is directly transferred to the

VSP9437B video decoder IC from where it follows the same

processing path as in case of RF/TV mode.

processing path as in case of RF/TV mode.

- S-video doesn't have any separate audio port. It uses AV3

audio for sound output(front LR).

- 32 -

Digital

Side

A/V

Analog

Power

Jack

IR

Front

EPF

LED

Logo

1

2

3

4

5

8

9

15

16

17

18

19

20

13

14

10

10

11

12

6

7

WIRING DIAGRAM

Wiring Part List

NO.

PART NO.

1

6631T11020A

2

6631T11020Z

3

6631T25023N

4

6631T20039C

5

6631T25019N

6

6631T25024Q

7

6631T25023L

8

6631T20037D

9

6631T20032U

10

6631T11022B

11

6631T11023A

12

6631T20034V

13

6631T12007D

14

6631T20028W

15

6631T20034U

16

6631T20033D

17

6631T20028V

18

6631T20028X

21

6852TAZ012J

22

6852TAZ012W

- 33 -

EXPLODED VIEW

010

020

040

160

180

210

120

130

150

151

060

080

090

170

100

11

0

030

050

140

070

190

200

Click on the first or last page to see other 37LP1DA-ZA (CHASSIS:ML-03JA) service manuals if exist.