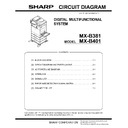

Sharp MX-B381 / MX-B401 (serv.man9) Service Manual ▷ View online

MX-B381/B401 CIRCUIT DIAGRAM AND PARTS LAYOUT 2 – 10

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

MSRCID1 [8]

MSRCID0 [8]

TSEC3_TXD[7:0] [12]

PCI_GNT1 [11]

PCI_GNT3 [11]

PCI_GNT2 [11]

PCI_GNT4 [11]

LB_ALE [6,8]

LB_OE

[6,8]

LB_CTL [8]

LGPL0

[8]

LGPL1

[8]

LGPL3

[8]

LGPL5

[8]

R130

4.7KJ

R107

4.7KJ

R148

X_4.7KJ

R111

4.7KJ

R113

4.7KJ

R123

4.7KJ

R132

X_4.7KJ

R109

X_4.7KJ

R160

4.7KJ

R108

X_4.7KJ

R147

4.7KJ

R117

X_4.7KJ

R166

X_4.7KJ

R166

X_4.7KJ

R167

X_4.7KJ

R167

X_4.7KJ

R126

X_4.7KJ

R161

X_4.7KJ

R146

4.7KJ

R112

4.7KJ

R116

4.7KJ

R133

X_4.7KJ

R149

4.7KJ

R115

X_4.7KJ

R131

4.7KJ

R124

X_4.7KJ

R125

X_4.7KJ

R110

4.7KJ

3

3

2

2

1

1

D

C

B

A

5/33 (7)

MX-B381/B401 CIRCUIT DIAGRAM AND PARTS LAYOUT 2 – 11

COP_TDI

COP_TMS

COP_TRST

COP_CKSTP_IN

COP_CKSTP_OUT

COP_CLK

WP_2KBIT

COP_VDD

COP_SRESET

COP_HRESET

COP_CKSTP_IN

COP_CKSTP_OUT

COP_SRESET

COP_HRESET

COP_TDI

SOC_JTAG_TDO

COP_TMS

COP_TRST

COP_CLK

GPO_EEP_nWP

WP_2KBIT

GPO_PD_SDDR_VTT1

GPO_SOCRSV5

GPO_EEP_nWP

GPO_PD_SDDR_VTT1

GPO_SOCRSV4

GPI_CNUPDATE

CCBCLK_OUT

GPO_GPHY1_RSTN

HRESET_REQ

HRESET_REQ

GPO_GPHY1_RSTN

S2_I2C_SDA

S2_I2C_SCL

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

STXD1_PIC

[32]

S1_I2C_SDA

[27,33]

S1_I2C_SCL

[27,33]

S2_I2C_SDA

[5,6,10]

S2_I2C_SCL

[5,6,10]

TMP_ANODE

[33]

TMP_CATHOD

[33]

SOC_RTC_CLK

[5]

SOC_SYSCLK

[5]

JTAG_CK1

[6,23,35]

SOC_JTAG_TDI

[35]

JTAG_TMS1

[6,23,35]

JTAG_RST1

[23,35]

SOC_JTAG_TDO

[35]

HRESET_4PLD

[6]

DMA_nREQ0_PLD1

[6]

DMA_ACK0_PLD1

[6]

DMA_nREQ1_PLD1

[6]

DMA_ACK1_PLD1

[6]

RTS_RS232C

[28]

TXD_RS232C

[28]

DSR_RS232C

[28]

CTS_RS232C

[28]

RXD_RS232C

[28]

MSRCID0

[7]

MSRCID1

[7]

GPO_nPD_SDDR_VTT1

[9]

DTR_RS232C

[28]

GPO_RES_PIC

[32]

SRXD1_PIC

[32]

REQPIC

[32]

CLR_PIC

[32]

GPI_PICPROG_READ

[32]

REQPIC

[32]

CLR_PIC

[32]

GPHY_RST

[23]

DCPWRON_BANK2 [5,6]

PWROFF_BK2

[3,4]

PWROFF_BK2_2

[6,35]

R228

10J

R205

1KJ

CP574

C112

1000pF(B)

R195

10KJ

CP184

CP588

R181

33J

R193

10KJ

CP

R225

4.7

CP108

R222

10J

R224

10KJ

CN1

X_BM11B-SRSS-TB

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

10

10

9

9

11

11

CP183

CP64

R204

1KJ

R171

10KJ

D34

LT1F67AF

A

K

R175

2.2KJ

R178

2.2KJ

CP520

CP423

CP573

R230

1KJ

CP516

CP408

C110

0.1uF(B)

C194

X_27

R168

10KJ

Y=

AB

AB

IC18

TC7SZ08FU(TE85L_F)

A

1

B

2

GND

3

Y

4

VCC

5

CP515

Y=/A

Schmitt

IC21

TC74LCX14FT(EL_K)

1A

1

1Y

2

2A

3

2Y

4

3A

5

3Y

6

GND

7

VCC

14

6A

13

6Y

12

5A

11

5Y

10

4A

9

4Y

8

R194

10KJ

R221

4.7

CP433

R227

10J

R218

4.7

CP571

R180

33J

R314

4.7KJ

CP185

R1

4.7

R89

2.2KJ

2.2KJ

CP569

R206

1KJ

R186

2.2KJ

CP197

R292

2.2KJ

R187

2.2KJ

CP432

CP517

R176

2.2KJ

CP195

CP518

R200

4.7

R294

X_2.2KJ

CP410

R199

X_

R192

0J

IC20

X_CAT24WC02(SOP8)

A0

1

A1

2

A2

3

GND

4

SDA

5

SCL

6

WP

7

VCC

8

C114

0.1uF(B)

CP

C115

0.1uF(B)

R201

X_

R177

2.2KJ

R174

10KJ

R170

10KJ

R183

X_2.2KJ

CP589

R196

10KJ

CP591

R226

10J

R184

X_2.2KJ

R296

X_2.2KJ

R220

4.7

CP373

CP181

R185

33J

R229

10J

CP590

R197

10KJ

CP572

R295

2.2KJ

CP519

CP

CP431

R179

2.2KJ

R223

4.7

CP15

R182

33J

R87

470J

CP570

C113

1000pF(B)

5

5

4

4

3

3

D

C

B

A

MFPC PWB (SoC: Local Bus/GPIO/UART/DMA/I2C)

MX-B381/B401 CIRCUIT DIAGRAM AND PARTS LAYOUT 2 – 12

SOC_ASLEEP

SOC_SDA1

SOC_SCL1

SOC_SDA2

SOC_SCL2

SOC_LSYNC

SOC_LAD0

SOC_LAD1

SOC_LAD2

SOC_LAD3

SOC_LAD4

SOC_LAD5

SOC_LAD6

SOC_LAD7

SOC_LAD8

SOC_LAD9

SOC_LAD10

SOC_LAD11

SOC_LAD12

SOC_LAD13

SOC_LAD14

SOC_LAD15

SOC_LAD16

SOC_LAD17

SOC_LAD18

SOC_LAD19

SOC_LAD20

SOC_LAD21

SOC_LAD22

SOC_LAD23

SOC_LAD24

SOC_LAD25

SOC_LAD26

SOC_LAD27

SOC_LAD28

SOC_LAD29

SOC_LAD30

SOC_LAD31

SOC_LDP3

SOC_LDP2

SOC_LDP1

SOC_LDP0

K_OUT

GPI_CNUPDATE

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

3R3V

DGND

GND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

SOC_LAD[31:0] [6]

SOC_LCS0 [6]

LB_LWE0 [6,7]

LB_ALE [6,7]

LB_OE

[6,7]

LGPL0

[7]

LGPL1

[7]

LGPL3

[7]

LGPL5

[7]

LB_CTL [7]

LB_LWE1 [7]

LB_LWE2 [7]

LB_LWE3 [7]

SOC_LA27 [7]

SOC_LA28 [7]

SOC_LA29 [7]

SOC_LA30 [7]

SOC_LA31 [7]

MFP_INT2 [6]

HDD_INT2 [6]

RTC_INTA [27]

PHY_INT_N [23]

nPOF

[32]

nFAX12_PIC_INT [32]

SOC_LCS1 [6]

SOC_LCS2 [6]

SOC_LCS3 [6]

SOC_LCS4 [6]

SOC_LCS5 [6]

SOC_LCS6 [6]

SOC_LCS7 [6]

nLBACC_TMN [6]

USB_SEL_SW [30]

RTC_INTB [27]

CP522

LOCA

L

BUS

G

PIO

DMA

UAR

T

I2

C

JT

A

G

&

TES

T

S

Y

S

TEM

CON

TRO

L

PIC

SoC MPC8533(800M)

IC19C

IIC1_SDA_IO

AH21

IIC1_SCL_IO

AG21

IIC2_SDA_IO

AG14

IIC2_SCL_IO

AG13

GPOUT[0]_O

AF22

GPOUT[1]_O

AH23

GPOUT[2]_O

AG27

GPOUT[3]_O

AH25

GPOUT[4]_O

AF21

GPOUT[5]_O

AF25

GPOUT[6]_O

AG26

GPOUT[7]_O

AF26

GPIN[0]_I

AH24

GPIN[1]_I

AG24

GPIN[2]_I

AD23

GPIN[3]_I

AE21

GPIN[4]_I

AD22

GPIN[5]_I

AF23

GPIN[6]_I

AG25

GPIN[7]_I

AE20

DMA_DREQ[0]_I

AA10

DMA_DREQ[1]_I

AA11

DMA_DDONE[0]_O

AA7

DMA_DDONE[1]_O

Y11

DMA_DACK[0]_O (PU)

Y13

DMA_DACK[1]_O (PU)

Y12

HRESET_REQ_O

AG15

HRESET_I

AG16

SRESET_I

AG19

CKSTP_IN_I

AH5

CKSTP_OUT_O (PU)

AA12

L1_TSTCLK_I

AC20

L2_TSTCLK_I

AE17

LCS[0]_O

K18

LCS[1]_O

G19

LCS[2]_O

H19

LCS[3]_O

H20

LCS[4]_O

G16

LCS[5]/DMA_REQ2_IO H16

LCS[6]/DMA_DACK2_O J16

LCS[7]/DMA_DDONE2_O L18

LCLK[0]_O H24

LCLK[1]_O J24

LCLK[2]_O H25

LCKE_O

L17

LBCTL_O (PU) J25

LALE_O (PU) J26

UART_SOUT[0]_O

AH7

UART_SOUT[1]_O

AF7

UART_SIN[0]_I

AG7

UART_SIN[1]_I

AH6

UART_RTS[0]_O

AG8

UART_RTS[1]_O

AG9

UART_CTS[0]_I

AH8

UART_CTS[1]_I

AF6

TRIG_IN_I

AC5

TRIG_OUT/READY/QUIESCE_O

AB5

MSRCID[0]_O (PU)

Y7

MSRCID[1]_O (PU)

W9

MSRCID[2]_O

AA9

MSRCID[3]_O

AB6

MSRCID[4]_O

AD5

MDVAL_O

Y8

CLK_OUT_O

AE16

RTC_I

AF15

SYSCLK_I

AH16

TEMP_ANODE

Y3

TEMP_CATHOD

AA3

ASLEEP_O

AH17

TCK_I

AG28

TDI_I (PU)

AH28

TDO_O

AF28

TMS_I (PU)

AH27

TRST_I (PU)

AH22

LSSD_MODE_I

AH19

TEST_SEL_I

AH13

LAD[00]_IO K22

LAD[01]_IO L21

LAD[02]_IO L22

LAD[03]_IO K23

LAD[04]_IO K24

LAD[05]_IO L24

LAD[06]_IO L25

LAD[07]_IO K25

LAD[08]_IO L28

LAD[09]_IO L27

LAD[10]_IO K28

LAD[11]_IO K27

LAD[12]_IO J28

LAD[13]_IO H28

LAD[14]_IO H27

LAD[15]_IO G27

LAD[16]_IO G26

LAD[17]_IO F28

LAD[18]_IO F26

LAD[19]_IO F25

LAD[20]_IO E28

LAD[21]_IO E27

LAD[22]_IO E26

LAD[23]_IO F24

LAD[24]_IO E24

LAD[25]_IO C26

LAD[26]_IO G24

LAD[27]_IO E23

LAD[28]_IO G23

LAD[29]_IO F22

LAD[30]_IO G22

LAD[31]_IO G21

LA[27]_O (PU) L19

LA[28]_O (PU) K16

LA[29]_O (PU) K17

LA[30]_O (PU) H17

LA[31]_O (PU) G17

UDE_I

AH15

MCP_I

AG18

IRQ_OUT_O

AD14

IRQ[0]_I

AG22

IRQ[1]_I

AF17

IRQ[2]_I

AD21

IRQ[3]_I

AF19

IRQ[4]_I

AG17

IRQ[5]_I

AF16

IRQ[6]_I

AC23

IRQ[7]_I

AC22

IRQ[8]_I

AC19

IRQ[9]/DMA_DREQ3_I AG20

IRQ[10]/DMA_DACK3_IO AE27

IRQ[11]/DMA_DDONE3_IO AE24

LDP[0]_IO K26

LDP[1]_IO G28

LDP[2]_IO B27

LDP[3]_IO E25

LGPL0/LSDA10_O (PU) J20

LGPL1/LSDWE_O (PU) K20

LGPL2/LOE/LSDRAS_O (PU) G20

LGPL3/LSDCAS_O (PU) H18

LGPL4/LGTA/LUPWAIT/LPBSE_IO L20

LGPL5_O (PU) K19

LSYNC_IN_I D27

LSYNC_OUT_O D28

LWE0/LBS0/LSDDQM[0]_O (PU) J22

LWE1/LBS1/LSDDQM[1]_O (PU) H22

LWE2/LBS2/LSDDQM[2]_O (PU) H23

LWE3/LBS3/LSDDQM[3]_O (PU) H21

R188 10KJ

CP536

R189 10KJ

CP598

P588

CP538

CP537

CP577

4.7KJ

R385

10KJ

10KJ

CP647

R215

10KJ

CP542

CP584

P423

R213

10KJ

CP532

CP136

C194

X_27pF(CH)

CP575

CP524

CP523

CP540

CP526

4.7KJ

C119

220pF(CH)

4.7KJ

R384

4.7KJ

C579

0.1uF(B)

R173

4.7KJ

CP533

R172

4.7KJ

R190 10KJ

R382

4.7KJ

CP535

CP509

CP539

R207

10KJ

CP525

CP528

CP582

R211

10KJ

C120

220pF(CH)

CP531

4.7KJ

C117

220pF(CH)

CP586

CP581

R214

10KJ

CP579

CP508

R203

10KJ

X_10J

C122

220pF(CH)

CP529

R202

10KJ

CP527

C116

220pF(CH)

CP578

R219

10KJ

C121

220pF(CH)

X_10J

R217

10KJ

0KJ

CP648

R208

10KJ

CP530

C118

220pF(CH)

4.7KJ

CP585

CP541

R212

10KJ

CP580

197

0KJ

R383

10KJ

10KJ

R216

10KJ

CP576

CP534

R191 10KJ

CP583

4.7KJ

CP595

ON

SW2

KSDA22

A1

1

A2

2

B1

4

B2

3

3

3

2

2

1

1

D

C

B

A

6/33 (8)

MX-B381/B401 CIRCUIT DIAGRAM AND PARTS LAYOUT 2 – 13

S_DDR1_AD0

S_DDR1_AD1

S_DDR1_AD2

S_DDR1_AD3

S_DDR1_AD4

S_DDR1_AD5

S_DDR1_AD6

S_DDR1_AD7

S_DDR1_AD8

S_DDR1_AD9

S_DDR1_AD10

S_DDR1_AD11

S_DDR1_AD12

S_DDR1_AD13

S_DDR1_CS0

S_DDR1_CS1

S_DDR1_CS2

S_DDR1_CS3

S_DDR1_BA1

S_DDR1_BA0

S_DDR1_BA2

S_DDR1_ODT3

S_DDR1_ODT0

S_DDR1_ODT1

S_DDR1_ODT2

S_DDR1_DQ51

S_DDR1_DQ48

S_DDR1_DQ53

S_DDR1_DQ52

S_DDR1_DQ50

S_DDR1_DQ54

S_DDR1_DQ55

S_DDR1_DQ49

S_DDR1_DQ18

S_DDR1_DQ16

S_DDR1_DQ21

S_DDR1_DQ19

S_DDR1_DQ20

S_DDR1_DQ23

S_DDR1_DQ22

S_DDR1_DQ17

S_DDR1_DQ56

S_DDR1_DQ63

S_DDR1_DQ60

S_DDR1_DQ59

S_DDR1_DQ58

S_DDR1_DQ57

S_DDR1_DQ62

S_DDR1_DQ61

S_DDR1_DQ3

S_DDR1_DQ7

S_DDR1_DQ6

S_DDR1_DQ2

S_DDR1_DQ5

S_DDR1_DQ0

S_DDR1_DQ4

S_DDR1_DQ1

S_DDR1_DQ9

S_DDR1_DQ15

S_DDR1_DQ8

S_DDR1_DQ13

S_DDR1_DQ10

S_DDR1_DQ14

S_DDR1_DQ11

S_DDR1_DQ12

S_DDR1_DQ36

S_DDR1_DQ35

S_DDR1_DQ34

S_DDR1_DQ32

S_DDR1_DQ37

S_DDR1_DQ33

S_DDR1_DQ39

S_DDR1_DQ38

S_DDR1_DM1

S_DDR1_DM2

S_DDR1_DM3

S_DDR1_DM4

S_DDR1_DM5

S_DDR1_DM6

S_DDR1_DM7

S_DDR1_DQ44

S_DDR1_DQ45

S_DDR1_DQ46

S_DDR1_DQ40

S_DDR1_DQ43

S_DDR1_DQ42

S_DDR1_DQ47

S_DDR1_DQ41

S_DDR1_DQ31

S_DDR1_DQ25

S_DDR1_DQ24

S_DDR1_DQ27

S_DDR1_DQ26

S_DDR1_DQ28

S_DDR1_DQ30

S_DDR1_DQ29

S_DDR1_DM0

SDDR_ECC0

SDDR_ECC1

SDDR_ECC2

SDDR_ECC3

SDDR_ECC4

SDDR_ECC5

SDDR_ECC6

SDDR_ECC7

SDDR_DM8

SDDR_DQSP8

SDDR_DQSN8

SDDR_DM8

SDDR_DQSN8

SDDR_DQSP8

1R8V

0R9V_DDR1VREF

DGND

DGND

1R8V

S_DDR1_CKE0

[10]

S_DDR1_CKE1

[10]

S_DDR1_AD[13:0] [10]

S_DDR1_BA[2:0] [10]

S_DDR1_CS[3:0] [10]

S_DDR1_ODT[3:0]

[10]

S_DDR1_DQ[63:0] [10]

S_DDR1_DQS0N [1

S_DDR1_DQS1N [1

S_DDR1_DQS1P [10

S_DDR1_DQS2N [1

S_DDR1_DQS2P [10

S_DDR1_DQS3N [1

S_DDR1_DQS3P [10

S_DDR1_DQS4N [1

S_DDR1_DQS4P [10

S_DDR1_DQS5N [1

S_DDR1_DQS5P [10

S_DDR1_DQS6N [1

S_DDR1_DQS6P [10

S_DDR1_DQS7N [1

S_DDR1_DQS7P [10

S_DDR1_DQS0P [10

S_DDR1_CK1P

[10]

S_DDR1_CK1N

[10]

S_DDR1_CK2P

[10]

S_DDR1_CK2N

[10]

S_DDR1_CK3P

[10]

S_DDR1_CK3N

[10]

S_DDR1_RAS

[10]

S_DDR1_CAS

[10]

S_DDR1_WE

[10]

S_DDR1_CK0P

[10]

S_DDR1_CK0N

[10]

S_DDR1_CKE2

[10]

S_DDR1_CKE3

[10]

BR4

1KJx4

8

1

7

2

6

3

5

4

BR5

1KJx4

8

1

7

2

6

3

5

4

R232

18.2F

R231

18.2F

C802

1uF(1608:B)

C130

0.1uF(B)

DDR

2

SDRAM

I/F

SoC MPC8533(800M)

IC19A

MCKP[0]_O

A9

MCKP[1]_O

J11

MCKP[2]_O

J6

MCKP[3]_O

A8

MCKP[4]_O

J13

MCKP[5]_O

H8

MCKN[0]_O

B9

MCKN[1]_O

H11

MCKN[2]_O

K6

MCKN[3]_O

B8

MCKN[4]_O

H13

MCKN[5]_O

J8

MCKE[0]_O

H10

MCKE[1]_O

K10

MCKE[2]_O

G10

MCKE[3]_O

H9

MCAS_O

E7

MRAS_O

C5

MWE_O

B4

MECC[0]_IO

G12

MECC[1]_IO

D14

MECC[2]_IO

F11

MECC[3]_IO

C11

MECC[4]_IO

G14

MECC[5]_IO

F14

MECC[6]_IO

C13

MECC[7]_IO

D12

MDM[8]_O

F13

MDQSP[8]_IO

D13

MDQSN[8]_IO

E13

MDIC[0]_IO

H15

MDIC[1]_IO

K15

MA[00]_O B7

MA[01]_O G8

MA[02]_O C8

MA[03]_O A10

MA[04]_O D9

MA[05]_O C10

MA[06]_O A11

MA[07]_O F9

MA[08]_O E9

MA[09]_O B12

MA[10]_O A5

MA[11]_O A12

MA[12]_O D11

MA[13]_O F7

MA[14]_O E10

MA[15]_O F10

MBA[0]_O A4

MBA[1]_O B5

MBA[2]_O B13

MCS[0]_O D3

MCS[1]_O H6

MCS[2]_O C4

MCS[3]_O G6

MDQ[00]_IO A26

MDQ[01]_IO B26

MDQ[02]_IO C22

MDQ[03]_IO D21

MDQ[04]_IO D25

MDQ[05]_IO B25

MDQ[06]_IO D22

MDQ[07]_IO

E21

MDM[0]_O C25

MDQSP[0]_IO C23

MDQSN[0]_IO D24

MDQ[08]_IO A24

MDQ[09]_IO A23

MDQ[10]_IO B20

MDQ[11]_IO A20

MDQ[12]_IO A25

MDQ[13]_IO B24

MDQ[14]_IO B21

MDQ[15]_IO A21

MDM[1]_O B23

MDQSP[1]_IO A22

MDQSN[1]_IO B22

MDQ[16]_IO E19

MDQ[17]_IO D19

MDQ[18]_IO E16

MDQ[19]_IO C16

MDQ[20]_IO F19

MDQ[21]_IO F18

MDQ[22]_IO F17

MDQ[23]_IO D16

MDM[2]_O D18

MDQSP[2]_IO E17

MDQSN[2]_IO C18

MDQ[24]_IO B18

MDQ[25]_IO A18

MDQ[26]_IO A15

MDQ[27]_IO B14

MDQ[28]_IO B19

MDQ[29]_IO A19

MDQ[30]_IO A16

MDQ[31]_IO B15

MDM[3]_O B17

MDQSP[3]_IO B16

MDQSN[3]_IO A17

MDQ[32]_IO D1

MDQ[33]_IO F3

MDQ[34]_IO G1

MDQ[35]_IO H2

MDQ[36]_IO E4

MDQ[37]_IO G5

MDQ[38]_IO H3

MDQ[39]_IO J4

MDM[4]_O G4

MDQSP[4]_IO K5

MDQSN[4]_IO J5

MDQ[40]_IO B2

MDQ[41]_IO C3

MDQ[42]_IO F2

MDQ[43]_IO G2

MDQ[44]_IO A2

MDQ[45]_IO B3

MDQ[46]_IO E1

MDQ[47]_IO F1

MDM[5]_O C2

MDQSP[5]_IO D2

MDQSN[5]_IO C1

MDQ[48]_IO L5

MDQ[49]_IO L4

MDQ[50]_IO N3

MDQ[51]_IO P3

MDQ[52]_IO J3

MDQ[53]_IO K4

MDQ[54]_IO N4

MDQ[55]_IO P4

MDM[6]_O L3

MDQSP[6]_IO M3

MDQSN[6]_IO M4

MDQ[56]_IO J1

MDQ[57]_IO K1

MDQ[58]_IO P1

MDQ[59]_IO R1

MDQ[60]_IO J2

MDQ[61]_IO K2

MDQ[62]_IO N1

MDQ[63]_IO R2

MDM[7]_O L2

MDQSP[7]_IO P2

MDQSN[7]_IO M2

MODT[0]_O

E5

MODT[1]_O

H7

MODT[2]_O

E6

MODT[3]_O

F6

MVREF

A28

BR3

1KJx4

8

1

7

2

6

3

5

4

5

5

4

4

3

3

D

C

B

A

MFPC PWB (SoC: DDR2 I/F)

Click on the first or last page to see other MX-B381 / MX-B401 (serv.man9) service manuals if exist.