Sharp SD-AT100 (serv.man6) Service Manual ▷ View online

– 111 –

SD-AT100H

1

VDDL

Input

L channel digital output section power terminal

2

OUTL (+)

Output

L channel forward output terminal

3

OUTL (–)

Output

L channel reverse output terminal

4

GNDD

—

Digital output section ground terminal

5

OUTR (–)

Output

R channel reverse output terminal

6

OUTR (+)

Output

R channel forward output terminal

7

VDDR

Input

R channel digital output section power terminal

8

VDDX

Input

Oscillation section power terminal

9

XI

Input

Quartz oscillator connection terminal. Clock necessary for the system is generated.

10

XO

Output

Quartz oscillator connection terminal. Clock necessary for the system is generated.

11

GNDX

—

Oscillation section ground terminal

12*

MCK

Output

System clock output terminal

13

TEST

Input

Test terminal. As usual, it is used at "L".

14

NFR1 (+)

Input

R channel forward signal feedback input terminal

15

NFR2 (–)

Input

R channel reverse signal feedback input terminal

16

GNDA

—

Analog ground terminal for AD converter

17

Rch IN

Input

R channel analog input terminal

18

Rch Vref

Input

Reference voltage terminal for R channel

19

Lch Vref

Input

Reference voltage terminal for L channel

20

Lch IN

Input

L channel analog input terminal

21

RESET

Input

Reset terminal. It is reset with "L".

22

NFL2 (–)

Input

L channel reverse signal feedback input terminal

23

NFL1 (+)

Input

L channel forward signal feedback input terminal

24

VDDA

Input

Analog current terminal for AD converter

Pin No.

Port Name

Input/Output

Function

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

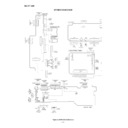

ICA100 RH-iX2815AFZZ: 7th Order Modulation Conversion LSI (IX2815AF)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VDDL

VDDA

NFL1(+)

NFL2(–)

RESET

Lch IN

Lch Vref

Rch Vref

Rch IN

GNDA

NFR2(–)

NFR1(+)

TEST

OUTL(+)

OUTL(–)

GNDD

OUTR(–)

OUTR(+)

VDDR

VDDX

XI

XO

GNDX

MCK

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VDA

NFL1(+)

NFL2(–)

RESET

Lch IN

Lch Vref

Rch Vre

f

Rch IN

GNDA

NFR2(–)

NFR1(+)

TEST

VDDL

OUTL(+)

OUTL(–)

GNDD

OUTR(–)

OUTR(+)

VDDR

VDDX

XI

XO

GNDX

MCK

Comparator

Comparator

Amplitude Doubling

Converter

Amplitude Doubling

Converter

Oscillator

Lch 7th order

Modulation Circuit

Rch 7th order

Modulation Circuit

Figure 111 BLOCK DIAGRAM OF IC

SD-AT100H

– 112 –

FL DISPLAY

PIN CONNECTION

PIN NO.

CONNECTION

8

4

4

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

31

P

30

P

29

P

28

P

27

P

26

P

25

P

24

P

20

P

23

P

22

P

21

P

19

P

18

P

17

P

16

P

15

P

14

P

10

P

13

P

12

P

11

P

9

P

8

P

7

P

6

P

5

P

4

P

3

P

2

P

1

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

8

3

3

8

2

2

8

1

1

8

0

0

7

9

9

7

8

8

7

7

7

7

6

6

7

5

5

7

4

4

7

3

3

7

2

2

7

1

1

7

0

0

6

9

9

6

8

8

6

7

7

6

6

6

6

5

5

6

4

4

6

3

3

6

2

2

6

1

1

6

0

0

5

9

9

5

8

8

5

7

7

5

6

6

5

5

5

5

4

4

5

3

3

4

9

9

4

8

8

4

7

7

4

6

6

4

5

5

4

4

4

4

3

3

5

2

2

5

1

1

5

0

0

PIN NO.

CONNECTION

1

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

32

P

33

P

34

P

35

P

36

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

1

G

2

G

6

G

3

G

4

G

5

G

7

G

8

G

9

G

10

G

11

G

12

G

13

G

14

G

15

G

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

2

3

4

5

6

7

8

9

1

0

0

1

1

1

1

2

2

1

3

3

1

4

4

1

5

5

1

6

6

1

7

7

1

8

8

1

9

9

2

0

0

2

1

1

2

2

2

2

3

3

2

4

4

2

5

5

2

6

6

2

7

7

2

8

8

2

9

9

3

0

0

3

1

1

3

2

2

3

6

6

3

7

7

3

8

8

3

9

9

4

0

0

4

1

1

4

2

2

3

3

3

3

4

4

3

5

5

(Note)

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

ANODE CONNECTION

P1

1 –1

2 –1

3 –1

4 –1

5 –1

1 –2

2 –2

3 –2

4 –2

5 –2

1 –3

1 –3

2 –3

3 –3

4 –3

5 –3

1 –4

1 –4

2 –4

3 –4

4 –4

5 –4

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

1G–8G, 12G,14G

9G

10G

S0

1–1

1–1

1–1

2–1

2–1

2–1

3–1

3–1

3–1

4–1

4–1

4–1

5–1

5–1

5–1

1–2

1–2

1–2

2–2

2–2

2–2

3–2

3–2

3–2

4–2

4–2

4–2

5–2

5–2

5–2

1–3

1–3

1–3

2–3

2–3

2–3

3–3

3–3

3–3

4–3

4–3

4–3

5–3

5–3

5–3

1–4

1–4

1–4

2–4

2–4

2–4

3–4

3–4

3–4

4–4

4–4

4–4

5–4

5–4

5–4

S2

S3

S4

S5

S6

S1

11G

13G

16G

DISC

L

C

C

R

LFE

SW

LS

RS

S

RDS

RT

TP

TA

PTYI

EON

PTY

TI

ST

STEREO

TRACK

TOTAL

CHAPTER

ANGLE

A

TITLE

RANDOM

PROGRAM

P21

1 –5

2 –5

3 –5

4 –5

5 –5

1 –6

2 –6

3 –6

4 –6

5 –6

1 –7

1 –7

2 –7

3 –7

4 –7

5 –7

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

1G–8G, 12G,14G

9G

10G

1–5

1–5

1–5

2–5

2–5

2–5

3–5

3–5

3–5

4–5

4–5

4–5

5–5

5–5

5–5

1–6

1–6

1–6

2–6

2–6

2–6

3–6

3–6

3–6

4–6

4–6

4–6

5–6

5–6

5–6

1–7

1–7

1–7

2–7

2–7

2–7

3–7

3–7

3–7

4–7

4–7

4–7

5–7

5–7

5–7

11G

13G

16G

B

SLEEP

PBC

KHz

MHz

ms

dB

dB

SLEEP

DISC

RDS

RDS

TRACK TITLE TOTAL CHAPTER ANGLE

A

kHz

MHz

ms

db

ST

B

RT TP TA PTYI EON PTY TI

STEREO

PROGRSM RANDOM

PBC

L

S

LS

RS

C

R

LFE

SW

15G

1G

2G

3G

4G

S2

S1

S0

S4

S5

( 1G-8G, 11G-15G )

S6

S3

5G

6G

7G

9G

8G

14G

10G

11G

12G

13G

1-1

2-1

3-1

4-1

5-1

1-2

2-2

3-2

4-2

5-2

1-3

2-3

3-3

4-3

5-3

1-4

2-4

3-4

4-4

5-4

1-5

2-5

3-5

4-5

5-5

1-6

2-6

3-6

4-6

5-6

1-7

2-7

3-7

4-7

5-7

FLE01 VVKHNA15LS+-1: FL Display

SD-AT100H

– 112 –

FL DISPLAY

PIN CONNECTION

PIN NO.

CONNECTION

8

4

4

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

31

P

30

P

29

P

28

P

27

P

26

P

25

P

24

P

20

P

23

P

22

P

21

P

19

P

18

P

17

P

16

P

15

P

14

P

10

P

13

P

12

P

11

P

9

P

8

P

7

P

6

P

5

P

4

P

3

P

2

P

1

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

8

3

3

8

2

2

8

1

1

8

0

0

7

9

9

7

8

8

7

7

7

7

6

6

7

5

5

7

4

4

7

3

3

7

2

2

7

1

1

7

0

0

6

9

9

6

8

8

6

7

7

6

6

6

6

5

5

6

4

4

6

3

3

6

2

2

6

1

1

6

0

0

5

9

9

5

8

8

5

7

7

5

6

6

5

5

5

5

4

4

5

3

3

4

9

9

4

8

8

4

7

7

4

6

6

4

5

5

4

4

4

4

3

3

5

2

2

5

1

1

5

0

0

PIN NO.

CONNECTION

1

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

32

P

33

P

34

P

35

P

36

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

1

G

2

G

6

G

3

G

4

G

5

G

7

G

8

G

9

G

10

G

11

G

12

G

13

G

14

G

15

G

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

2

3

4

5

6

7

8

9

1

0

0

1

1

1

1

2

2

1

3

3

1

4

4

1

5

5

1

6

6

1

7

7

1

8

8

1

9

9

2

0

0

2

1

1

2

2

2

2

3

3

2

4

4

2

5

5

2

6

6

2

7

7

2

8

8

2

9

9

3

0

0

3

1

1

3

2

2

3

6

6

3

7

7

3

8

8

3

9

9

4

0

0

4

1

1

4

2

2

3

3

3

3

4

4

3

5

5

(Note)

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

ANODE CONNECTION

P1

1 –1

2 –1

3 –1

4 –1

5 –1

1 –2

2 –2

3 –2

4 –2

5 –2

1 –3

1 –3

2 –3

3 –3

4 –3

5 –3

1 –4

1 –4

2 –4

3 –4

4 –4

5 –4

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

1G–8G, 12G,14G

9G

10G

S0

1–1

1–1

1–1

2–1

2–1

2–1

3–1

3–1

3–1

4–1

4–1

4–1

5–1

5–1

5–1

1–2

1–2

1–2

2–2

2–2

2–2

3–2

3–2

3–2

4–2

4–2

4–2

5–2

5–2

5–2

1–3

1–3

1–3

2–3

2–3

2–3

3–3

3–3

3–3

4–3

4–3

4–3

5–3

5–3

5–3

1–4

1–4

1–4

2–4

2–4

2–4

3–4

3–4

3–4

4–4

4–4

4–4

5–4

5–4

5–4

S2

S3

S4

S5

S6

S1

11G

13G

16G

DISC

L

C

C

R

LFE

SW

LS

RS

S

RDS

RT

TP

TA

PTYI

EON

PTY

TI

ST

STEREO

TRACK

TOTAL

CHAPTER

ANGLE

A

TITLE

RANDOM

PROGRAM

P21

1 –5

2 –5

3 –5

4 –5

5 –5

1 –6

2 –6

3 –6

4 –6

5 –6

1 –7

1 –7

2 –7

3 –7

4 –7

5 –7

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

1G–8G, 12G,14G

9G

10G

1–5

1–5

1–5

2–5

2–5

2–5

3–5

3–5

3–5

4–5

4–5

4–5

5–5

5–5

5–5

1–6

1–6

1–6

2–6

2–6

2–6

3–6

3–6

3–6

4–6

4–6

4–6

5–6

5–6

5–6

1–7

1–7

1–7

2–7

2–7

2–7

3–7

3–7

3–7

4–7

4–7

4–7

5–7

5–7

5–7

11G

13G

16G

B

SLEEP

PBC

KHz

MHz

ms

dB

dB

SLEEP

DISC

RDS

RDS

TRACK TITLE TOTAL CHAPTER ANGLE

A

kHz

MHz

ms

db

ST

B

RT TP TA PTYI EON PTY TI

STEREO

PROGRSM RANDOM

PBC

L

S

LS

RS

C

R

LFE

SW

15G

1G

2G

3G

4G

S2

S1

S0

S4

S5

( 1G-8G, 11G-15G )

S6

S3

5G

6G

7G

9G

8G

14G

10G

11G

12G

13G

1-1

2-1

3-1

4-1

5-1

1-2

2-2

3-2

4-2

5-2

1-3

2-3

3-3

4-3

5-3

1-4

2-4

3-4

4-4

5-4

1-5

2-5

3-5

4-5

5-5

1-6

2-6

3-6

4-6

5-6

1-7

2-7

3-7

4-7

5-7

FLE01 VVKHNA15LS+-1: FL Display

SD-AT100H

– 112 –

FL DISPLAY

PIN CONNECTION

PIN NO.

CONNECTION

8

4

4

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

31

P

30

P

29

P

28

P

27

P

26

P

25

P

24

P

20

P

23

P

22

P

21

P

19

P

18

P

17

P

16

P

15

P

14

P

10

P

13

P

12

P

11

P

9

P

8

P

7

P

6

P

5

P

4

P

3

P

2

P

1

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

8

3

3

8

2

2

8

1

1

8

0

0

7

9

9

7

8

8

7

7

7

7

6

6

7

5

5

7

4

4

7

3

3

7

2

2

7

1

1

7

0

0

6

9

9

6

8

8

6

7

7

6

6

6

6

5

5

6

4

4

6

3

3

6

2

2

6

1

1

6

0

0

5

9

9

5

8

8

5

7

7

5

6

6

5

5

5

5

4

4

5

3

3

4

9

9

4

8

8

4

7

7

4

6

6

4

5

5

4

4

4

4

3

3

5

2

2

5

1

1

5

0

0

PIN NO.

CONNECTION

1

F

+

+

N

P

P

N

P

P

N

P

P

I

C

P

32

P

33

P

34

P

35

P

36

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

N

P

P

1

G

2

G

6

G

3

G

4

G

5

G

7

G

8

G

9

G

10

G

11

G

12

G

13

G

14

G

15

G

N

P

P

N

P

P

N

P

P

F

–

–

F

–

–

F

+

+

2

3

4

5

6

7

8

9

1

0

0

1

1

1

1

2

2

1

3

3

1

4

4

1

5

5

1

6

6

1

7

7

1

8

8

1

9

9

2

0

0

2

1

1

2

2

2

2

3

3

2

4

4

2

5

5

2

6

6

2

7

7

2

8

8

2

9

9

3

0

0

3

1

1

3

2

2

3

6

6

3

7

7

3

8

8

3

9

9

4

0

0

4

1

1

4

2

2

3

3

3

3

4

4

3

5

5

(Note)

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

1) F+, –: Filament pin

2) nG: Grid pin

3) Pn: Anode pin

4) NP: No pin

5) IC: Pines are internally connection, and should be electrically open on the PCB

ANODE CONNECTION

P1

1 –1

2 –1

3 –1

4 –1

5 –1

1 –2

2 –2

3 –2

4 –2

5 –2

1 –3

1 –3

2 –3

3 –3

4 –3

5 –3

1 –4

1 –4

2 –4

3 –4

4 –4

5 –4

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

1G–8G, 12G,14G

9G

10G

S0

1–1

1–1

1–1

2–1

2–1

2–1

3–1

3–1

3–1

4–1

4–1

4–1

5–1

5–1

5–1

1–2

1–2

1–2

2–2

2–2

2–2

3–2

3–2

3–2

4–2

4–2

4–2

5–2

5–2

5–2

1–3

1–3

1–3

2–3

2–3

2–3

3–3

3–3

3–3

4–3

4–3

4–3

5–3

5–3

5–3

1–4

1–4

1–4

2–4

2–4

2–4

3–4

3–4

3–4

4–4

4–4

4–4

5–4

5–4

5–4

S2

S3

S4

S5

S6

S1

11G

13G

16G

DISC

L

C

C

R

LFE

SW

LS

RS

S

RDS

RT

TP

TA

PTYI

EON

PTY

TI

ST

STEREO

TRACK

TOTAL

CHAPTER

ANGLE

A

TITLE

RANDOM

PROGRAM

P21

1 –5

2 –5

3 –5

4 –5

5 –5

1 –6

2 –6

3 –6

4 –6

5 –6

1 –7

1 –7

2 –7

3 –7

4 –7

5 –7

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

P36

1G–8G, 12G,14G

9G

10G

1–5

1–5

1–5

2–5

2–5

2–5

3–5

3–5

3–5

4–5

4–5

4–5

5–5

5–5

5–5

1–6

1–6

1–6

2–6

2–6

2–6

3–6

3–6

3–6

4–6

4–6

4–6

5–6

5–6

5–6

1–7

1–7

1–7

2–7

2–7

2–7

3–7

3–7

3–7

4–7

4–7

4–7

5–7

5–7

5–7

11G

13G

16G

B

SLEEP

PBC

KHz

MHz

ms

dB

dB

SLEEP

DISC

RDS

RDS

TRACK TITLE TOTAL CHAPTER ANGLE

A

kHz

MHz

ms

db

ST

B

RT TP TA PTYI EON PTY TI

STEREO

PROGRSM RANDOM

PBC

L

S

LS

RS

C

R

LFE

SW

15G

1G

2G

3G

4G

S2

S1

S0

S4

S5

( 1G-8G, 11G-15G )

S6

S3

5G

6G

7G

9G

8G

14G

10G

11G

12G

13G

1-1

2-1

3-1

4-1

5-1

1-2

2-2

3-2

4-2

5-2

1-3

2-3

3-3

4-3

5-3

1-4

2-4

3-4

4-4

5-4

1-5

2-5

3-5

4-5

5-5

1-6

2-6

3-6

4-6

5-6

1-7

2-7

3-7

4-7

5-7

FLE01 VVKHNA15LS+-1: FL Display