Panasonic KX-TVM200BX / KX-TVM204X / KX-TVM296X Service Manual ▷ View online

121

KX-TVM200BX

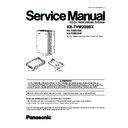

18.3.2. DSP and DPT Block Diagram

McBSP0 sends and receives voice PCM data to and from the PBX interface. The PBX interface has three types of interfaces.

For this reason, each interface has a different device to and from which PCM voice data are sent and received. In any case,

the DSP´s McBSP0 is a clock slave while the clock master varies from interface to interface. In the case of 1 and 3, the clock

master is the ASIC. In the case of 2, the clock master is the DPT I/F. The base clock is a 2-MHz PCM serial communication

signal, and voice data of up to 24 channels are sent and received. As for the placements of clock master and clock slave, see

the references at the end of the chapter.

McBSP1 sends and receives the data compressed between the ASIC and the DSP and the data decompressed by the DSP.

The DSP is a clock slave, and the clock master is the ASIC. McBSP1 forms the serial communication that sends and receives

16-bit command data and 16-bit data on the base clock 8 MHz respectively with 24 channels x 2 (mainframe + subframe) = 48

frames.

The HPI-8 is accessed by the CPU and it writes the command setting program data into the DSP.

The CPU has a mechanism at startup to download application programs to each DSP´s internal RAM with the HPI-8. With this

configuration, application programs can be uploaded as necessary after installation.

The DSP unit installed in this system has four channels per unit, and two DSPs are installed.

For this reason, each interface has a different device to and from which PCM voice data are sent and received. In any case,

the DSP´s McBSP0 is a clock slave while the clock master varies from interface to interface. In the case of 1 and 3, the clock

master is the ASIC. In the case of 2, the clock master is the DPT I/F. The base clock is a 2-MHz PCM serial communication

signal, and voice data of up to 24 channels are sent and received. As for the placements of clock master and clock slave, see

the references at the end of the chapter.

McBSP1 sends and receives the data compressed between the ASIC and the DSP and the data decompressed by the DSP.

The DSP is a clock slave, and the clock master is the ASIC. McBSP1 forms the serial communication that sends and receives

16-bit command data and 16-bit data on the base clock 8 MHz respectively with 24 channels x 2 (mainframe + subframe) = 48

frames.

The HPI-8 is accessed by the CPU and it writes the command setting program data into the DSP.

The CPU has a mechanism at startup to download application programs to each DSP´s internal RAM with the HPI-8. With this

configuration, application programs can be uploaded as necessary after installation.

The DSP unit installed in this system has four channels per unit, and two DSPs are installed.

122

KX-TVM200BX

•

•

•

• McBSP0

McBSP0 is used at the serial communication port for sending/receiving voice data between the CODEC and the DSP, and

between the PBX interface and the DSP.

between the PBX interface and the DSP.

As for the data to be handled, only 2-channel 8-bit MSB First voice data are sent and received. The frame pulse remains active

during valid data are asserted according to the specifications of the PBX interface ASIC. There is no data delay in frame pulses

and data sent and received.

during valid data are asserted according to the specifications of the PBX interface ASIC. There is no data delay in frame pulses

and data sent and received.

123

KX-TVM200BX

•

•

•

• McBSP1

McBSP1 is connected with the serial management controller interface of VM-dedicated ASIC.

This interface sends and receives the voice data and control commands of each channel with up to 12 DSPs (24 channels) at

the maximum. The serial communication format to be connected is shown below. The DSP operates as a clock slave even at

McBSP1, and the clock master is the ASIC dedicated to VM. The base clock´s CLKR/X is set at 8.192 MHz, and the frame sync-

pulse at 2 KHz. As for the frame pulse, only one cycle of clock becomes active. The DSP is set to allow data to lag one bit

behind the assertion of frame pulse. Each channel´s command data 16 bits and voice data 16 bits are arranged as mainframe

and subframe, and 48 frames of 24 channels are timeshared and arranged on this serial communication format.

Each DSP sends and receives commands and data of two channels of serial communication signals. As DFH 1-12 signals that

show the dedicated data frame heads are input into each DSP, each DSP sends and receives data to and from these DFH

signals through 4-word frame, single-phase frame and 32-bit words (which can be changed, depending on temporary DSP

specifications). With DFH input, each DSP handles 24 x 2 x (16 +16) = 1536 bits as valid data. As for the frame format of

command frames, see ASIC module specifications. The frame format of data frames is composed of 16-bit MSB First. The

clock between McBSP0 and McBSP1 is not synchronized.

This interface sends and receives the voice data and control commands of each channel with up to 12 DSPs (24 channels) at

the maximum. The serial communication format to be connected is shown below. The DSP operates as a clock slave even at

McBSP1, and the clock master is the ASIC dedicated to VM. The base clock´s CLKR/X is set at 8.192 MHz, and the frame sync-

pulse at 2 KHz. As for the frame pulse, only one cycle of clock becomes active. The DSP is set to allow data to lag one bit

behind the assertion of frame pulse. Each channel´s command data 16 bits and voice data 16 bits are arranged as mainframe

and subframe, and 48 frames of 24 channels are timeshared and arranged on this serial communication format.

Each DSP sends and receives commands and data of two channels of serial communication signals. As DFH 1-12 signals that

show the dedicated data frame heads are input into each DSP, each DSP sends and receives data to and from these DFH

signals through 4-word frame, single-phase frame and 32-bit words (which can be changed, depending on temporary DSP

specifications). With DFH input, each DSP handles 24 x 2 x (16 +16) = 1536 bits as valid data. As for the frame format of

command frames, see ASIC module specifications. The frame format of data frames is composed of 16-bit MSB First. The

clock between McBSP0 and McBSP1 is not synchronized.

124

KX-TVM200BX

Click on the first or last page to see other KX-TVM200BX / KX-TVM204X / KX-TVM296X service manuals if exist.