Panasonic KX-TDA0490XJ / KX-TDA0490X Service Manual ▷ View online

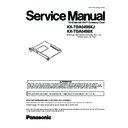

7 BLOCK DIAGRAM

VoIP BUSY LED

SH4(7750R)

IC400

IC

40

3,

40

5

RJ45

CN201

DPRAM

(1KB)

IC300

DSP

M82510

Midspeed

IC100

ON LINE LED

Serial

DC/DC

CONVERTER

IC800

+15V

3.3V

1.5V

BB_IF

CN200

LPR(SH1)

IC100

FLASH

1MB

IC102

SRAM

512KB

IC103

16

16

8

8

8

nINT

nINT

Lside

Rside

L_nRST

16

16

16

32

SCI_CN

32

BSC

FPGA

IC301

8

PCM Highway

SCI

SDRAM

64MB

IC501,502

FLASH

8MB

IC500

PBX IF

CT Bus

90 Pin

LPR

LED

Green/Red

CARD SATUS LED

HUDI

Xtal

16M

X400

16

VoIP_nRST

CLKIO(66MHz)

BUS TRANS

16

DSP I/F (sub board)

16

CN

PHY

BCM5221

IC202

rMII

Exp_Bus

SDRAM

16MB

IC107

TDM

OSC

10M

X201

EC Bus

2.5V

PWR_nRST

DC/DC CONVERTER

IC105

3.3V

1.2V

CN1

00

OSC

50M

X200

OSC 12M

X100

OSC 16M

X200

RST IC

IC201

REGULATER

IC801

PLD

IC201

PCC-ASIC

IC202

ALARM LED

DATA LED

LINK LED

IP Engine

ASIC

Power Supply

OPT_nRST

KX-TDA0490XJ/KX-TDA0490X BLOCK DIAGRAM

KX

-T

-T

DA0

490X

J

/

KX

-T

-T

DA0

490X

17

8 CIRCUIT OPERATIONS

8.1. BRIEF DESCRIPTION OF BLOCKS

Block Name

Functional Outline

Power Supply

P.S.

DC/DC Power Supply; Supply 3.3V, 1.5V, 2.5V from 15V power supply.

Power Supply +1.2V and +3.3V.

Power Supply +1.2V and +3.3V.

ASIC Block

RST-IC

Reset IC; Generate a reset of the PCC ASIC.

PCC-ASIC

ASIC by PCC, which controls interface between the cards of TDA100/200.

•

•

•

• Local bus controller

•

•

•

• TSW between a basic channel of the system and a local channel in the card

Operating Frequency: 16.384MHz

OSC16M

Crystal oscillator for PCC-ASIC (16.384MHz)

CARD STATUS LED

Display the status of the IP-GW16 card by LED.

Displayed in red/green.

Displayed in red/green.

LPR Block

LPR

LPR control the process, which receive a message from the side of backboard and

convert it to a message to the IP-Engine.

convert it to a message to the IP-Engine.

OSC12M

Oscillator for LPR (12.288MHz)

FLASH

Store the above CPU program.

1024Kbyte (512K x 16bit)

1024Kbyte (512K x 16bit)

SRAM

Used as the operational data area of the CPU.

512Kbyte (256K x 16bit)

512Kbyte (256K x 16bit)

PBX-IF

DPRAM

Two-way memory for communication between the CPU of the IP-Engine and the LPR.

FPGA

Conversion logic to transfer the voice data from the PCC-ASIC to the CPU of the IP-

Engine.

Engine.

IP-Engine

SH4

Control the protocol including H.323 V2 and HTTP.

XTAL16M

Crystal oscillator for SH4 (16.384MHz is planned.)

ENGINE STS

LED group indicating the status of the engine block

(ONLINE, ALARM, VoIP BUSY)

(ONLINE, ALARM, VoIP BUSY)

SDRAM

Memory for storing program and data

64Mbyte (16M x 16bit x 2)

64Mbyte (16M x 16bit x 2)

BUSDRV

Buffer to divide the SH4 bus into the high speed bus and the low speed bus.

FLASH

Memory for storing program and data

The FLASH of the dual operation type is used.

8Mbyte (4M x 16bit)

The FLASH of the dual operation type is used.

8Mbyte (4M x 16bit)

DSP I/F

DSP CON

Connector to mount DSP Sub Board.Mount the LAN Interface Part including DSP on this

board.

board.

DSP

Realization of 16-Channel and VoIP function

Supported Voice Codec Standarda: G.711, G.729A. G.723.1

Echo Cancellation

RTP/RTCP

Fax Tones Detection and Generation

DTMF Detection and Generation

Supported Voice Codec Standarda: G.711, G.729A. G.723.1

Echo Cancellation

RTP/RTCP

Fax Tones Detection and Generation

DTMF Detection and Generation

OSC10M

System Clock of DSP (10MHz)

PHY

10BASE-T/100BASE-TX IEEE 802.3u fast Ethernet transceiver.

Mll and RMII configurable.

Controls the LED of LINK and DATA.

Mll and RMII configurable.

Controls the LED of LINK and DATA.

OSC50M

Quartz crystal oscillator for DSP and PHY(50MHz)

8.2. IP-Engine

Configuration :

CPU (IC400), SDRAM (IC501, IC502), Flash ROM (IC500), Source clock 16.384MHz (X400), Spread spectrum clock generator

(IC406), etc.

(IC406), etc.

Function :

CPU (IC400)

•

•

•

•

• This generates a select signal, and reads/stores data among peripherals.

•

•

•

• This controls middle ware of G.711, G.723.1, G.729A and protocol of H.323, HTTP.

•

•

•

• Communication with the Main Board of PBX.

Spread spectrum clock generator (IC406)

•

•

•

•

• This generates the clock that has constant fluctuations with a central focus on X400 clock output (16.384MHz), in order to

reduce unnecessary radiation.

18

KX-TDA0490XJ / KX-TDA0490X

8.3. ASIC BLOCK

Configuration :

ASIC (IC202), Reset IC (IC201), Source clock 16.384MHz (X200), etc.

Function :

ASIC (IC202)

Being connected with the backboard by 90pin connector (CN200), this provides the EC bus interface function and H.100

communication function.

(1) EC bus interface (Dual port RAM (DPRAM) communication) function

•

Being connected with the backboard by 90pin connector (CN200), this provides the EC bus interface function and H.100

communication function.

(1) EC bus interface (Dual port RAM (DPRAM) communication) function

•

•

•

• This is connected with the synchronized 16-bit bus that is called EC bus, for the communications with MAIN.

•

•

•

• All EC-bus signals from mainboard are terminated at ASIC (IC202).

•

•

•

• Between this card and MAIN (EC bus), data is transmitted and received through the dual port RAM.

•

•

•

• The schematic diagram is as follows.

Fig. DPRAM Communication schematic diagram

(2) H.100 interface function

•

•

•

•

• CT-BUS function included in ASIC (IC202), being connected with the mainboard, conducts voice and data communications

in serial. This board does not output clock.

Type of Reset

Description

PWR_RST

Power-on Reset

Reset function to be released in 50msec after turning on the power supply (3.3V) to the card by the power-on or

the on-line addition.

This reset is connected to the ASIC for a circuit control and the FLASH memory.

(To start up the FLASH before the LPR reset is released.)

Reset function to be released in 50msec after turning on the power supply (3.3V) to the card by the power-on or

the on-line addition.

This reset is connected to the ASIC for a circuit control and the FLASH memory.

(To start up the FLASH before the LPR reset is released.)

EC_nRST

System Reset of the PBX

Controlled directly by the CPU with MPR, and activated by supplying power to the system, self-resetting the CPU

or pressing the Reset SW on the MPR.

Controlled directly by the CPU with MPR, and activated by supplying power to the system, self-resetting the CPU

or pressing the Reset SW on the MPR.

L_nRST

Local Reset in the Card

Reset function to the device in the card, outputted from a port of the line ASIC.

After the reset of the line ASIC (the PWR_RST, EC_nRST above) is released, hold the Reset Hold status and

can release by a direction from the MPR.

Reset function to the device in the card, outputted from a port of the line ASIC.

After the reset of the line ASIC (the PWR_RST, EC_nRST above) is released, hold the Reset Hold status and

can release by a direction from the MPR.

EC Bus

Card Individual Command Reset

The access to the line ASIC by the EC bus access from the MPR can perform the Self Reset in the ASIC.

The ASIC reset returns the L_nRST to its initial state and makes it active.

After the command is issued, a reset in the ASIC is released in 16clk (2µsec) at the EC_CLK.

The access to the line ASIC by the EC bus access from the MPR can perform the Self Reset in the ASIC.

The ASIC reset returns the L_nRST to its initial state and makes it active.

After the command is issued, a reset in the ASIC is released in 16clk (2µsec) at the EC_CLK.

VoIP_nRST

IPGW Engine Reset

Reset signal to the IPGW engine block controlled from the PCC-LPR.

Outputted from a port of the line ASIC, held at the reset hold state after the start-up of the card and released from

the LPR after the start-up of the LPR.

Reset signal to the IPGW engine block controlled from the PCC-LPR.

Outputted from a port of the line ASIC, held at the reset hold state after the start-up of the card and released from

the LPR after the start-up of the LPR.

SUB_nRST

Sub Board Reset

Outputted from PORT19, I/O Port of SH4.After resetting a power-on, since it is in a reset input status in the initial

state, it is controlled from SH4 to cancel the reset of the Sub Board.(Reset Input Time: 2ms or more)

Outputted from PORT19, I/O Port of SH4.After resetting a power-on, since it is in a reset input status in the initial

state, it is controlled from SH4 to cancel the reset of the Sub Board.(Reset Input Time: 2ms or more)

19

KX-TDA0490XJ / KX-TDA0490X

8.4. PBX INTERFACE BLOCK

Configuration :

DPRAM (IC300) etc.

Function :

DPRAM (IC300)

Be-directional memory for communication between CPU (SH4) and mainboard of PBX.

Be-directional memory for communication between CPU (SH4) and mainboard of PBX.

8.5. DSP BLOCK (SUB BOARD)

Configuration :

DSP (IC100), SDRAM (IC107), PHY (IC202), PLD (IC201), DSP system clock 10MHz (X201), Ethernet clock 50MHz (X200),

RJ45 integrated magnetics connector (CN201).

RJ45 integrated magnetics connector (CN201).

Function :

DSP (IC100)_sub board)

•

•

•

•

• Power Supply : +1.2V and +3.3V.

•

•

•

• Package : 484-ball PFBGA.

•

•

•

• Operating Clock : 10MHz.

•

•

•

• Supported Voice Codec Standards : G.711, G.729A, G.723.1.

•

•

•

• Echo Cancellation.

•

•

•

• RTP/RTCP.

•

•

•

• Fax Tones Detection and Generation.

•

•

•

• DTMF Detection and Generation.

SDRAM (IC107_sub board)

•

•

•

•

• Execution Area of DSP Firmware.

PHY (IC202_sub board)

•

•

•

•

• Power Supply : +2.5V or +3.3V.

•

•

•

• Package : 64-pin TQFP.

•

•

•

• 10BASE-T/100BASE-TX IEEE 802.3u fast Ethernet transceiver.

•

•

•

• Mll and RMII configurable.

•

•

•

• Controls the LED of LINK and DATA.

PLD (IC201)

•

•

•

•

• Switching Control between 10BASE and 100BASE.

20

KX-TDA0490XJ / KX-TDA0490X

Click on the first or last page to see other KX-TDA0490XJ / KX-TDA0490X service manuals if exist.