Panasonic KX-NCP1180X Service Manual ▷ View online

5

KX-NCP1180X

3 Specifications

Functional Block

Functional contents

Analog External Line Interface

Number of Ports

4 ports

Main Function

Dial pulse signal transmission function

DTMF signal transmission function

Polarity reversal detecting function

Bell detection function

End-call signal detection function

2W/4W Conversion function

Surge Protection function

4ch CODEC by STMENS function

DTMF signal transmission function

Polarity reversal detecting function

Bell detection function

End-call signal detection function

2W/4W Conversion function

Surge Protection function

4ch CODEC by STMENS function

• CODEC Function

• Power down function

• µ/A law switching function

• Test function (Loop back, tone generation)

• Programmable digital filter function

• Serial interface function

• PIO function

• CO Caller ID function (FSK/DTMF)

• Power down function

• µ/A law switching function

• Test function (Loop back, tone generation)

• Programmable digital filter function

• Serial interface function

• PIO function

• CO Caller ID function (FSK/DTMF)

DTMF Generator

Available to transmit an optional tone every 4 line port

On-board DC/DC Power

Input +15V

Output +15V, +5V, +3.3V

Output +15V, +5V, +3.3V

Power Failure Transfer

Supports 1 line

ASIC (IC3)

EC bus interface function

H.100 bus Interface function

Digital PLL function Local bus interface function

Time switch function, Gain Control function

Intelligent PIO function, JTAG

H.100 bus Interface function

Digital PLL function Local bus interface function

Time switch function, Gain Control function

Intelligent PIO function, JTAG

LED Display Circuit

Card state Display LED: 2 colors (Red/Green)

External Interface Connector

Extension interface

RJ45: 4 port

Power Failure Transfer

RJ45: 1 port

6

KX-NCP1180X

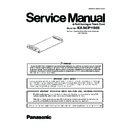

4 Technical Descriptions

4.1.

Block Diagram

KX-NCP1180X BLOCK DIAGRAM

BACK BOARD

nR

E

S

L_n

R

S

T

nW

R

nR

D

LA

[12:

0]

L

D

[7

:0

]

M

O

D

E

[5

:0

]

P1

[7

:0

]

n

R

ESET

P

LLC

LK

DI

N

DO

UT

DCL

K

C_

CS

[0

]

FH

HW

C

L

K

[0

]

LD

H

W

[0

]

LU

H

W

[0

]

E

C

_C

LK

EC

_

P

A

R

E

C

_

T

RDY

EC

_

S

T

O

P

EC

_

PER

R

EC

_

IN

T

EC

_

N

R

S

T

C

T

_C

8_A

C

T

_

D

[7

:0

]

ASI

C

(C

ID

nW

R

nR

D

nR

E

S

R

ESET IC

IC

6

XT

A

L

16.

38

4

MH

z

C_

CS

[0

]

DH

W

[0

]

ASI

C

(e

SAM

SO

N)

UH

W

[0

]

CL

K

FH

CS

CO

DE

C

PEB

2466

EC

_

D

ET

C

T

_

C

B_

A

n

C

S[0]

XT

AL

4.096MH

z

DR

IV

E

R

DR

IV

E

R

P2

2

P2

3

+3

.3

V

P2

0

MO

D

E

4

J

U

M

PER

8

n

C

P

CDE

T

[0

]

S

HUNT

[0

]

OP

A

M

P

R

e

v&Be

ll

&

S

hunt

Detec

tor

Por

t#

1

T

rans

for

m

e

r

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

n

BEL

D

E

T

[0

]

n

L

OOP

[0

]

Se

rg

e

EM

C

n

R

E

V

D

E

T

][0

]

OP

A

M

P

R

e

v&Be

ll

&

S

hunt

Detec

tor

Por

t#

2

T

rans

for

m

e

r

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

n

BEL

D

E

T

[1]

n

L

O

O

P[1]

Se

rg

e

EM

C

n

R

E

V

D

ET[1]

OP

A

M

P

R

e

v&Be

ll

&

S

hunt

Detec

tor

Por

t#

3

T

rans

for

m

e

r

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

n

BEL

D

E

T

[2]

n

L

O

O

P[2]

Se

rg

e

EM

C

n

R

E

V

D

ET[2]

OP

A

M

P

R

e

v&Be

ll

&

S

hunt

Detec

tor

Por

t#

4

T

rans

for

m

e

r

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

n

BEL

D

E

T

[3]

n

L

O

O

P[3]

Se

rg

e

EM

C

n

R

E

V

D

ET[3]

n

C

PC

D

E

T

[1]

S

HUNT

[1

]

n

C

PC

D

E

T

[2]

S

HUNT

[2

]

S

HUNT

[3

]

nC

S

[0

]

+2

.5

V

+5

V

+3

.3

V

+

15V

DC

/D

C

DC

/D

C

+2

.5

V

DC

/D

C

L_n

R

S

T

nW

R

nR

D

LA

[12:

0]

L

D

[7

:0

]

M

O

D

E

[5

:0

]

P1

[7

:0

]

n

R

ESET

P

LLC

LK

DI

N

DO

UT

DCL

K

C_

CS

[0

]

FH

HW

C

L

K

[0

]

LD

H

W

[0

]

LU

H

W

[0

]

E

C

_C

LK

E

C

_A

D

[15:

0

]

EC

_

P

A

R

EC

_

F

R

A

M

E

E

C

_

T

RDY

EC

_

S

T

O

P

EC

_

BE[

1

:0

]

EC

_

PER

R

EC

_

IN

T

EC

_

ID

SEL

EC

_

N

R

S

T

CT

_

N

E

T

RE

F

CT

_

F

RA

M

E

_

A

C

T

_C

8_A

C

T

_

D

[7

:0

]

A

[5:0]

D

[7:

0]

ASI

C

(C

ID

)

J

U

M

PER

J

U

M

PER

ASI

C

(e

SAM

SO

N)

DO

UT

DX

A

DX

B

PC

L

K

MC

L

K

DI

N

DCL

K

CS

DRA

DRB

CO

DE

C

PEB

2466

FS

C

R

ESET

EC

_

D

ET

C

T

_

C

B_

A

NC

S

0

NW

R

NR

S

T

NR

D

DR

IV

E

R

DR

IV

E

R

P2

2

P2

3

P2

0

P

O

[7

:0

]

OP

A

M

P

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

Se

rg

e

EM

C

OP

A

M

P

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

Se

rg

e

EM

C

OP

A

M

P

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

Se

rg

e

EM

C

OP

A

M

P

DI

A

L

&

D

C

Loop &

CP

C

Detec

tor

Se

rg

e

EM

C

n

C

PC

D

E

T

[3]

nC

S

[0

]

+2

.5

V

DC

/D

C

DC

/D

C

DC

/D

C

DC

/D

C

DC

/D

C

DC

/D

C

IC5

IC5

IC203

7

KX-NCP1180X

4.2.

Circuit Operation

4.2.1.

Description of Control System Circuits

4.2.1.1.

Reset

On startup, releasing the ASIC reset is executed by EC_nRST through MPR.

After releasing the ASIC, the local reset signal should be sent to CODEC by releasing the soft rest from MPR, and CODEC fac-

tor should be downloaded from MPR.

After releasing the ASIC, the local reset signal should be sent to CODEC by releasing the soft rest from MPR, and CODEC fac-

tor should be downloaded from MPR.

• LED operational state display LED (2 colors)

Red ON: Fault (includes RESET)

Green ON: INS (line free)

Green flash (60/sec): INS (line busy)

Red flash (60/sec): OUS

OFF: the power section failure

Green ON: INS (line free)

Green flash (60/sec): INS (line busy)

Red flash (60/sec): OUS

OFF: the power section failure

4.2.1.2.

Local Highway Interface

Packs 2.048, 4.096, 8.192 MHz highway (Max.64 timeslot). (voice communication bus in the circuit board)

The PCM data of arbitrary streams 0-15 (128 timeslot / 1 stream) on the CT bus can switch to the arbitrary local highway (64

timeslot) by the local TSW.

The timeslot configuration example of the local highway is shown below.

The PCM data of arbitrary streams 0-15 (128 timeslot / 1 stream) on the CT bus can switch to the arbitrary local highway (64

timeslot) by the local TSW.

The timeslot configuration example of the local highway is shown below.

8

KX-NCP1180X

4.2.1.3.

ASIC...IC5

• EC bus Interface

16bit/8MHz two-way address data multiplex self-bus (communication bus with MPR).

• CT bus Interface

Supports eight of 8.192MHz highway (128 timeslot) (voice communication bus with MPR).

• Local TSW

Timeslot switching between CT bus (1024ch) and local highway (64ch).

(Timeslot switching between the voice communication bus in MPR and that in the circuit board).

(Timeslot switching between the voice communication bus in MPR and that in the circuit board).

• Local Gain Control

Gain control of the local highway up-down 64ch by 1dB/step randomly.

• GPIO Interface

A parallel interface that can be set in random interactively.

Refer to IC5 (ASIC) (P.38).

Refer to IC5 (ASIC) (P.38).

Click on the first or last page to see other KX-NCP1180X service manuals if exist.