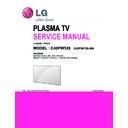

LG C42PW120-WA (CHASSIS:PC21A) Service Manual ▷ View online

THERMAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

C408

0.1uF

0.1uF

PC_SER_CLK

PC_SER_DATA

T1OUT

+5V_ST

T1OUT

+3.3V_ST

R1IN

IC401

MAX3232CDR

3

C1-

2

V+

4

C2+

1

C1+

6

V-

5

C2-

7

DOUT2

8

RIN2

9

ROUT2

10

DIN2

11

DIN1

12

ROUT1

13

RIN1

14

DOUT1

15

GND

16

VCC

R448

10

READY

10

READY

+5V_ST

C410

0.1uF

C411

22uF

22uF

16V

R447

10

READY

10

READY

R1IN

T2OUT

R2IN

S7_TXD

T2OUT

IR

+3.3V_ST

S7_RXD

Q402

READY

E

B

C

R2IN

C407

0.1uF

+5V_ST

IR

R437

4.7K

R438

4.7K

READY

4.7K

READY

R441

4.7K

D406

30V

BAT54_SUZHO

D407

30V

BAT54_SUZHO

D408

READY

D410

30V

BAT54_SUZHO

R401

33

33

DSUB_B+

RGB_DDC_SDA

RGB_DDC_SCL

R428

1K

R416

75

R415

75

75

DSUB_DET

+5V_ST

DSUB_HSYNC

R410

10

10

C400

10pF

50V

10pF

50V

DSUB_G+

DSUB_R+

R405

10K

R427

10K

R409

10K

R400

33

33

R411

10

10

PC_SER_DATA

C403

10pF

50V

10pF

50V

DSUB_VSYNC

GND

PC_SER_CLK

R417

75

USB1_DP_to_MAIN

R433

0

ET_NET

RP

R446

10K

R432

0

ET_NET

R431

0

ET_NET

+5V_ST

R451

10K

R434

0

ET_NET

USB_OCD

C413

10uF

10V

USB1_DM_to_MAIN

TN

+2.5V

IC402

AP2191SG-13

3

IN_2

2

IN_1

4

EN

1

GND

5

FLG

6

OUT_1

7

OUT_2

8

NC

C412

0.1uF

16V

TP

RN

R459

0

READY

R445

33

R455

0

+5V

AV_CVBS_IN

AV_L_IN

AV_R_IN

R418

12K

12K

R412

10K

R407

220K

220K

R419

12K

12K

R413

10K

10K

R408

220K

220K

R420

75

75

R406

2K

P_17V

C402

10uF

10uF

16V

+3.3V_ST

R404

2K

R402

2K

R414

6.8K

C404

27pF

27pF

50V

R422

15K

AV_AUDIO_MUTE

R423

5.6K

AV_Lout

C401

10uF

10uF

16V

MMBT3904(NXP)

Q400

AV_Rout

IC400

AZ4580MTR-E1

3

IN1+

2

IN1-

4

VEE

1

OUT1

5

IN2+

6

IN2-

7

OUT2

8

VCC

R403

2K

R430

5.6K

MMBT3904(NXP)

Q401

R426

10K

10K

R421

15K

15K

C405

27pF

50V

R429

6.8K

6.8K

R424

10K

R425

1K

AV_DET

IR

R469 0

PM_RXD

PM_TXD

+3.3V

+3.3V

+3.3V

+3.3V

L400

120

120

L401

READY

120

JK402

KJA-UB-0-0037

1

2

3

4

5

JK401

XRJV-01V-0-D12-080

ET_NET

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

JK403

PEJ027-04

6B

T_TERMINAL2

7B

B_TERMINAL2

5

T_SPRING

4

R_SPRING

7A

B_TERMINAL1

6A

T_TERMINAL1

3

E_SPRING

L402

R470

100K

+5V_ST

C414

47uF

25V

+5V_ST

R471

2.7K

+3.3V_ST

JK400

SPG09-DB-010

1

RED

2

GREEN

3

BLUE

4

GND_1

5

DDC_GND

6

RED_GND

7

GREEN_GND

8

BLUE_GND

9

NC

10

SYNC_GND

11

GND_2

12

DDC_DATA

13

H_SYNC

14

V_SYNC

15

DDC_CLOCK

16

SHILED

JK407

SPG09-DB-009

1

2

3

4

5

6

7

8

9

10

JK408

PPJ231-01

8

6

7

5

4

JK409

PPJ241-02

3

[WH]L_OUT

5

[WH]GND

4

[RD]R_OUT

6

FIX_TER

LAN_VDD35

LAN_1.2V

R475

4.7K

R491

4.7K

4.7K

R477

4.7K

TN

LAN_3.3V

IC405

AT93C66A-10SU-1.8

3

DI

2

SK

4

DO

1

CS

5

GND

6

ORG

7

NC

8

VCC

R493

33

PME_CLEAR

RP

LAN_USB_DP

LAN_VDD12PLL

LAN_1.2V

+3.3V_ST

EEDI

LAN_3.3V

LAN_3.3V

LAN_1.2V

PME_MODE_SEL

R486 33

EECLK

EECS

EEDI

EECS

EEDO

LAN_USB_DM

TP

PME

IC403

LAN7500

1

TDI

2

TCK

3

TMS

4

TDO

5

XI

6

XO

7

VDDVARIO_1

8

VDD12CORE_1

9

SW_MODE

10

GPIO7

11

VDD12CORE_2

12

USBDM

13

USBDP

14

VBUS_DET

15

VDD33A

16

USBRBIAS

17

VDD12USBPLL

18

GPIO8

19

VDDVARIO_2

20

VDD12CORE_3

21

GPIO9

22

GPIO10

23

VDD12CORE_4

24

VDDVARIO_3

25

GPIO11

26

EECLK

27

EEDI

28

EEDO

29

EECS

30

VDD12CORE_5

31

GPIO0/LED0

32

GPIO1/LED1

33

GPIO2/LED2

34

GPIO3/LED3

35

GPIO4/LED4

36

VDD12CORE_6

37

VDDVARIO_4

38

GPIO5/PME

39

TEST

40

GPIO6/PME_MODE_SEL

41

ETHRBIAS

42

NRESET/PME_CLEAR

43

TR0N

44

TR0P

45

VDD12A_1

46

TR1N

47

TR1P

48

VDD12A_2

49

VDD12BIAS

50

VDD12PLL

51

TR2N

52

TR2P

53

VDD12A_3

54

TR3N

55

TP3P

56

VDD12A_4

57

[EP]VSS

LAN_VDD12USBPLL

EEDO

VBUS_DET

RN

R494

33

R474

4.7K

X400

25MHz

LAN_3.3V

EECLK

LAN_3.3V

R476

4.7K

LAN_VDD12

C440

0.1uF

16V

0.1uF

16V

R492

33

R485

8.2K 1%

LAN_1.2V

L405

BLM18SG121TN1D

C427

0.1uF

16V

0.1uF

16V

+3.3V_ST_LAN

LAN_VDD35

C433

0.1uF

16V

0.1uF

16V

C435

0.1uF

16V

0.1uF

16V

C423

0.1uF

16V

0.1uF

16V

C437

0.1uF

16V

0.1uF

16V

LAN_VDD12USBPLL

Q407

AO3407A

G

D

S

C430

0.1uF

16V

0.1uF

16V

L409

BLM18SG121TN1D

LAN_VDD12

22uF

C420

10V

C432

0.1uF

16V

0.1uF

16V

C434

0.1uF

16V

0.1uF

16V

C439

0.1uF

16V

0.1uF

16V

+3.3V_ST_LAN

L404

BLM18SG121TN1D

LAN_3.3V

C424

0.1uF

16V

0.1uF

16V

IC404

AZ1117BH-1.2TRE1

GND/ADJ

OUT

IN

C419

2.2uF

16V

C428

0.1uF

16V

0.1uF

16V

L408

BLM18SG121TN1D

C422

0.1uF

16V

0.1uF

16V

LAN_1.2V

C421

1uF

25V

1uF

25V

+3.3V_ST

C438

0.1uF

16V

0.1uF

16V

C418

2.2uF

16V

LAN_1.2V

C429

0.1uF

16V

0.1uF

16V

LAN_VDD12PLL

R488

100K

100K

L407

BLM18SG121TN1D

C425

0.1uF

16V

0.1uF

16V

C436

0.1uF

16V

0.1uF

16V

L403

BLM18SG121TN1D

LAN_CTRL

C426

0.1uF

16V

0.1uF

16V

C431

0.1uF

16V

0.1uF

16V

R489

0

0

L406

BLM18SG121TN1D

C443

1uF 25V

ET_NET

C442

0.1uF16V

ET_NET

C444

1uF 25V

ET_NET

LAN_3.3V

R452

0

R1403 0

R1402 0

R1401 0

R1400 0

R1404

0

R1405

0

R1406

0

R1407

0

R439

0

READY

R442 0

R443

0

R444 0

R456

0

0

R457

0

0

R462

0

R463

0

0

R465

0

READY

R467

0

READY

R479

0

R480 0

R481 0

R490

1

R458

22

22

R496

49.9

ET_NET

R497

49.9

ET_NET

R498

49.9

ET_NET

R499

49.9

ET_NET

R450

100

100

R453

100

100

R464

100

R466

100

R473

1K

R436

1K

R440

1K

READY

READY

R435

10K

10K

R454

10K

10K

R461

10K

R468

10K

R482

10K

10K

R484

10K

R1408

10K

READY

R1409

10K

READY

R478

1M

READY

R483 12K

1/16W

1%

R472

33K

R487

470K

470K

C409

0.01uF

C441

0.01uF

ET_NET

C416 33pF

C417 33pF

C415

0.47uF

25V

Q403

MMBT3904(NXP) E

B

C

Q404

MMBT3904(NXP)

MMBT3904(NXP)

E

B

C

Q406

MMBT3904(NXP)

E

B

C

D400

D401

D402

ET_NET

D403

ET_NET

D404

ET_NET

D405

ET_NET

D411

READY

D412

READY

Q405

AO3407A

G

D

S

C406

0.1uF

16V

ET_NET

ET_NET

R460

18K

18K

R449

18K

18K

MDS62110202

M1

MDS62110202

M2

MDS62110202

M3

JK406

SPG12-DB-0401

1

2

3

4

5

6

7

8

9

10

4 5

EAX

JACK INTERFACE

RS-232C IN/OUT

RGB PC

$0.11

USB

ETHERNET

SWITCH ADDED

Wired IR

AV_L_OUT

AV_R_OUT

AV_IN/L_R OUT

LAN7500

ESD Gasket

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

FRC_DQU[5]

FRC_DQU[0]

FRC_DQL[0]

FRC_DQU[7]

FRC_A[0]

FRC_DQL[1]

FRC_DQU[4]

FRC_A[6]

FRC_A[10]

FRC_A[4]

FRC_DQL[5]

FRC_A[2]

FRC_A[8]

FRC_A[9]

FRC_A[7]

FRC_A[1]

FRC_A[5]

FRC_A[3]

FRC_DQU[6]

FRC_A[11]

FRC_DQL[2]

FRC_A[12]

FRC_DQU[2]

FRC_A[13]

FRC_DQL[4]

FRC_DQL[3]

FRC_DQU[1]

FRC_DQL[7]

FRC_DQU[3]

FRC_DQL[6]

USPI_DO

AVDD_LVDS_3.3V

FRC_DDR3_RESETB

+1.26V_FRC

URSA_PWM1

C509

0.1uF

16V

R509

10K

AVDD33

DVDD_DDR_1V

AVDD_PLL_FRC

R512

10K

R514

10K

READY

R525

100

C534

0.1uF

AVDD_PLL_FRC

USPI_CK

VDDC10

C520

0.1uF

C519

0.1uF

16V

C532

0.1uF

16V

VDDC10

C506

22uF

10V

URSA_MODEL_OPT_3

C533

0.1uF

16V

+3.3V_FRC

C527

0.1uF

16V

R513

10K

READY

R510

10K

READY

FRC_DQSL

R549

33

READY

URSA_MODEL_OPT_1

AVDD33

C526

0.1uF

C508

0.1uF

16V

C500

0.1uF

USPI_DI

C528

0.1uF

R557

33

R507

10K

READY

R524

100

AVDD_DDR

R542

1M

R516

10K

READY

VDD33_FRC

C517

0.1uF

DVDD_DDR_1V

USPI_CK

R551

33

FRC_CASB

C525

0.1uF

+3.3V_FRC

R503

10K

READY

+3.3V_FRC

FRC_MCLK

MOD_SDA_URSA

R508

10K

READY

MOD_SDA_DB

C504

0.1uF

FRC_DQL[0-7]

+3.3V_FRC

FRC_DQSU

URSA_MODEL_OPT_0

L500

CIC21J501NE

FRC_RASB

MOD_SCL_DB

FRC_BA0

C529

0.1uF

R522

33

AVDD_PLL_FRC

URSA_MODEL_OPT_0

FRC_DQSUB

SW500

JS2235S

URSA

3

2

1

4

5

6

FRC_WEB

URSA_PWM0

L502

CIC21J501NE

R502

10K

GPIO[1]

C530

0.1uF

16V

R523

100

R511

10K

C515

10uF

6.3V

URSA_PWM0

C518

0.1uF

16V

R550

4.7K

R505

10K

MOD_SDA_DB

GPIO[8]

L505

CIC21J501NE

R520

4.7K

READY

AVDD_DDR

FRC_ODT

3D_SYNC

R517

10K

C501

0.1uF

+3.3V_FRC

VDD33_FRC

R

5

4

3

0

READY

FRC_DQSLB

C524

0.1uF

R504

10K

READY

C513

0.1uF

AVDD_LVDS_3.3V

L504

CIC21J501NE

VDDC10

3D_SYNC_RF

URSA_MODEL_OPT_1

+3.3V_FRC

L501

CIC21J501NE

R501

22

URSA_MODEL_OPT_3

+1.26V_FRC

AVDD_LVDS_3.3V

FRC_DML

R556

33

USPI_CS

L503

CIC21J501NE

FRC_A[0-13]

C505

0.1uF

USPI_DO

R

5

4

8

0

R

5

4

4

0

R515

10K

R506

10K

C516

0.1uF

USPI_CS

R528

100

R526

100

C503

0.1uF

16V

+1.5V_FRC

+3.3V_FRC

R518

0

C502

0.1uF

16V

FRC_BA1

R

5

4

6

0

URSA_MODEL_OPT_2

VDD33_FRC

FRC_DQU[0-7]

R527

100

R559

33

C521

0.1uF

URSA_MODEL_OPT_2

C511

0.1uF

C514

0.1uF

16V

FRC_MCLKB

FRC_DMU

FRC_CKE

X500

24MHz

R500

22

R

5

4

1

0

R552

10K

URSA_PWM1

+3.3V_FRC

MOD_SCL_URSA

AVDD33

GPIO[1]

R521

33

R558

3.3K

MOD_SCL_DB

R519

4.7K

READY

READY

C510

22uF

10V

GPIO[8]

FRC_BA2

MOD_SDA_URSA

MOD_SCL_URSA

+3.3V_FRC

R547

4.7K

READY

P500

12507WS-04L

URSA

1

2

3

4

5

LVDS_TXA4N

LVDS_TXACLKP

LVDS_TXA0N

LVDS_TXA2P

LVDS_TXA4P

LVDS_TXA1N

LVDS_TXA0P

LVDS_TXA3P

LVDS_TXA1P

LVDS_TXA3N

LVDS_TXA2N

LVDS_TXACLKN

LVDS_TXB1N

LVDS_TXBCLKN

LVDS_TXB0P

LVDS_TXB2P

LVDS_TXB2N

LVDS_TXBCLKP

LVDS_TXB4N

LVDS_TXB3P

LVDS_TXB4P

LVDS_TXB1P

LVDS_TXB3N

LVDS_TXB0N

RXB4-

RXB4+

RXB3+

RXB3-

PDP_SCL

PDP_SDA

C512

0.22uF

C522

0.22uF

C531

1uF

C523

0.22uF

6.3V

C507

22uF

C536

13pF

C535

13pF

USPI_DI

R545

33

FRC_RESET

IC500

LGE7303C

URSA

DDR3_A0/DDR2_NC

P14

DDR3_A1/DDR2_A8

G15

DDR3_A2/DDR2_NC

N14

DDR3_A3/DDR2_A10

L15

DDR3_A4/DDR2_A2

H15

DDR3_A5/DDR2_A3

L14

DDR3_A6/DDR2_A4

G14

DDR3_A7/DDR2_A5

N12

DDR3_A8/DDR2_A6

G13

DDR3_A9/DDR2_A9

N13

DDR3_A10/DDR2_RASZ

H14

DDR3_A11/DDR2_A11

F15

DDR3_A12/DDR2_A0

H13

DDR3_A13/DDR2_A12

P13

DDR3_BA0/DDR2_BA2

M12

DDR3_BA1/DDR2_CASZ

H12

DDR3_BA2/DDR2_A1

L13

DDR3_MCLK/DDR2_MCLK

F16

DDR3_MCLKZ/DDR2_MCLKZ

F17

DDR3_CKE/DDR2_ODT

J13

DDR3_ODT/DDR2_CKE

K12

DDR3_RASZDDR2_WEZ

L12

DDR3_CASZ/DDR2_BA1

K13

DDR3_WEZ/DDR2_BA0

K14

DDR3_RESET/DDR2_A7

M14

DDR3_DQSL/DDR2_DQSL

N16

DDR3_DQSU/DDR2_DQSU

M17

DDR3_DQSBL/DDR2_DQSBL

M16

DDR3_DQSBU/DDR2_DQSBU

M15

DDR3_DQML/DDR2_DQU5

J15

DDR3_DQMU/DDR2_DQU4

R16

DDR3_DQL0/DDR2_DQU3

R17

DDR3_DQL1/DDR2_DQL0

H17

DDR3_DQL2/DDR2_DQL6

R15

DDR3_DQL3/DDR2_DQL7

J17

DDR3_DQL4/DDR2_DQL3

T17

DDR3_DQL5/DDR2_DQL2

H16

DDR3_DQL6/DDR2_DQL1

T15

DDR3_DQL7/DDR2_DQL5

G16

DDR3_DQU0/DDR2_DQU7

K15

DDR3_DQU1/DDR2_DQML

N15

DDR3_DQU2/DDR2_DQU2

K17

DDR3_DQU3/DDR2_DQU6

P17

DDR3_DQU4/DDR2_NC

L17

DDR3_DQU5/DDR2_DQU1

P16

DDR3_DQU6/DDR2_DQU0

K16

DDR3_DQU7/DDR2_DQMU

P15

I2CM_SCL

D14

I2CM_SDA

D15

I2CS_SCL

P1

I2CS_SDA

P2

DDR3_NC/DDR2_A13

F14

DDR3_NC/DDR2_DQL4

T16

VSS_1

D6

VSS_2

D7

VSS_3

D8

VSS_4

D9

VSS_5

E6

VSS_6

E7

VSS_7

E8

VSS_8

E9

VSS_9

E10

VSS_10

E16

VSS_11

F3

VSS_12

F6

VSS_13

F7

VSS_14

F8

VSS_15

F9

VSS_16

G1

VSS_17

G2

VSS_18

G4

VSS_19

G5

VSS_20

G6

VSS_21

G7

VSS_22

G8

VSS_23

G9

VSS_24

G17

VSS_25

H1

VSS_26

H2

VSS_27

H4

VSS_28

H5

VSS_29

H6

VSS_30

H7

VSS_31

H8

VSS_32

H9

VSS_33

H10

VSS_34

H11

VSS_35

J4

VSS_36

J5

VSS_37

J6

VSS_38

J7

VSS_39

J8

VSS_40

J9

VSS_41

J10

VSS_42

J11

VSS_43

J12

VSS_44

J14

VSS_45

J16

VSS_46

K4

VSS_47

K5

VSS_48

K6

VSS_49

K7

VSS_50

K8

VSS_51

K11

VSS_52

L6

VSS_53

L7

VSS_54

L8

VSS_55

L11

VSS_56

L16

VSS_57

M6

VSS_58

M7

VSS_59

M8

VSS_60

M11

VSS_61

M13

VSS_62

N6

VSS_63

N7

VSS_64

N8

VSS_65

N17

VSS_66

P3

VSS_67

P4

VSS_68

P5

VSS_69

P6

VSS_70

P7

VSS_71

P12

VSS_72

U16

NC

L9

HW_RESET

J3

TESTPIN_1

D1

TESTPIN_2

D2

TESTPIN_3

D3

TESTPIN_4

E1

TESTPIN_5

E2

TESTPIN_6

E3

TESTPIN_7

F1

TESTPIN_8

F2

M0_SCLK

C17

M0_MOSI

D16

M1_SCLK

D17

M1_MOSI

E15

M2_SCLK

E14

M2_MOSI

E13

M3_SCLK

E12

M3_MOSI

F13

SPI_CK

T9

SPI_CZ

U10

SPI_DI

U9

SPI_DO

T10

TXA0P/GCLK6/BLUE[7]

C8

TXA0N/GCLK5/BLUE[6]

C9

TXA1P/OPT_N/LK3/BLUE[9]

B8

TXA1N/FLK/BLUE[8]

A8

TXA2P/GREEN[1]

A7

TXA2N/OPT_P/LK2/GREEN[0]

B7

TXACLKP/RLV0N/GREEN[3]

C6

TXACLKN/RLV0P/GREEN[2]

C7

TXA3P/RLV1N/GREEN[5]

B6

TXA3N/RLV1P/GREEN[4]

A6

TXA4P/RLV2N/GREEN[7]

A5

TXA4N/RLV2P/GREEN[6]

B5

TXB0P/RLV3N/GREEN[9]

C4

TXB0N/RLV3P/GREEN[8]

C5

TXB1P/RLVCLKN/RED[1]

B4

TXB1N/RLVCLKP/RED[0]

A4

TXB2P/RLV4P/RED[3]/EPI_A3P

A3

TXB2N/RLV4N/RED[2]/EPI_A3N

B3

TXBCLKP/RLV5N/RED[5]/EPI_A2P

C2

TXBCLKN/RLV5P/RED[4]/EPI_A2N

C3

TXB3P/RLV6N/RED[7]/EPI_A1P

B2

TXB3N/RLV6P/RED[6]/EPI_A1N/

A2

TXB4P/RLV7N/RED[9]/EPI_A0P

C1

TXB4N/RLV7P/RED[8]/EPI_A0N

B1

TXC0P/SOE

C16

TXC0N/POL

B17

TXC1P/GSP_R

B16

TXC1N/GSP/VST

A16

TXC2P/GOE/GCLK1

A15

TXC2N/GSC/GCLK3

B15

TXCCLKP/LLV0N

C14

TXCCLKN/LLV0P

C15

TXC3P/LLV1N

B14

TXC3N/LLV1P

A14

TXC4P/LLV2N

A13

TXC4N/LLV2P

B13

TXD0P/LLV3N

C12

TXD0N/LLV3P

C13

TXD1P/LLVCLKN

B12

TXD1N/LLVCLKP

A12

TXD2P/LLV4N/EPI_B3P

A11

TXD2N/LLV4P/EPI_B3N

B11

TXDCLKP/LLV5N/BLUE[1]/EPI_B2P

C10

TXDCLKN/LLV5P/BLUE[0]/EPI_B2N

C11

TXD3P/LLV6N/BLUE[3]

B10

TXD3N/LLV6P/BLUE[2]/EPI_B1N

A10

TXD4P/LLV7N/BLUE[5]/EPI_B0P

A9

TXD4N/LLV7P/BLUE[4]/EPI_B0N

B9

MOD_GPIO0/VDD_ODD/HSYNC

D10

MOD_GPIO1/VDD_EVEN/VSYNC

D11

MOD_GPIO2/PWM13/GCLK4/LCK

D12

MOD_GPIO3/PWM14/GCLK2/LDE

D13

PWM0/SCAN_BLK1

U12

PWM1/SCAN_BLK2

T12

LPLL_FBCLK

G3

LPLL_OUTCLK

E17

LPLL_REFIN

H3

AVDD_1

F4

AVDD_2

F5

AVDD_DDR_C_1

F10

AVDD_DDR_C_2

G10

AVDD_DDR_D_1

F11

AVDD_DDR_D_2

F12

AVDD_DDR_D_3

G11

AVDD_DDR_D_4

G12

AVDD_LVDS3.3V_1

D4

AVDD_LVDS3.3V_2

D5

AVDD_LVDS3.3V_3

E4

AVDD_LVDS3.3V_4

E5

AVDD_MPLL3.3V

M5

AVDD_LPLL3.3V

L4

AVDD_PLL3.3V

L5

AVDDL_MOD1.26V

K10

DVDD_DDR_1.26V

L10

DVDD_HF1.26V

K9

VD33_1

M4

VD33_2

N4

VD33_3

N5

VDDC_1.26V_1

M9

VDDC_1.26V_2

M10

VDDC_1.26V_3

N9

VDDC_1.26V_4

N10

VDDC_1.26V_5

N11

VDDC_1.26V_6

P10

VDDC_1.26V_7

P11

RXBCLKP

R2

RXBCLKN

R3

RXB0P

R4

RXB0N

R5

RXB1P

T4

RXB1N

U4

RXB2P

U3

RXB2N

T3

RXB3P

T2

RXB3N

U2

RXB4P

T1

RXB4N

R1

RXACLKP

R6

RXACLKN

R7

RXA0P

R8

RXA0N

R9

RXA1P

T8

RXA1N

U8

RXA2P

U7

RXA2N

T7

RXA3P

T6

RXA3N

U6

RXA4P

U5

RXA4N

T5

XTALO

J1

XTALI

J2

GPIO0/(UART_RX/S_PIF_DA0)

R13

GPIO1

P9

GPIO2/(S_PIF_CLK)

T13

GPIO3/(LTD_DA1)

U15

GPIO4/(LTD_DE)

R14

GPIO5/(LTD_CLK)

K2

GPIO6/(LTD_DA0)

K1

GPIO7(3D_FLAG)

T14

GPIO8

P8

GPIO9/(UART_TX/S_PIF_DA1)

U14

GPIO10/(S_PIF_FC)

U13

GPIO11/(S_PIF_CS)

R12

VSYNC_LIKE

E11

M_S_PIF_CLK

N2

M_S_PIF_CS

M1

M_S_PIF_DA0

N1

M_S_PIF_DA1

N3

M_S_PIF_FC

M3

S_M_PIF_CLK

L1

S_M_PIF_CS

M2

S_M_PIF_DA0

L2

S_M_PIF_DA1

K3

S_M_PIF_FC

L3

SOFT_RST_L

R10

SOFT_RST_R

T11

OP_SYNC_L

R11

OP_SYNC_R

U11

IC501

W25X20BVSNIG

URSA

3

WP

2

DO

4

GND

1

CS

5

DIO

6

CLK

7

HOLD

8

VCC

RXBCK+

RXB1+

RXBCK-

RXB1-

RXB2-

RXB0-

RXB2+

RXB0+

R529

0

URSA

R530

0

URSA

R531

0

URSA

R532

0

URSA

R533

0

URSA

R534

0

URSA

R535

0

URSA

R536

0

URSA

R537

0

URSA

R538

0

URSA

R539

0

URSA

R540

0

URSA

3D_SYNC_RF

+3.3V_FRC

R561

0

READY

R562

0

READY

R563

0

READY

R564

0

READY

R565

0

READY

R566

0

READY

R567

0

READY

R568

0

READY

R569

0

READY

R570

0

READY

R571

0

READY

R572

0

READY

P501

12507WS-04L

URSA

1

2

3

4

5

R553

33

R554

33

R555

33

URSA

EAX

5

5

L/DIM_ON

D13

GPIO1 : HI => B8, LOW => B4

LOW

LVDS_NON

_REVERSE

_REVERSE

MIRROR_OFF

MODEL_OPT_0

MODEL_OPT_3

MIRROR_ON

Debugging for URSA5

L/DIM_OFF

CHIP_CONF : {GPIO8, PWM1, PWM0}

CHIP_CONF = 3’d5 : boot from interal SRAM

CHIP_CONF = 3’d6 : boot from EEPROM

CHIP_CONF = 3’d7 : boot from SPI Flash

CHIP_CONF = 3’d5 : boot from interal SRAM

CHIP_CONF = 3’d6 : boot from EEPROM

CHIP_CONF = 3’d7 : boot from SPI Flash

PIN NO.

Place Close to Mstar Pin

[SPI FLASH(2Mbit)]

LVDS_REVERSE

D11

D10

D12

RESERVED

MODEL_OPT_2

MODEL OPTION

(VDDP)

HIGH

PIN NAME

RESERVED

PLACE TERMINATION RESISTORS CLOSE TO URSA5

MODEL_OPT_1

URSA5 CONFIGURATION

Place Close to Bead

Making

6-2

Repair Process

Revision

1/5

PDP TV

Symptom

Picture Problem

No Picture

2012. 7 . 25

Revision

First of all, Check whether all of cable between board was inserted properly or not.

(Main B/D↔ Power B/D, Power B/D↔ Y-sus B/D,Y-Sus B/D ↔Z-Sus B/D,LVDS Cable,…)

Check Module pattern

by using “TILT” key

by using “TILT” key

SVC R/C

Normal

Y

Close

Check

LVDS Cable

Normal

Y

on SVC R/C

N

Replace

Main B/D

N

Check

Vs, Va

Y

Normal

Check voltage

. -V

Y

. V

SC

V

ZB

Y

Check B+ Voltage

on Power Board

on Power Board

/ Control Board

Check B+(5V)

Y

1.Check Control Board

. LED on

. Crystal(X101)

. 1.8V, 3V, 5V FET

. Crystal(X101)

. 1.8V, 3V, 5V FET

Rom update

Normal

Normal

N

. V

ZB

N

1. Check Y-Sus/ Z-Sus Board

2. Replace defective B/D

2. Replace defective B/D

.Check B+(5V)

. Rom update

2.Replace Control B/D

Move

Power problem

Section

Move

Power problem

Section

N

※Refer to the Module label for each voltage

<SVC R/C & Pattern>

Click on the first or last page to see other C42PW120-WA (CHASSIS:PC21A) service manuals if exist.