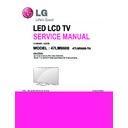

LG 47LM9600 (CHASSIS:LB23E) Service Manual ▷ View online

L9

LG1152D

AUD

BB_TP_DATA

DAC_DATA

AAD_DATA

HSR_P/M

CVBS

SIF

Tuner

PC_AUDIO

PC_Audio L/R

AV 1_Audio L/R

PC-RGB

A/V1

COMP1

A/V1_CVBS

Comp1 Y,Pb,Pr

PC_R,G,B,H,V

HDMI

Switch

HDMI1~4

L9

LG1152A

USB1

USB2

USB3

USB

HUB

HUB

PHY

RMII

LAN

Motion-R

M-Remote_R/TX

Audio

AMP

OPTIC

SPK

SPDIF

I2S

16

DDR

16

DDR

256MB×4

(1600)

128MB×1

(1600)

8

eMMC

4GB×1

Built-in WiFi

3D Depth

LG1132

FRC-III

LG1122

mini_LVDS

mini_LVDS

T-con

LG5812

HS_LVDS

2Link

HS_LVDS / 2Link

V by One / 8 Line

CHB_DATA

FE_TS_DATA[0-7]

FE_TS_SYNC

FE_TS_ERR

FE_TS_CLK

FE_TS_CLK

FE_TS_VAL

<Parallel TS>

USB

DIF (

DA ONLY

)

(

SA ONLY

)

4. Block Diagram for High-end models(Main + BE)

* FHD 240Hz, T480Hz ( 47/55LM9600)

80Pin

Mini -LVDS

Output

L9D

(LG1152)

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

FRC-III

(LG1122)

FRC-III

(LG1122)

3D Chip

(LG1132)

3D Chip

(LG1132)

T-Con

(LG5812)

T-Con

(LG5812)

2 link

HS-LVDS

51P Cable

2 link

HS-LVDS

8 lanes

VbyOne

Mini-LVDS

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

80Pin

Mini -LVDS

Output

Main Board

T-Con Board

Mini-LVDS

8P L/Dimming

LED Driver

240Hz

LCM

eMMC

4Gb

eMMC

4Gb

50Pin

EPI

L9D

(LG1152)

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

FRC-III

(LG1122)

FRC-III

(LG1122)

3D Chip

(LG1132)

3D Chip

(LG1132)

T-Con

(LG5822)

T-Con

(LG5822)

2 link

HS-LVDS

51P Cable

2 link

HS-LVDS

4 lanes

LVDS

EPI

DDR3@

800MHz

800MHz

DDR3@

800MHz

800MHz

50Pin

EPI

Main Board

T-Con Board

EPI

8P L/Dimming

LPB (LED Driver)

120Hz

LCM

eMMC

4Gb

eMMC

4Gb

4. Block Diagram for High-end models(Back-end)

* FHD 120Hz, T240Hz ( 47/55LM8600)

* FHD 240Hz T480Hz ( 72LM9500)

4. Block Diagram for High-end models(Back-end)

DDR3 SDRAM

-

1Gbit (x16)

-

800MHz

DDR3 SDRAM

-

1Gbit (x16)

-

800MHz

DDR1_DATA[15:0]

DDR1_A[13:0]/

BA[2:0]/CLK/CKE

DDR0_DATA[15:0]

DDR0_A[14:0] /

BA[2:0]/CLK/CKE

DC-DC Con

(TPS54327)

DC-DC Con

(TPS54327)

+2.5V

SPI_DO/CK/CS

SPI_DI

SPI FLASH

(32Mbit)

SPI FLASH

(32Mbit)

DC-DC Con

(TPS54327)

DC-DC Con

(TPS54327)

L/DIM0_VS,

L/DIM0_SCLK/MOSI

DDR3 SDRAM

-

1Gbit (x16)

-

800MHz

DDR3 SDRAM

-

1Gbit (x16)

-

800MHz

FRC-III

(LG1122)

(0x1C, direct

0xB2, in-direct)

XTAL_IN

XTAL_OUT

X-Tal

(24.75Mhz)

LG1121_RESET

8Lane Vx1 HS

Dual-Link HS-LVDS

VL

CD

_P

OW

ER

(+

12V

)

LG

112

1__RESET

I2C_SDA

_S

I2C_S

CL

_S

PMIC

(MAX17139)

PMIC

(MAX17139)

VCC/VDD/

VGH_A/VGL/

HVDD/VCORE

VLCD_POWER(+12V)

I2C_SDA_S

I2C_SCL_S

L/DIM0_VS

L/DIM0_MOSI/SCLK

I2C_SDA_S

I2C_SCL_S

+1.8V

VLCD_POWER(+12V)

VLCD_POWER(+12V)

* Epoxy 4Layer 1.2T (206x183mm)

TX_

LOCK

LOCK

GM

A[

4:

1]

/

G

M

A[14:10]

VCC/

V

D

D

P-

G

A

MMA

IC

–

Ma

ster

1

(B

UF0683

0)

P-

G

A

MMA

IC

–

Ma

ster

1

(B

UF0683

0)

VC

OM

I2C_SDA

_S

I2C_S

CL

_S

VCC/

V

D

D

GM

A_

M

[9

:5

]

/

G

M

A_M[18:15]

P-

G

A

MMA

IC

–

Ma

ster

2

(B

UF0683

0)

P-

G

A

MMA

IC

–

Ma

ster

2

(B

UF0683

0)

I2C_SDA

_S

I2C_S

CL

_S

80

P m

ini

-LV

DS

O

utput

RIGHT

LGE 240Hz

T-Con

(L

G

5812,

0x70

)

OPT

_N

/O

PT_

P/

GS

P/GS

C/

GO

E

VDD/

V

CC

/

H

VDD/

VG

L/

VG

H

/

VC

OM

R

/

G

M

A[18:1]

VC

OM

R

FB

VDD/

V

CC

/

H

VDD/

VG

L/

VG

H

/

VC

OM

/

G

M

A[18:1]

VC

OM

LF

B

TCON

_SDA

TCON

_SC

L

EEPROM

(AT2

4C32D,

32

Kb

it

)

EEPROM

(AT2

4C32D,

32

Kb

it

)

I2C_SDA

_S

I2C_S

CL

_S

80

P m

ini

-LV

DS

O

utput

LEFT

OPT

_N

N

/O

PT

_P

/

SOE/

POL

/

H_CO

N

V

/

GS

C/GO

E

OPT

_N

/

SOE/

POL

H

_C

O

NV

/GS

C/GO

E

HF min

i-LVD

S

(2

-L

in

k)

HF min

i-LVD

S

(2

-L

in

k)

[S]

TCON

_SDA

TCON

_SC

L

[M]

80

P m

ini

-LV

DS

O

O

utput

RIGHT

LGE 240Hz

T-Con

(L

G

5812,

0x70

)

OPT

_N

/O

PT_

P/

GS

P/GS

C/

GO

E

E

VDD/

V

CC

/

H

VDD/

VG

L/

L/

VG

H

H

/

VC

OM

R

OM

R

/

G

M

A[18:1]

VC

OM

R

OM

R

FB

VDD/

V

CC

/

H

VDD/

VG

L/

L/

VG

H

H

/

VC

OM

/

OM

/

G

M

A[18:1

]

VC

OM

LF

OM

LF

B

TCON

_SDA

TCON

_SC

L

EEPROM

(AT2

4C32D,

32

Kb

it)

EEPROM

(AT2

4C32D,

32

Kb

it)

I2C_SDA

_S

I2C_S

CL

_S

80

P m

ini

-LV

DS

O

O

utput

LEFT

OPT

_N

N

/O

PT

_P

/

SOE/

POL

/

/

H_CO

N

V

/

GS

C/GO

E

E

OPT

_N

/

SOE/

POL

H

_C

O

NV

/GS

C/GO

E

/GS

C/GO

E

HF min

i-LVD

S

(2

-L

in

k)

HF min

i-LVD

S

(2

-L

in

k)

[S]

TCON

_SDA

TCON

_SC

L

[M]

GM

A[

A[

4:1

] /

G

M

A[14:10]

VCC/

V

D

D

P-

G

A

MMA

IC

–

Ma

ster

1

ster

1

(B

UF0683

0)

P-

G

A

MMA

IC

–

Ma

ster

1

ster

1

(B

UF0683

0)

VC

OM

OM

I2C_SDA

_S

I2C_S

CL

_S

VCC/

V

D

D

GM

A_

A_

M

[9

:5

] /

G

M

A_M[18:15]

P-

G

A

MMA

IC

–

Ma

ster

2

ster

2

(B

UF0683

0)

P-

G

A

MMA

IC

–

Ma

ster

2

ster

2

(B

UF0683

0)

I2C_SDA

_S

I2C_S

CL

_S

DC-DC Con

(TPS54327)

DC-DC Con

(TPS54327)

+1.5V

+3.3V

DC-DC Con

(TPS54327)

DC-DC Con

(TPS54327)

VLCD_POWER(+12V)

PMIC

(MAX17139)

PMIC

(MAX17139)

VCC/VDD/

VGH_A/VGL/

HVDD/VCORE

VLCD_POWER(+12V)

I2C_SDA_S

I2C_SCL_S

+0.9V

DC-DC Con

(AOZ1038PI)

DC-DC Con

(AOZ1038PI)

VLCD_POWER(+12V)

DC-DC Con

(TPS54327)

DC-DC Con

(TPS54327)

+1.8V

VLCD_POWER(+12V)

VLCD_POWER(+12V)

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

Vx1

Rep

I2C HUB

(PCA9516)

I2C HUB

(PCA9516)

I2C_EN_M

I2C_EN_S

I2C_SDA_1

I2C_SCL_1

I2C_SDA_2

I2C_SCL_2

I2C_SDA_S

I2C_SCL_S

8Lane Vx1 HS

8Lane Vx1 HS

5. Jack Interface for High/Middle models

[SPDIF_OUT]

Main SoC

[Y1P],[PB1P],[PR1P]

[OPCTRL9]

[VGA_SCL]

[VGA_SDA]

[OPCTRL7]

[VSYNC], [HSYNC]

[RP],[GP],[BP]

SPDIF(AUDIO OPTIC)

SPDIF_OUT

[AIN2_L_AADC]

COMP PHONE JACK

COMP1_Y/Pb/Pr

COMP1_DET

[AIN3_R_AADC]

[AIN3_L_AADC]

[CVBS0P]

[OPCTRL5]

AV1_L_IN

AV1_R_IN

AV1_CVBS_DET

AV1_R_IN

AV1_CVBS_DET

AV1_CVBS_IN

AV PHONE JACK

RGB_PC

RGB_DDC_SCL

RGB_DDC_SDA

DSUB_DET

DSUB_VSYNC, DSUB_HSYNC

DSUB_R+, DSUB_G+, DSUB_B+

PC AUDIO

PC_L_IN

PC_R_IN

[AIN2_R_AADC]

CVBS 1

Phone JACK _Yellow

Component 1

Phone JACK _Green

LAN

EPHY_TDP/TDN //RDP/RDN

Air

Analog 2~69ch

Digital 2~69ch

Analog 2~69ch

Digital 2~69ch

Cable

Analog 1~125ch

Analog 1~125ch

Main SoC

USB DM3 / DP3

USB3

APPS

USB2

USB HUB

USB_DM2 / DP2

USB1

DVR Ready

DVR Ready

USB_DM1 / DP1

HDMI1 /ARC

HDMI2

HDMI3

HDMI4 / PC

HDMI1 D0/D1/D2/CLK/SCL/SDA/HPD

HDMI2 D0/D1/D2/CLK/SCL/SDA/HPD

HDMI3 D0/D1/D2/CLK/SCL/SDA/HPD

HDMI4 D0/D1/D2/CLK/SCL/SDA/HPD

HDMI

MUX

USB

MUX

REAR

SIDE

Click on the first or last page to see other 47LM9600 (CHASSIS:LB23E) service manuals if exist.