Sharp MX-6240N / MX-7040N (serv.man34) Service Manual ▷ View online

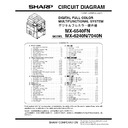

MX-7040 BLOCK DIAGRAM / ブ ロ ッ ク 図

1 – 4

SCANNER CONTROL PWB (2/2)

MFPC PWB

POF

to CPU

LANcnt signal/Communication request/POF

POF signal

Rycnt/OFFcnt signal

LCDSEL0, LCDSEL1

24V/5V/3.3V

from CPU

CCFT

LED backlight

Image data

LCD display

LCD_DISP

Image data

SYNC

24VM5, 5V, 3.3V

12VL

12VL

24V

12VL

Recovery trigger

24V, 5VL, 5Vo, 3.3V

5Vo

LED lighting

24V/5Vo/5VL/3.3V

5VL

24V/12VL

24VM5/12V/5Vo/5V/3.3V

5Vo

Rycnt/OFFcnt signal

Communitarian,

etc.

etc.

POF signal

LANcnt signal/Communication request/POF

SCN-MotherCNT PWB

LSUcnt PWB

LVDS PWB

10.1inch LCD

FAX

Power supply

USB

IO ASIC

Orditor

(TBD)

PIC

Recovery trigger

Right tray

SPED

USB HUB

USB CN PWB

(Front USB)

KEYBOARD PWB

IC CARD

READER

HDD

FAN

MFPC

FAN

HDD

FAN

FAN

SUB power

FAN

RxFPD link

TxFPD link

PCU PWB

FAX reception lamp

PWB

DC PWB

SUB DC

PWB1

SUB DC

PWB2

FAX main

PWB

TxFPD link

RxFPD link

RxFPD link

FAX

reception LED

DCCNT

PWB

Recovery trigger

Recovery trigger from FAX

LED lighting

FAX reception notifying LED

Reserve

MX-7040 BLOCK DIAGRAM / ブ ロ ッ ク 図

1 – 5

4. OPERATION UNIT / オペ レ ーシ ョ ンユニ ッ ト

FI-RE41S-HF

FI-RE41S-HF

CN

CN4

CN3

40Pin

Thin

line

coaxial

41Pin

Differential

signal

TCLK

FPD

L

inc

R

[7:2]

F

PD

Linc

Differential

signal

TCLK

41Pin

41Pin

Differential

signal

TX_OUT0

V385

G[7:2]

VP386

Differential

signal

TX_OUT0

Differential

signal

TX_OUT1

IC3

B

[7:2]

IC1

Differential

signal

TX_OUT1

Differential

signal

TX_OUT2

Differential

signal

TX_OUT2

CK_in

Hsync

Vsync

ENAB

3.3V

3.3V

KRC102S

QB1

CCFT_out

CCFT_out

/CCFT_in

/CCFT

DISP_out

PST8427UR

ICB1

3.3V

DISP_out

3.3V

NJM78M18DL1A

IC5

18V_LCD

18V_LCD

24V

RP131S331D-E2-F

IC4

nLCD_DISP

3.3V

5V

52271-046

9

BM08B-GHS-TBT

CN2

CN1

CN

CN

/YL(Y1)

/YL(Y1)

XH(X1)

XH(X1)

/XL(X2)

/XL(X2)

YH(Y2)

YH(Y2)

SM11B-GHS-TB

CN1

CN

CN

Home

key

Home

LED

Buzzer

Power

SW

Power

LED

Power-saving

SW

Power-saving

LED

CN

CN

SHIELD1

CN1

GND

D1+

D1-

VBUS1

nINFO_LED

CN3

CN

CN

24pin

CN

GND

CN1

D1+

00

6200

524

330

000+

D1-

VBUS

Wire

harness

Wire

harness

Wire

harness

Wire

harness

Wire

harness

Kyeboard

USB

c

onnector

PWB

TP_IF_PWB

SCN_MOTHER_PWB

KEY

P

WB

OPE

UN

10.1LCD

U

N

101LVDS_P_

P

WB

Touch

p

anel

USB

C

ONV

P

WB

MX-7040 BLOCK DIAGRAM / ブ ロ ッ ク 図

1 – 6

5. MFP CONTROL PWB / MFP コ ン ト ロール PWB

USB

HUB

PIC

Micon.

SCN-Mother

PWB

U

A

R

T(ch6)

USB

2

.0

Host

LV

DS

(Scan)

LVDS

(LSU

CLK&SYNC)

UART(1ch)

LSU

PWB

LV

DS

(Scan)

DualScan

Reus

2

(subCPU)

DDR2/3

IF

Local

B

us

IF

LSU

IF

FPDLINK

T

ransmitter

PCIe

IF

(1lane)

SCN

IF

PCIe

IF

(4lane)

SA

T

A

IF

SD

EtherMA

C

10/100/1G

EtherMA

C

10/100/1G

USB2.0

IF

De

vice

Non-interr

u

ption

a

rea

(Not

used)

I2C(2/3ch)

Controller

I2C(1/3ch)

Controller

UA

R

T

(11ch)

UA

R

T

(1ch)

INT

(1/3ch)

INT

GPIO

INT

(3/3ch)

INT

(2/3ch)

DDR3

SO-DIMM

SOCKET2

Reus

1

(mainCPU)

DDR2/3

IF

Local

B

us

IF

PCIe

IF

(1lane)

SCN

IF

PCIe

IF

(4lane)

SD

EtherMA

C

10/100/1G

EtherMA

C

10/100/1G

USB2.0

IF

De

vice

USB2.0

IF

Host

SD

Soc

k

et

SDHC

4GB

DDR3

S

O-DIMM

1GB

DDR3

SO-DIMM

SOCKET1

Non-interr

uption

area

(ON

w

hen

LAN

standb

y)

I2C(3/3ch)

Controller

EtherPHY

10/100/1G

LAN

J

A

C

K

RJ45

USB

D

e

v

ice

TYPE-B

CN

FPDLINK

Receiv

er

I2C(1/3ch)

Controller

F

AX(2nd)

CN

UA

R

T

(11ch)

UA

R

T

(1ch)

DSUB

CN

(RIC

,PCI,C

oinV

ender)

I2C(2/3ch)

Controller

MFPC

PWB

INT

(1/3ch)

INT

(1/4ch)

DDR3

S

O-DIMM

Opt.

GMII

Interr

uption

area

(OFF

when

L

AN

standb

y)

INT(Sleep)

USB

2

.0

De

vice

480Mbps

GPIO

POF

U

A

R

T

(1ch)

RS232C

Le

v

e

l

Con

v

er

ter

1Gbps

3.0Gbps

INT

(3/3ch)

INT

(2/3ch)

INT(W

a

leUp)

INT

(nF

A

X12_PIC_INT)

nF

AX12_PIC_INT

U

A

R

T

(ch10)

CPLD

RT

C

A

CRE

Opt

CN

AC

R

E

PWB

(Option)

EEPR

OM

256kb

I2C

360KHz

Local

B

us

I2C

360KHz

I2C

9

5KHz

UA

R

T

PCIe

x1

DDR3

SO-DIMM

1GB

DDR3SO-DIMM

SOCKET1

FPDLINK

Receiv

er

U

A

R

T

(ch

9

)

U

A

R

T

(ch1/4)

F

AX(3nd)

CN

U

A

R

T

(ch2/5)

PCIe

x4

Gen1

FLASH

DIMM

FLASH

D

IMM

SOCKET

Interr

uption

a

rea

(OFF

when

LAN

standb

y

)

Intel

ICH8

DMI

SA

T

A

DDR3

SO-DIMM

2GB

DDR3

SO-DIMM

SOCKET1

DDR3

SO-DIMM

SOCKET2

I2C

9

5KHz

PCIe

IF

(4lane)

USB

PCIe

x4

Gen1

PCI

E

xpress

Switch

Intel

Pine

vie

w

D525

1.8GHz

DDR2/3

IF

SMb

us

DMI

SPI

CK505

Cloc

kGen

SPIFlash

(BIOS)

PCIe

x4

Gen1

PCIe

x4Gen1

PCIe

IF

(1lane)

HDD

3

.5'

1TB

Mirror

ing

(Opt.)

HDD

3

.5'

1TB

FA

X

(3

rd

)

(Opt.)

F

A

X(2nd)

(Opt.)

CN

Update

SW

PCIe

IF

(1lane)

INT(POF)

I2C

Logic

IC

SA

T

A

CN

Raid

PWB

3.5inch

I2C

Cloc

kGen

I2C

Ser

ial

CN2

(Deb

ug)

U

A

R

T

(ch

9

)

USB

H

ost

TYPE-A

C

N

INT

To

IC

H

8

INT

To

IC

H

8

To

Reus1

To

ICH8

por

t1-4

por

t1

CF

PATA

CF

CN

CF

4GB

Prog

ra

m

USB

Wireless

LAN

(Opt.)

U

A

R

T

(ch8)

Ser

ial

CN2

(Deb

ug)

PCI(sub)

CN

U

A

R

T

(ch8)

LCD

IF

PCU

P

WB

U

A

R

T

(ch7)

F

A

X(1st)

U

A

R

T(ch0/3)

OPE

UN

CPU(H8S)

F

ront

USB

LCD

IF

Boardt

oB

oardConnector

LV

D

S

MX-7040 BLOCK DIAGRAM / ブ ロ ッ ク 図

1 – 7

6. LSU CNT PWB

LSU CNT PWB (1/2)

LSU_ASIC

CHIP-2

LSU_ASIC

CHIP-1

SCN

Mother

Thermistor

Motor control

PCU

8

PCU I/F

Register

etc...

SCK

RSV_DAT

TRANS_RST

TRANS_DAT

JOBEND_INT_Y

Clock synchronization serial communication

Thermistor output

PCU_TRG

Print trigger input

AMP

Reset IC

Reset input

Hard reset

35:5

ID[0:0]

ID[0:1]

I2C

ROM

I2C

ROM

I2C BUS

ASIC

to CHIP-2/3/4

Hard reset

SCK

RSV_DAT

TRANS_RST

TRANS_DAT

Clock synchronization serial communication

JOBEND_INT_M

System CK

HSYNC/ECLK

35:5

Print trigger chain

LD

Polygon

control

control

Fan

control

I2C BUS

DT_Y1+-

3

2

DT_Y2+-

2

DT_Y3+-

2

DT_Y4+-

2

FPD-LINK/Reciver

Motor control

Polygon

control

Fan

control

Serial

D/A I/F

LD control

LD control

(APC etc.)

(APC etc.)

Oscillator

(CK for 330mm/s)

Oscillator

(CK for 300 or 360mm/s)

Oscillator

(CK for 220mm/s)

OSCCLK_C

OSCCLK_M

OSCCLK_A

CLK_C_EN

CLK_M_EN

CLK_A_EN

TH

nVSYNC_M

8

DT_M1+-

2

DT_M2+-

2

DT_M3+-

2

DT_M4+-

2

ASIC

to CHIP-2/3/4

ASIC

from CHIP-2/3/4

LSU_ASIC

CHIP-3

BD

PCU I/F

Register etc...

Channel A: M1 circuit

Channel B: M2 circuit

Channel C: M3 circuit

Channel D: M4 circuit

Channel A: Y1 circuit

Channel B: Y2 circuit

Channel C: Y3 circuit

Channel D: Y4 circuit

Main scanning,

Sub scanning

timing control

System CK

HSYNC/ECLK

nVSYNC_Y

Serial

D/A I/F

LD control

LD control

(APC etc.)

(APC etc.)

Print trigger chain

BD

MFPC

Or

EFI

Thermistor

2

Thermistor output

AMP

TH2

4

MSET_M/Y

4

2

P4_Y_AK1(ENB)

P4_Y_AK2(ENB)

P4_Y_AK2(ENB)

MicroWire BUS

SCLK/TXD/RXD

3

Chip select(EEP-ROM)

CS EEP-ROM K/C/M/Y

8

Chip setect(LDD)

CS K/C/M/Y

8

2

P4_M_AK1(ENB)

P4_M_AK2(ENB)

P4_M_AK2(ENB)

JOBEND_INT

JOBEND_INT_M

JOBEND_INT_C

JOBEND_INT_K

nJOBEND_INT_Y

nJOBEND_INT_M

nJOBEND_INT_C

nJOBEND_INT_K

nINT STM/Y

P3_M_AK1

P3_WAIT_AK1

P3_M_AK2

P3_WAIT_AK2

nSEL_ADJ_M

P3_ADJ

P3_Y_AK1

P3_WAIT_AK1

P3_Y_AK2

P3_WAIT_AK2

nSEL_ADJ_Y

P3_ADJ

Main scanning,

Sub scanning

timing control

FPD-LINK/Reciv

er

Click on the first or last page to see other MX-6240N / MX-7040N (serv.man34) service manuals if exist.