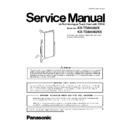

Panasonic KX-TDA6382X / KX-TDA6382SX Service Manual ▷ View online

8

KX-TDA6382X/KX-TDA6382SX

4.2.

Circuit Operations

4.2.1.

Description of Control System Circuits

4.2.1.1.

Reset

On startup, releasing the ASIC reset is executed by EC_nRST through MPR.

After releasing the ASIC, the local reset signal should be sent to CODEC by releasing the soft rest from MPR, and CODEC fac-

tor should be downloaded from MPR.

After releasing the ASIC, the local reset signal should be sent to CODEC by releasing the soft rest from MPR, and CODEC fac-

tor should be downloaded from MPR.

• LED operational state display LED (2 colors)

Red ON: Fault (includes RESET)

Green ON: INS (line free)

Green flash (60/sec): INS (line busy)

Red flash (60/sec): OUS

OFF: the power section failure

Green ON: INS (line free)

Green flash (60/sec): INS (line busy)

Red flash (60/sec): OUS

OFF: the power section failure

4.2.1.2.

Local Highway Interface

Packs 2.048, 4.096, 8.192 MHz highway (Max.64 timeslot). (voice communication bus in the circuit board)

The PCM data of arbitrary streams 0~15 (128 timeslot / 1 stream) on the CT bus can switch to the arbitrary local highway (64

timeslot) by the local TSW.

The timeslot configuration example of the local highway is shown below.

Timeslots between slot 8 and slot 15 are used by the Sub Board.

The PCM data of arbitrary streams 0~15 (128 timeslot / 1 stream) on the CT bus can switch to the arbitrary local highway (64

timeslot) by the local TSW.

The timeslot configuration example of the local highway is shown below.

Timeslots between slot 8 and slot 15 are used by the Sub Board.

Slot

PCM Data

Slot

PCM Data

Slot

PCM Data

0

CO#1

16

Not used

32-63

Not used

1

CO#2

17

Not used

2

CO#3

18

Not used

3

CO#4

19

Not used

4

CO#5

20

Not used

5

CO#6

21

Not used

6

CO#7

22

Not used

7

CO#8

23

Not used

8

CO#9

24

Not used

9

CO#10

25

Not used

10

CO#11

26

Not used

11

CO#12

27

Not used

12

CO#13

28

Not used

13

CO#14

29

Not used

14

CO#15

30

Not used

15

CO#16

31

Not used

Software reset

EC_nRST

IC3

Reset IC

IC4

+5V

+3.3V

+3.3V

+3.3V

(Green)

LED

(Red)

P22

P23

nHALT

U1-1/2

Q3

System reset in ASIC

E

C

B

U

S

C

B

U

S

LPR reset

ASIC

RST

LED

CPU

IC401

nlRQ0

nRES

9

KX-TDA6382X/KX-TDA6382SX

4.2.1.3.

ASIC...IC3

• EC bus Interface

16bit/8MHz two-way address data multiplex self-bus (communication bus with MPR)

• CT bus Interface

Supports eight of 8.192MHz highway (128 timeslot) (voice communication bus with MPR)

• Local TSW

Timeslot switching between CT bus (1024ch) and local highway (64ch)

(Timeslot switching between the voice communication bus in MPR and that in the circuit board)

(Timeslot switching between the voice communication bus in MPR and that in the circuit board)

• Local Gain Control

Gain control of the local highway up-down 64ch by 1dB/step randomly

• GPIO Interface

A parallel interface that can be set in random interactively

Refer to IC3 (ASIC) (P.64).

Refer to IC3 (ASIC) (P.64).

Host-EC

bridge

(slave)

CT_IF

Local

TSW

Host

Local-bus I/F

DPLL

JTAG

GAIN

Internal Highway

Internal bus

System bus

APT

controller

HDLC

8ch

FIFO/

DPRAM

DPT

controller

Local

Highway I/F

PT

DR/RV

GPIO

CODEC

Controller

RT_SND

CS-IF

Local

Bus

EC

CT

Highway

PT-I/F

GPIO-i/f

CS-I/F

10

KX-TDA6382X/KX-TDA6382SX

4.2.1.4.

8-Port Sub Board

8-Port Sub Board is mounterd to Main Board.

DT_OE[15]

DT_OE[11]

DT_OE[13]

DT_OE[12]

DT_OE[14]

DT_OE[8]

DT_OE[9]

DT_OE[8-15]

D[0-7]

DT_OE[10]

DT_OE[13]

DT_OE[15]

LA[0-5]

DT_OE[9]

R[14]

R[15]

R[8]

R[10]

R[9]

R[11]

R[13]

R[12]

T[8]

DT_OE[8]

LA[1]

LA[2]

LA[5]

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

LA[4]

LA[0]

LA[3]

DT_OE[12]

T[9]

T[10]

T[11]

T[12]

T[13]

T[14]

T[15]

DT_OE[11]

DT_OE[14]

DT_OE[10]

OPT[1]

DG

DG

CLK

FH

DHW

UHW

C_CS[2]

C_CS[3]

DCLK

DIN

DOUT

DG

+5V

nRD

CLK

nWR

nCS_CID[1]

nRST

11

19

31

17

18

49

57

22

56

28

52

21

51

48

55

2

1

47

3

29

30

59

34

33

53

23

4

45

60

17

25

27

15

13

19

26

54

6

5

7

38

3

9

32

12

8

8

13

CN8

5

24

20

46

50

16

43

40

58

39

7

10

15

41

11

42

14

36

35

6

37

9

12

44

CN2

12

34

CN2

9

CN2

10

35

37

CN2

11

36

CN2

13

38

CN2

14

39

CN2

15

40

CN2

16

41

5

6

7

8

5

6

7

8

CN6

1

2

14

16

18

4

10

20

J1I

J1J

J1K

J1L

J1M

J1N

J1O

J1P

SFG

+3.3V

+2.5V

DG

TH1I

TH1J

TH1K

TH1L

TH1M

TH1N

TH1O

TH1P

+15V

DG

C

928

C

929

C

930

C

931

SFG

C9

1

C9

0

RA

6

R

A

5

11

KX-TDA6382X/KX-TDA6382SX

4.2.2.

Description of Functions and Circuits

4.2.2.1.

Dial Pulse Signal Transmission

Transmits 10pps/20pps dial pulse by a open/close action between Tip and Ring with Photo MOS relay.

The make width, break width and inter digital width for 10pps/20pps can be set respectively.

When making, 37pin (DIAL [0]) of IC6 becomes Low level, and RL3 turns ON. When breaking, 37pin (DIAL [0]) of IC6 becomes

High level, and RL3 turns OFF.

The make width, break width and inter digital width for 10pps/20pps can be set respectively.

When making, 37pin (DIAL [0]) of IC6 becomes Low level, and RL3 turns ON. When breaking, 37pin (DIAL [0]) of IC6 becomes

High level, and RL3 turns OFF.

It provides the SHUNT control function for the stabilization of line power depending on the destination. Turning ON PC5 when

transmitting pulse reduces the impedance at making, and stabilizes the line power.

transmitting pulse reduces the impedance at making, and stabilizes the line power.

4.2.2.2.

Circuit For Line Acquisition

Making CODEC (e.g. pin-37 of IC6, DIAL [0]) Low level, the photo MOS relay (RL3) turns ON and the line is acquired.

It is used in common as Dial Pulse transmitting circuit.

It is used in common as Dial Pulse transmitting circuit.

DC Loop Path:

• Ring

• Ring

L1D1D2J7D3RL3Q4(C-E)D4D3L1TH1Tip

• Tip

TH1L1D3D4Q4(C-E)RL3D3J7D2D1L1Ring

R[0]

T[0]

AG

+5V

DG

DG

DG

DG

DG

+5V

+5V

+5V

+5V

+5V

SFG

R

20A

PC5A

1

2

3

4

R

17A

D2A

R3

A

T1A

2

1

3

4

C1

A

C2

A

C4

A

C8A

D1A

D4

A

R21A

R

11A

R

14A

R15A

R16A

R1

8

A

R

19A

R1

A

R22A

R2

A

R4A

1.2K

R5

A

R6

A

J1A

RL

2

A

4

3

2

1

J4A

PC1A

1

23

4

PC2A

1

2

3

4

PC

4

A

1

2

3

4

L1A

1

2

3

4

C3

A

CN3 2

CN3 3

J7

A

C6

A

C7A

Q5A

E

C

B

ZN

R

2

A

CN2

1

26

D3A

1

2

3

4

TH1A

ZN

R

1

A

RL3A

4

3

2

1

D5

A

SA

1

A

12

3

Q4A

E

C

B

A

Ring

Tip

CODEC

IC6

R[0]

T[0]

AG

+5V

DG

DG

DG

DG

DG

+5V

+5V

+5V

+5V

+5V

SFG

R

20A

PC5A

1

2

3

4

R

17A

D2A

R3

A

T1A

2

1

3

4

C1

A

C2

A

C4

A

C8A

D1A

D4

A

R21A

R

11A

R

14A

R15A

R16A

R

18A

R

19A

R1

A

R22A

R2

A

R4A

R5

A

R6

A

J1A

RL

2

A

4

3

2

1

J4A

PC1A

1

23

4

PC2A

1

2

3

4

PC

4

A

1

2

3

4

L1A

1

2

3

4

C3

A

CN3 2

CN3 3

J7

A

C6

A

C7A

Q5A

E

C

B

ZN

R

2

A

CN2

1

26

D3A

1

2

3

4

TH1A

ZN

R

1

A

RL3A

4

3

2

1

D5

A

SA

1

A

12

3

Q4A

E

C

B

A

Ring

Tip

CODEC

IC6

Click on the first or last page to see other KX-TDA6382X / KX-TDA6382SX service manuals if exist.