Panasonic KX-TDA620BX Service Manual ▷ View online

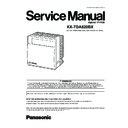

8.1.3.

Block

Diagram

CPU

SH4

IC200

FLASH

4MB

SDRAM

16MB

SRAM

Main_BUS

1MB

ASIC

IC101

EC_BUS

CT_BUS

LED

Add/Data

Driver

3.3V

1.5V

OSC16M

90pin

16.384MHz

Circ-

Link

IC401

OSC40M

LV

D

D

S

RST IC

3.3V

System TSW

IC501

LV

D

D

S

SHWU[2:0]

CPU_STATUS[1:0]

SHW_CLK,SHW_nFH

FPGA

IC402

1/2

+15V

GND

3.3V_BB

EC_CLK

EC_nRST

EC_AD[15:0]

EC_CBE[1:0]

EC_PAR

EC_nFRAME

EC_nTRDY

EC_nSTOP

EC_nPERR

EC_nCDET

EC_nINT

EC_IDSEL

GND

3.3V_BB

EC_CLK

EC_nRST

EC_AD[15:0]

EC_CBE[1:0]

EC_PAR

EC_nFRAME

EC_nTRDY

EC_nSTOP

EC_nPERR

EC_nCDET

EC_nINT

EC_IDSEL

CT_NETREF

CT_D[7:0]

CT_C8

CT_D[7:0]

CT_C8

RINGER

nHALT

POW_TYPE[1:0]

M/nS

MASTER/nS

LEDRUN

LEDALM

nHALT

POW_TYPE[1:0]

M/nS

MASTER/nS

LEDRUN

LEDALM

nBATT

nLOS_BB

nSLFFAN_ALM

nFAN_ALM

DC_ALM

AC_ALM

nLOS_BB

nSLFFAN_ALM

nFAN_ALM

DC_ALM

AC_ALM

RING_SYNC

SHWD0_P/N

SHWD1_P/N

SHWD2_P/N

SHWU0_P/N

SHWU1_P/N

SHWU2_P/N

SHWD1_P/N

SHWD2_P/N

SHWU0_P/N

SHWU1_P/N

SHWU2_P/N

S_RINGSYNC_P/N

S_nRESET_P/N

SHW_CLK_P/N

SHW_nFH_P/N

CT_NETREF_P/N

CCLINK_P/N

nLOS_P/N

S_nRESET_P/N

SHW_CLK_P/N

SHW_nFH_P/N

CT_NETREF_P/N

CCLINK_P/N

nLOS_P/N

CPU_STATUS0_P/N

CPU_STATUS1_P/N

CPU_STATUS1_P/N

nSLF_PRS

S_ESLFID[1:0]

S_ESLFID[1:0]

SHWD[2:0]

IC113

X102

nC

S

S

4

L

_

nW

E

L

_

nR

D

D

L_

n

n

L

B

/U

B

L

_

A

D

D

[16:

1]

1]

L

_

D

A

T

A

[15:

0]

0]

nC

S

S

0

L_

n

n

W

E

0

L

_

nR

D

D

L_

n

n

L

B

/U

B

L

_

A

D

D

[16:

1]

1]

L

_

D

A

T

A

[15:

0]

0]

A

D

D

[22:

17]

17]

L

_

DAT

A[

1

1

5

:0

]

L

_

nR

D

D

L_

n

n

W

E

0

L

_

A

D

D

[16:

1]

1]

L_

n

n

W

E

1

L

_

nW

E

L_

R

R

/n

W

L_DATA[15:0]

L_ADD[15:0]

nCS4

nCS5

L_ADD[15:0]

nCS4

nCS5

nRD

L_nWE[1:0]

nBS

nWAIT_ASIC

CLK_16M

nC

S

S

_

C

C

L

IN

K

L

_

nR

D

D

nW

R

_

C

C

L

IN

K

L

_

A

D

D

[5:

1]

L

_

DAT

A[

1

1

5

:0

]

nI

R

Q

_C

C

C

L

IN

K

CCLINK_RXD

CCLINK_TXD

CCLINK_TXEN

CCLINK_TXD

CCLINK_TXEN

nD

T

T

A

C

K

CLK_20M

C

L

K

_40

M

X401

nD

S

S

L_

R

R

/n

W

nC

S

S

_

C

T

S

W

L

_

A

D

D

[14:

1]

1]

L

_

D

A

T

A

[15:

0]

0]

CT_C8,CT_FRAME

CT_D[7:0]

CT_D[7:0]

D

A

T

A

[15:

0]

0]

nR

D

D

nW

E

0

A

D

D

[16:

1]

1]

nW

E

1

RD/

n

W

R

CTSW_EN

IC304

IC303

IC301,302

RING_SYNC

ESLFID[1:0]

BM_nRESET

ESLFID[1:0]

BM_nRESET

S_ESLFID[1:0]

S_RING_SYNC

S_nRESET

nLOS

nCS_CCLINK

L_nWE

nCS_CTSW

L_nRD

L_R/nW

nDTACK

L_nWE

nCS_CTSW

L_nRD

L_R/nW

nDTACK

nWAIT_NEXUS

nCS5

nWR_CCLINK

nDS

nRDY

nDS

nRDY

nIRQ_ASIC

nIRQ_CCLINK

nDC_ALM

nIRQ_CCLINK

nDC_ALM

SS IC

IC202

D

A

T

A

[31:

0]

0]

A

D

D

[15:

2]

2]

nC

S

S

2

nR

A

A

S

, nC

A

S

RD/

n

W

R

D

Q

M

[3:

0]

CLKIO

D

A

T

A

[31:

0]

0]

A

D

D

[16:

1]

1]

nC

S

S

2

nR

A

A

S

, nC

A

S

RD/

n

W

R

D

Q

M

[3:

0]

nSLF_PRS

LV

D

D

S

DC/DC

REG

2.5V

IC701

IC704

IC703

IC203

RINGER

HALT

POWTYPE

MASTER/nS

M/nS

LED_ALM

LED_RUN

HALT

POWTYPE

MASTER/nS

M/nS

LED_ALM

LED_RUN

To CPU

nBATT

nLOS_BB

nSLFFAN_ALM

nFAN_ALM

DC_ALM

AC_ALM

nLOS_BB

nSLFFAN_ALM

nFAN_ALM

DC_ALM

AC_ALM

Li-BAT

3.3VB

Sheet 6

Sheet 4

Sheet 1

Sheet 3

Sheet 7

REG

15V

Sheet 2

Sheet 5

KX-TDA620BX BUS-S CARD BLOCK DIAGRAM

40

CN601

pin

Local_BUS

29

KX-

TDA620BX

8.1.4. Circuit Description

ASIC Block (Sheet1)

This block is capable of controlling the EC bus, which is a way of accessing the option card.

It also realizes TSW function by controlling the CT bus (8.192MHz HW clock; 8 highways, 128 timeslots). At the same time, it

is capable of controlling conference call with a range of 3 parties of 10 to 10 parties of 3.

It also generates single or DTMF tones in any highway or time slot.

It also realizes TSW function by controlling the CT bus (8.192MHz HW clock; 8 highways, 128 timeslots). At the same time, it

is capable of controlling conference call with a range of 3 parties of 10 to 10 parties of 3.

It also generates single or DTMF tones in any highway or time slot.

CPU Block (Sheet2)

The CPU block consists of IC200 (CPU), X201 (Clocking clock), IC202 (spread clock).

IC200 is the CPU that controls the expansion shelf, X201 is the clock that the CPU uses internally, and IC202 is a driver to

transmit the CPU operating clock from the ASIC block.

IC200 is the CPU that controls the expansion shelf, X201 is the clock that the CPU uses internally, and IC202 is a driver to

transmit the CPU operating clock from the ASIC block.

Memory Block (Sheet3)

This block consists of IC301, 302 (SDRAM), IC303 (flash ROM), IC304 (SRAM), as well as the following to separate the main

and local buses: IC305, IC306, IC307, IC308, IC309, IC310, IC311, IC313 (Logic IC).

In flash memory are stored the boot and operating programs.

SDRAM is the region in which the operating program is actually expanded and run.

SRAM is the region in which an error log is temporarily stored during operation.

Access to ICs and all RAM aside from SDRAM is done through the separated local bus.

and local buses: IC305, IC306, IC307, IC308, IC309, IC310, IC311, IC313 (Logic IC).

In flash memory are stored the boot and operating programs.

SDRAM is the region in which the operating program is actually expanded and run.

SRAM is the region in which an error log is temporarily stored during operation.

Access to ICs and all RAM aside from SDRAM is done through the separated local bus.

CircLink Block (Sheet4)

This block consists of IC401 (Controller), X401 (source clock 40MHz), and IC410.

Through message communication among controllers within the BUS-M card mounted in the basic shelf, packet communication

with EMPR of the basic shelf is made possible.

LVDS is used for actual communication.

IC402 serves an auxiliary role when the CPU accesses other ICs.

Through message communication among controllers within the BUS-M card mounted in the basic shelf, packet communication

with EMPR of the basic shelf is made possible.

LVDS is used for actual communication.

IC402 serves an auxiliary role when the CPU accesses other ICs.

System TSW Block (Sheet5)

This block consists of IC501 (TSW).

It is capable of exchanging voice data between the CT bus (1024ch) within the unit and the voice bus (384ch) of the basic shelf.

It is capable of exchanging voice data between the CT bus (1024ch) within the unit and the voice bus (384ch) of the basic shelf.

Bus Cable Connection Block (Sheet6)

This block consists of IC601, 602, 603, 604, 605 (LVDS) and CN601 (BUS Cable Connector).

Each control signal is converted to a differential signal through LVDS device and sent to the bus cable.

Each control signal is converted to a differential signal through LVDS device and sent to the bus cable.

On board Power supply (Sheet7)

The power supply block consists of IC701 (DC/DC converter), Q712 (transistor), IC703 (regulator), and IC704 (regulator).

IC701 and Q712 are circuits to generate 3.3V used in nearly all of the ICs.

IC703 generates 1.5V used in the CPU (IC200). IC704 generates 2.5V used in IC402.

IC704 generates 2.5V used in IC402.

IC701 and Q712 are circuits to generate 3.3V used in nearly all of the ICs.

IC703 generates 1.5V used in the CPU (IC200). IC704 generates 2.5V used in IC402.

IC704 generates 2.5V used in IC402.

30

KX-TDA620BX

Explanation of signals used in the block diagrams

Signal Name

Contents

EC_AD[15:0]

Address of EC Synchronous bus, Data Bus.

EC_CBE[1:0]

EC Bus command /Byte enable: The indicator drives as bus command in the address phase and as byte

enable in the data phase.

enable in the data phase.

EC_nCDET

EC line card detection signal: Asynchronous interrupting signal

EC_CLK

Clock of EC Synchronous Bus (8MHz) All the EC Bus signal except nRESET/EC_INT operates in sync

with signal.

with signal.

EC_FARME

EC Cycle frame signal: This indicates the drive by initiator and the execution of EC bus cycle.

EC_nINT

EC Interrupt signal: This is asserted by optional card.

EC_PAR

Parity bit of EC synchronous Bus: Drive by applying even parity to AD[15:0] and CDE[1:0].

EC_nPERR

EC parity error: Flag indicating error status by parity flag.

EC_nRST

EC Reset signal: shelf reset signal

EC_nSTOP

EC Bus Stop signal: This is asserted, when target requests transaction halt to initiator.

EC_nTRDY

EC Target ready signal: This indicates the drive by target and the possible data transfer.

CT_C8

Clock 8.192MHz clock outputted from DPLL

CT_FRAME

Frame signal: 8kHz frame signal outputted from DPLL

CT_D [7:0]

CT Data Bus: Two-way serial data bus to which the drive from any card is possible in the system.

RINGER

Ringer signal :Output square-wave of 20/25Hz as source signal of ringer.

HALT

This alarms the occurrence of the decline DC voltage to line card.Operation halt signal sent to the option

card (when the DC alarm has gone off).

card (when the DC alarm has gone off).

POWTYPE

Notification signal of the power supply type M Power Supply attached: POWTYPE[1:0]= [H, H,] L Power

Supply attached: POWTYPE[1:0]= [H, L]

Supply attached: POWTYPE[1:0]= [H, L]

LED_ALM

Control signal for the extension shelf LED_ALM H: Turn ON

LED_RUN

Control signal for the extension shelf LED_RUN H: Turn ON

nLOS_BB

Loss of line signal

nSLFFAN_ALM

Alarm signal of the casing fan

nFAN_ALM

Fan alarm signal :It goes Low at the error of the L Power Supply’s Fan.It goes High when the Fan is

normal and Power supply M, which does not carry the FAN are used.

normal and Power supply M, which does not carry the FAN are used.

DC_ALM

DC alarm signal :Indicates the declined DC voltage

AC_ALM

AC alarm signal: This indicates AC voltage cutoff.

RING_SYNC

Trigger signal of Ringer signal generation timing to each internal line card.

CLK_16M

Clock 16.386MHz ASIC and CPU operation Clock.

CTSW_EN

CTSW output enable signal

SHW_CLK

Voice system clock signal from the basic shelf (8MHz)

SHW_nFH

Voice system frame signal from the basic shelf (8kHz)

nIRQ_ASIC

Interrupt signal from the ASIC

nIRQ_CCLINK

Interrupt signal from CCLINK

DATA[31:0]

CPU Data Bus

ADD[16:1]

CPU Address Bus

nCS0

Flash ROM select

nCS2

SDRAM Chip select

nCS4

SRAM Chip select

nCS5

ASIC Chip select

nCS_CCLINK

CCLINK Chip select

nCS_CTSW

CTSW Chip select

nRAS

Row Address strobe: for SDRAM

nCAS

Column address strobe: for SDRAM

RD/nWR

Read / Write Signal for SDRAM

DQM[3:0]

Data input output Mask for SDRAM

L_DATA[15:0]

Local data bus

L_ADD[16:1]

Local address bus

L_nRD

Local read signal

L_nWE0, 1

Local byte write signal

L_nWE

Local write signal

L_R/nW

Local read/write signal

nWR_CCLINK

CCLINK write signal

nDS

CCLINK data strobe signal

nRDY

CPU ready signal

ESLFID[1:0]

Extension shelf ID notification signal

BM_nRESET

Extension shelf reset signal

nDTACK

nDTACK signal from CTSW

nWAIT_NEXUS

Access wait signal from the ASIC

S_RING_SYNC

Ringer synchronous input signal from the basic shelf

S_nRESET

Reset input signal from the basic shelf

CPU_STATUS[1:0]

BUS-S status display

CLK_40M

CircLink operating clock (40.0MHz)

CCLINK_TXD

CircLink send data

31

KX-TDA620BX

CCLINK_RXD

CircLink receive data

CCLINK_TXEN

CircLink send data valid

CLK_20M

CTSW operating clock (20.0MHz)

SHWU[2:0]

Intersystem highway upstream data

SHWD[2:0]

Intersystem highway downstream data

SHWU[2:0]_P/N

Intersystem highway upstream differential signal

SHWD[2:0]_P/N

Intersystem highway downstream differential signal

SHW_CLK_P/N

Intersystem clock differential signal

SHW_nFH_P/N

Intersystem frame timing differential signal

S_RINGSYNC_P/N

Ringer synchronous differential signal

S_nRESET_P/N

Extension shelf reset differential signal

CT_NETREF_P/N

Differential signal of the extension shelf synchronous reference signal

CCLINK_P/N

Circlink communication differential signal

nLOS_P/N

Differential signal for loss of line indicator

CPU_STATUS[1:0]_P/N

Differential signal for BUS-S status

nSLF_PRS

Extension shelf connection display signal

S_ESLFID[1:0]

Extension shelf ID notification signal

+15V

Power supply

3.3V

IC power supply on the card

3.3VB

Backup power supply (3.3V)

2.5V

Power supply for FPGA (IC402)

1.5V

Power supply for CPU (IC200)

9 BACK BOARD CIRCUIT OPERATION

The back board (BB) connects signals between optional card in KX-TDA620. It also supplies power from the power supply unit

to the cards.

Connectors Explanation

(1) Power Supply Unit Connector: CN100

(2) Free Slot Connectors: CN101 to CN111

(3) BUS-S Card Connector: CN112

(4) FAN Connector: CN114

(5) LED Connector: CN115

(6)Voltage drop Resistor for Fan control: R400

to the cards.

Connectors Explanation

(1) Power Supply Unit Connector: CN100

(2) Free Slot Connectors: CN101 to CN111

(3) BUS-S Card Connector: CN112

(4) FAN Connector: CN114

(5) LED Connector: CN115

(6)Voltage drop Resistor for Fan control: R400

32

KX-TDA620BX

Click on the first or last page to see other KX-TDA620BX service manuals if exist.