Panasonic KX-NS5171XSX / KX-NS5172XSX Service Manual ▷ View online

41

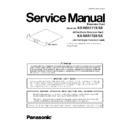

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

D12

nSLCRST

O

SLIC reset

D13

VCCD_PLL

-

VCC

D14

D3_T

I/O

TACKER bus data

D15

D2_T

I/O

TACKER bus data

D16

D1_T

I/O

TACKER bus data

E1

NC

-

no connect

E2

GND

-

GND

E3

VCCIO

-

VCC

E4

GND

-

GND

E5

TEST6

-

test pad

E6

NC

-

no connect

E7

A2_L

O

local bus address

E8

NC

-

no connect

E9

NC

-

no connect

E10

A13_L

O

local bus address

E11

TEST7

test pad

E12

GNDA

-

GND

E13

GND

-

GND

E14

VCCIO

-

VCC

E15

NC

-

no connect

E16

NC

-

no connect

F1

nSBACK_M

I

local bus acknowledge from sub bus arbiter

F2

D1_L

I/O

local bus data

F3

D6_L

I/O

local bus data

F4

nSTATUS

I

multimode configuration status

F5

NC

-

no connect

F6

NC

-

no connect

F7

NC

-

no connect

F8

NC

-

no connect

F9

NC

-

no connect

F10

NC

-

no connect

F11

NC

-

no connect

F12

VCCA

-

VCC

F13

D7_T

I/O

TACKER bus data

F14

D6_T

I/O

TACKER bus data

F15

D5_T

I/O

TACKER bus data

F16

D4_T

I/O

TACKER bus data

G1

nSBACK_S

O

local bus acknowledge to slave controller

G2

HWCLK

O

High Way clock(4M)

G3

VCCIO

-

VCC

G4

GND

-

GND

G5

NC

-

no connect

G6

VCCINT

-

VCC

G7

VCCINT

-

VCC

G8

VCCINT

-

VCC

G9

VCCINT

-

VCC

G10

VCCINT

-

VCC

G11

NC

-

no connect

G12

MSEL2

I

configuration mode select

G13

GND

-

GND

G14

VCCIO

-

VCC

G15

A1_T

I/O

TACKER bus address

G16

A0_T

I/O

TACKER bus address

H1

DCLK

O

SPI flash ROM clock

H2

DATA0

I

SPI flash ROM data

H3

TCK

I

JTAG TCK

H4

TDI

I

JTAG TDI

H5

nCONFIG

I

configuration indicator

H6

VCCINT

-

VCC

H7

GND

-

GND

H8

GND

-

GND

H9

GND

-

GND

H10

GND

-

GND

H11

VCCINT

-

VCC

H12

MSEL1

I

configuration mode select

H13

MSEL0

I

configuration mode select

H14

CONF_DONE

I

multiconfiguration DONE signal

Pin No.

Pin Name

I/O

Function

42

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

H15

GND

-

GND

H16

GND

-

GND

J1

IRQ0

I

local IRQ

J2

IRQ1

I

local IRQ

J3

nCE

I

multimode configuration chip select

J4

TDO

O

JTAG TDO

J5

TMS

I

JTAG TMS

J6

NC

-

no connect

J7

GND

-

GND

J8

GND

-

GND

J9

GND

-

GND

J10

GND

-

GND

J11

NC

-

no connect

J12

NC

-

no connect

J13

A5_T

I/O

TACKER bus address

J14

A4_T

I/O

TACKER bus address

J15

A3_T

I/O

TACKER bus address

J16

A2_T

I/O

TACKER bus address

K1

IRQ2

I

local IRQ

K2

IRQ3

I

local IRQ

K3

VCCIO

-

VCC

K4

GND

-

GND

K5

TEST5

-

test pad

K6

NC

-

no connect

K7

VCCINT

-

VCC

K8

NC

-

no connect

K9

NC

-

no connect

K10

NC

-

no connect

K11

NC

-

no connect

K12

TEST0

test pad

K13

GND

-

GND

K14

VCCIO

-

VCC

K15

A7_T

I/O

TACKER bus address

K16

A6_T

I/O

TACKER bus address

L1

IRQ6

I

local IRQ

L2

IRQ7

I

local IRQ

L3

CID3

I

CARD ID

L4

CP0

I

High Way select

L5

VCCA

-

VCC

L6

NC

-

no connect

L7

NC

-

no connect

L8

NC

-

no connect

L9

NC

-

no connect

L10

NC

-

no connect

L11

NC

-

no connect

L12

NC

-

no connect

L13

A11_T

I/O

TACKER bus address

L14

A10_T

I/O

TACKER bus address

L15

A9_T

I/O

TACKER bus address

L16

A8_T

I/O

TACKER bus address

M1

HWCLK_M

I

High Way clock input(4M)

M2

NC

-

no connect

M3

VCCIO

-

VCC

M4

GND

-

GND

M5

GNDA

-

GND

M6

TEST4

-

test pad

M7

TEST3

-

test pad

M8

NC

-

no connect

M9

NC

-

no connect

M10

TEST2

test pad

M11

NC

-

no connect

M12

TEST1

test pad

M13

GND

-

GND

M14

VCCIO

-

VCC

M15

NC

-

no connect

M16

CLK

I

system clock(25MHz)

N1

CID0

I

CARD ID

Pin No.

Pin Name

I/O

Function

43

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

N2

CID1

I

CARD ID

N3

CID2

I

CARD ID

N4

VCCD_PLL

-

VCC

N5

CP2

I

High Way select

N6

CP4

I

High Way select

N7

GND

-

GND

N8

DELAY1

I

attainment signal from connected terminal

N9

CP7

I

High Way select

N10

GND

-

GND

N11

nCS20

O

local bus SRAM chip select

N12

nCS0

O

local bus FROM chip select

N13

nCS3

O

local bus ASIC chip select

N14

nCS1

O

local bus ASIC chip select

N15

nCS_DMA

I

SRAM chip select at DMA

N16

A12_T

I/O

TACKER bus address

P1

HWFH_M

I

frame sync from TSW

P2

LUHW_M

O

UP High Way to TSW

P3

CP1

I

High Way select

P4

VCCIO

-

VCC

P5

GND

-

GND

P6

CP3

I

High Way select

P7

VCCIO

-

VCC

P8

DELAY0

I

attainment signal from connected terminal

P9

CP6

I

High Way select

P10

VCCIO

-

VCC

P11

nCS21

O

local bus SRAM chip select

P12

GND

-

GND

P13

VCCIO

-

VCC

P14

nBREQ

I

local bus request

P15

nBACK

O

local bus acknowledge

P16

nWAIT

I

local bus wait

R1

LDHW_M

I

DOWN High Way from TSW

R2

GND

-

GND

R3

nWR_M

I

CPU bus write

R4

nWAIT_M

O

CPU bus wait

R5

D6_M

I/O

CPU bus data

R6

D4_M

I/O

CPU bus data

R7

D2_M

I/O

CPU bus data

R8

CP5

I

High Way select

R9

LUHW0

I

LOCAL UP High Way

R10

D0_M

I/O

CPU bus data

R11

A8_M

I

CPU bus address

R12

A6_M

I

CPU bus address

R13

A4_M

I

CPU bus address

R14

A2_M

I

CPU bus address

R15

GND

-

GND

R16

A0_M

I

CPU bus address

T1

VCCIO

-

VCC

T2

nINT_M

O

IRQ to CPU

T3

nCS_M

I

CPU bus chip select

T4

nRD_M

I

CPU bus read

T5

D7_M

I/O

CPU bus data

T6

D5_M

I/O

CPU bus data

T7

D3_M

I/O

CPU bus data

T8

LDHW

O

LOCAL DOWN High Way

T9

LUHW1

I

LOCAL UP High Way

T10

D1_M

I/O

CPU bus data

T11

A9_M

I

CPU bus address

T12

A7_M

I

CPU bus address

T13

A5_M

I

CPU bus address

T14

A3_M

I

CPU bus address

T15

A1_M

I

CPU bus address

T16

VCCIO

-

VCC

Pin No.

Pin Name

I/O

Function

44

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

13.2. Cabinet and Electrical Parts Location

13.2.1.

KX-NS5171

1

The positioning boss of BRACKET

needs to fit into the hole of PCB.

Click on the first or last page to see other KX-NS5171XSX / KX-NS5172XSX service manuals if exist.