Panasonic KX-NS5171XSX / KX-NS5172XSX Service Manual ▷ View online

5

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

3 Specifications

4 General/Introduction

4.1.

General Description

This card, which is used in the free slot of KX-NS300/500 series system, can randomly connect sixteen of DPT.

Functional Block

Functional contents

Extension Interface

Number of Ports

16 ports

PT Interface

+40V Over current protective function, Voltage switching function Inter-

DPT communications

2B+D (144kbps) 2W Ping-pong transmission system (512kbps)

Dch-control HDLC embeds eight channels in ASIC

Surge protective function

DPT communications

2B+D (144kbps) 2W Ping-pong transmission system (512kbps)

Dch-control HDLC embeds eight channels in ASIC

Surge protective function

Control Block

CPU

NiosII included in DLC FPGA

DLC FPGA

Dual-port memory between CPU board and NiosII CPU

Flash ROM

1Mbyte

SRAM

256kbyte

ASIC

Digital PLL function

Local bus interface function

Time switch function, Gain controlling function, DPRAM function

Private telephone controlling interface function

Parallel IO function

Local bus interface function

Time switch function, Gain controlling function, DPRAM function

Private telephone controlling interface function

Parallel IO function

External Interface

RJ45: 4 ports

6

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

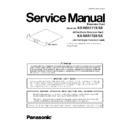

5 Technical Descriptions

5.1.

Block Diagram

DLC16

Block

Diagram

DLC

Dr

iv

er

&

Rec

ei

ve

r

Se

rg

e

EMC

DTB

0

Pul

se

Tr

an

s

Po

w

e

r SE

L

Ov

er

lo

ad

Pr

ot

ec

tion

PT

_P

OW

0

DTA

0

P

T

_C

UR0

Port #2

(Sam

e

as

Port #1)

D1A

D2A

Por

t #1

D1

B

D2B

DR

0

+40V

+3

.3

V

VR

EF

VREF

+

Port #3

(Sam

e

as

Port #1)

D1C

D2C

Port #4

(Sam

e

as

Port #1)

D1D

D2

D

Port #5

(Sam

e

as

Port #1)

D1E

D2

E

Port #6

(Sam

e

as

Port #1)

D1

F

D2F

Port #7

(Sam

e

as

Port #1)

D1

G

D2G

Port #8

(Sam

e

as

Port #1)

D1H

D2H

Port #9

(Sam

e

as

Port #1)

D2

I

Por

t #10

(Sam

e as

Por

t #

1

)

D1J

D2J

Por

t #11

(Sam

e as

Por

t #

1

)

D1K

D2K

Por

t #12

(Sam

e as

Por

t #

1

)

D1L

D2L

Por

t #13

(Sam

e as

Por

t #

1

)

D2

M

Por

t #14

(Sam

e as

Por

t #

1

)

D1N

D2N

Por

t #15

(Sam

e as

Por

t #

1

)

D1O

D2O

Por

t #16

(Sam

e as

Por

t #

1

)

D1P

D2P

PORT9

12

PO

RT

1316

TAC

KER

ASIC

(M

as

te

r)

NI

OS

P4[

0]

P5[

0]

RX

[0

]

TXA[

0

]

TXB[

0

]

FL

ASH

ROM

8M

B

it

SR

AM

1M

B

it

A_

L

[1

9

:0

]

A[

1

9

:1

]

A[

1

6

:0

]

A

[12:0]

A

[12:0]

D_L[15:0]

D[15:

0]

D[7:0]

D[7:0]

D[7:0

]

nW

R

_

L

nRD_L

nW

R

nRD

nW

R

nRD

nW

R

nRD

nW

R

nR

D

nCS

_D

M

A

nCS

_D

M

A

nC

S

_

D

M

A

nCS

_D

M

A

nC

S

nC

S

_

D

M

A

SR

AM

1M

B

it

A[

1

6

:0

]

D[7:0]

nW

R

nRD

nC

S

nCS

0

nCS

1

nCS

3

nC

S

I

nCS

I

nCS

0

nCS

1

nCS

20

nCS

21

nC

S

3

nCS

20

nCS

21

n

R

ES

ET

0

_

M

nR

E

S

E

T

n

R

ES

ET

n

R

ES

ET

0

_

M

XT

AL

25M

H

z

nW

A

IT

nW

A

IT

nW

A

IT

TAC

KER

ASIC

(Slav

e)

SBR

EQ

SBA

CK

BAC

K

BREQ

BAC

K

BREQ

BAC

K

BREQ

AL

E

AL

E

AL

E

XT

AL

16.384

MH

z

nIR

Q1

nIR

Q

PL

L

C

L

K

ECCL

K

P

LLCLK

ECCL

K

P2

3

P2

3

DEL

A

Y

0

DELA

Y1

DELA

Y0

DELA

Y1

CP[7

:0]

CP[7

:0]

CT

_D[7:0]

CT

_D[7:0]

LDH

W

LUH

W

0

LU

H

W

0

LDH

W

0

LUH

W

0

LDH

W

0

CONF

IG

HW

C

L

K

2

_

M

HW

C

L

K

_

M

HW

F

H

2

_

M

HW

F

H

_

M

LD

H

W

2_M

LU

H

W

2_M

LD

H

W

_M

LU

H

W

_M

A

_

M

[9:0]

D_M

[7:0]

nW

A

IT

_

M

nW

A

IT

_

M

D_M

[7:0]

A_

M

[9

:0

]

RD_

M

RD_

M

WR

_

M

WR

_

M

CS_

M

CS0

_

M

CS1

_

M

INT

_

M

INT

0_M

INT

1_M

IRQ2

BEL

L

_

S

Y

N

C

IRQ0

HAL

T

IRQ3

ACAL

M

R

E

S

E

T

1_M

HW

C

L

K

3

_

M

HW

_

F

H

3

_

M

TO

und

er

boar

d

TO

upp

er

boar

d

VREF

+

nC

S

n

R

ES

ET

Har

d

Revi

si

on

P0

[7

:0

]

+4

0

V

+3

.3

V

n

R

ES

ET

0

_

M

n

R

ES

ET

0

_

M

SH

W

_

F

H

SH

W

_

CL

K

SH

W

_

F

H

SH

W

_

CL

K

HW

C

L

K

HW

C

L

K

HW

F

H

HW

F

H

LUH

W

0

LUH

W

1

LUH

W

0

LDH

W

LDH

W

LDH

W

CAR

D

ID

CLK

CA

R

D

ID[3:0](

I/

O)

TM

S

TC

K

TD

I

TD

O

Debugging

Part

JT

A

G

Port

PTC

TR

VREF

-

VREF

-

VREF

+

VREF

-

VREF

+

VREF

-

VREF

+

VREF

-

D1

I

D1

M

Se

ri

a

l

RO

M

for Confi

g

4M

bi

t

DAT

A

DCL

K

CSO

DAT

A

DCLK

CS

ASDO

ASDI

DLC

FPGA

EP4

C

E

1

0

LUH

W

1

LUH

W

1

A_

T

[1

2

:0

]

D

_

T

[7:0]

nW

R

_

T

nRD

_T

DC/

DC

+2

.5

V

+1

.2

V

A_

T

[1

2

:0

]

A_

T

[1

2

:0

]

A

_

T

[12:0]

D_T

[7:0]

D_T

[7:0]

D_T

[7:0]

nW

R

_

T

nW

R

_

T

nW

R

_

T

nR

D_T

nRD_T

nRD_T

nIRQ_T

nIRQ

nIRQ_T

nIRQ_T

HW

C

L

K

HW

F

H

HW

C

L

K

HW

F

H

SBA

CK_

M

SBR

EQ

SBA

CK_

S

A_

L

[1

9

:1

]

A

_

L[16:0]

A_

L

[1

6

:0

]

D

_

L[15:0]

D

_

L[7:0]

D_L[7:0]

nW

R

_

L

nW

R

_

L

nW

R

_

L

nRD_L

nRD_L

nRD_L

nW

R

_

L

nRD_L

A_

L

[1

9

:0

]

D_L[15:0]

7

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

5.2.

Circuit Operation

5.2.1.

Control-System Circuit

5.2.1.1.

DLC FPGA

Function

Specifications

FPGA Internal Processer

NiosII CPU

Interface

CPU Board I/F

Bus Timing

TI CortexA8 CPU Bus Interface

Data Bus

8bit

Address Bus

11bit

Interrupt Control

External Interrupt

Up to 2

Internal Interrupt

Up to 3

SLIC Control

Number of SLIC

Up to 2

DPT Control

Delay Measurement

16bit with data latch

SLC

MPR_BUS

DLC_FPGA

SPI

CPU

CS_DLY

FH

P23

INT

SLIC_INT

DPRAM

INT_CON

8

KX-NS5171X/KX-NS5171SX/KX-NS5172X/KX-NS5172SX

5.2.1.2.

TACKER ASIC

• Local TSW

Exchanges the time slots between CT bus (1024ch) and local highway (64ch).

• Local highway interface

Accommodates 2.048, 4.096, and 8.192MHz highways (Up to 64 time slots).

• Local gain control

Controls the gain of the local highway up-and-down 64ch in 1db step arbitrarily.

• PT interface

Allows APT/DPT interface to be selected for each port.

• GPIO interface

Parallel interface that is arbitrarily programmable bidirectionally.

Local

Bus

Local

TSW

Host

L

L

ocal-

-

bus I/F

DPLL

JTAG

GAIN

I

l Hi h

I

l b

APITS

controller

HDLC

8ch

FIFO /

/

DPRAM

DPITS

controller

Highway

Local

H

H

ighway I/F

PT-I/F

PITS

GPIO-i/f

GPIO

CODEC

controller

RT_SND

Click on the first or last page to see other KX-NS5171XSX / KX-NS5172XSX service manuals if exist.