Panasonic KX-NCP1290CJ (serv.man2) Service Manual ▷ View online

5

KX-NCP1290CJ

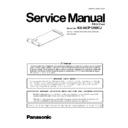

3 Technical Descriptions

3.1.

Block Diagram

20MH

z

Line Interface Block

CLKOUT(4.096MHz or

2.048MHz)

DSTi

DSTo

nF0b

nC4b

D[7:0]

A[4:0]

nIRQ

LOS

nRxMF

nTxMF

nRES

E1.5o/C1.5o

TX+

TX-

RX+

RX

-

DPLL IC302

f=12.288MHz

(CPU)

IC1

nIRQ1

nRES

nBREQ

nBACK

nWAIT

nIRQ0

PB[0]

nIRQ2

nIRQ3

nIRQ4

nIRQ5

PB[3]

RXD

TXD

PA[11]

PB[10]

Decode

r

(ASIC)

IC2

EC_CLK

EC_AD[15:0

]

EC_BE[1:0]

EC_FRAME

EC_TRDY

EC_STOP

EC_INT

EC_PART

EC_PERR

EC_nRST

EC_IDSEL

EC_DET

LDHW[1:0]

LUHW[1:0]

HW_FH

HW_CLK0

HW_CLK1

L_NETREF

SHW_FH

CT_NETREF

nCT_FRAME_

A

CT_CLK_A

CT_D[7:0]

TCK

TDI

TDO

TMS

TRST

P2[7]

nRESE

T

PLLCL

K

P0[7:0]

P1[3:0]

P2[0]

P2[1]

P2[6]

P3[0]

P3[4]

nCS_DMA

LD[7:0]

LA[12:0]

nRD

,nWR

nCSI

nCS[0]

nIRQ[1]

nIRQ[0]

P2[3]

P2[2]

nLRST

nBREQ

nBACK

nWAIT

+3.3V

J

u

mpe

r

Status

Indecation

x

5

Local

Reset

JTAG

RJ45

(C

O/EXT)

DHW0/DHW1(2.048Mbps)

UHW0/UHW1(2.048Mbps)

CLKOUT(4.096MHz or 2.048MHz)

nSHW_FH(8kHz)

nINT_ISD

DHW0

UHW0

nHW_FH(8kHz)

HW_CLK0(4M)

D7-0

A4-6

nRD,nWR

nCS_ISDN

nINT_ISDN

LOS

nRxMF

nTxMF

ISDN_RST

+3.3V

nREST

20MH

z

+3.3V

Flash

4Mbit

(256k x 16)

SRAM

4Mbit

(256k x 16)

+3.3

V

+

3.3V

+

3.3V

D15-0

A19-0

nRD

nWR

nLBS

nCS0

nCS1

nCS2

nCS3

nCS6

12.288M

z

nINT_ISDN

nINT_DSP

LOS

nRxMF

RYnBY

nCS_ISDN

nCS_DSP

+3.3

v

ISDN_RST

DSP_nRST

nTxMF

LOOPB

HRDY

nCS_DMA

D7-0

AIZ-0

nRD_nWR

nCS1

nINT_ISDN

nCS[0]_S

+3.3V

nRST

nHALT

EC_bus

28

H100 bus

11

CT

_

LO

OSC

16.384MHz

nRESET

RYnBY

nRESE

T

D15-0

A18-1

nWR,nRD

nCS0

D15-0

A18-1

nWR,nRD,nLBS,A0

nCS2

A10

nCS[0]_S

+15V

(PRI-

IC

)

IC301

Serge

EMC

Serge

EMC

Termination

Termination

Transforme

r

Transforme

r

Power

Thermisto

r

DC/DC

Converte

r

KX-NCP1290CJ BLOCK DIAGRAM

IC3

IC5

6

KX-NCP1290CJ

3.2.

Hardware Functional Specification

3.2.1.

CPU Peripheral Function

The CPU (IC1) is a single chip microcomputer of RISC architecture.

This item describes a memory interface (program & work) and peripheral functions.

This item describes a memory interface (program & work) and peripheral functions.

3.2.1.1.

Memory (Program & Work)

Shows a list of the memory (program & work).

List of the memory (program & work)

3.2.1.2.

Chip Select Logic

The CPU (IC1) has a chip select module as an internal peripheral and 8 chip select terminals are prepared outside. The area of

4Mbyte is assigned to a chip select terminal. (When DRAM is used, there is an exception partly, however it is not mentioned

here.)

4Mbyte is assigned to a chip select terminal. (When DRAM is used, there is an exception partly, however it is not mentioned

here.)

Table of Chip Select Terminals

Table of Chip Select Port allocation

Part Name

Size

Purpose

Remarks

4M_Flash

4Mbit (256K x 16)

Program Area

Flash memory is employed for the software downloading by on-board.

4M_SRAM

4Mbit (256K x 16)

Work Area

Terminals

Function used

Wait Function

(Numeral is no. of

clocks.)

Remarks

CS Terminals

Individual Output

(1)

Individual Output

(2)

nCS0 (area 0)

-

-

nCS0

1+Programable

or

1+Programable+WAIT

Terminals

Terminals

Used for Flash memory CS.

nCS1 (area 1)

nCASH (DRAM)

-

nCS1

Read 1/Write 2 or

2+WAIT Terminals

2+WAIT Terminals

Used for IC2 (ASIC) CS

nCS2 (area 2)

-

-

nCS2

1+Programable

or

1+Programable+WAIT

Terminals

Terminals

Used for SRAM CS. Work Area

nCS3 (area 3)

nCASL (DRAM)

-

nCS3

Read 1/Write 2 or

2+WAIT Terminals

2+WAIT Terminals

CS Reserve

nCS4 (area 4)

PA0 (I/O)

TIOCA0 (Timer)

nCS4

Read 1/Write 2 or

2+WAIT Terminals

2+WAIT Terminals

CS Reserve

nCS5 (area 5)

PA1 (I/O)

nRAS (DRAM)

nCS5

Read 1/Write 2 or

2+WAIT Terminals

2+WAIT Terminals

CS Reserve

nCS6 (area 6)

PA2 (I/O)

TIOCB0 (Timer)

nCS6

1+Programable

or

1+Programable+WAIT

Terminals

Terminals

Used for peripheral LSI CS.

nCS7 (area 7)

PA3 (I/O)

nWAIT

nWAIT

Read 1/Write 2 or

2+WAIT Terminals

2+WAIT Terminals

Used for Input Wait Terminals.

Chip Select

Address

DeviceBit Wide

Assignment

Device

Bus Cycle

Remarks

nCS0

0000000h

l

0FFFFFFh

l

0FFFFFFh

16bit

4M_Flash

IC5

2 Clock (1+Long Wait1)

Port allocation of word by static bus siz-

ingBus cycle has same setting as Area 2

(nCS2).

ingBus cycle has same setting as Area 2

(nCS2).

nCS1

1000000h

l

1FFFFFFh

l

1FFFFFFh

8bit

ASIC

IC2

2+WAIT Terminals

Port allocation of byte by static bus sizing.

nCS2

A000000h

l

AFFFFFFh

l

AFFFFFFh

16bit

4M_SRAM

IC3

2 Clock (1+Long Wait1)

Port allocation of word by static bus siz-

ingBus cycle has same setting as Area 0

(nCS0).

ingBus cycle has same setting as Area 0

(nCS0).

nCS6

6000000h

l

6FFFFFFh

l

6FFFFFFh

8bit

PRI_IC

IC301

3 Clock (1+Long Wait2)

Port allocation of byte by static bus sizing.

7

KX-NCP1290CJ

3.2.1.3.

Interrupt

Shows the external interrupt image.

External interrupt image

Note:

• nHALT signal polls using I/O port to achieve the consistency with the existing PBX.

However, in case the CPU(IC1) moves to the sleep mode while the system is halted, the unit returns from the sleep mode receiv-

ing the interrupt signal in CPU(IC1) when nHALT is released in accordance with its specification.

ing the interrupt signal in CPU(IC1) when nHALT is released in accordance with its specification.

• The nIRQ[0] interrupt of ASIC(IC2) should be set to the output, which is used as an interrupt output to the CPU (IC1); mainly

DPRAM communication interrupt.

The LOS signal of PRI-IC(IC301) is the level output which goes to "H" when the line reference is lost.

Consequently, inputting the inverted LOS signal to the CPU (IC1) enables to generate a negative edge interrupt while the line ref-

erence is lost.

Also setting nIRQ4 terminal of CPU(IC1) to I/O port makes polling possible.

The unit is provided with interrupt processing in order to achieve the consistency with the existing PBX.

Polling with I/O port is disable because nRxMF signal of PRI-IC(IC301) is generated in a periodical frame timing.

The LOS signal of PRI-IC(IC301) is the level output which goes to "H" when the line reference is lost.

Consequently, inputting the inverted LOS signal to the CPU (IC1) enables to generate a negative edge interrupt while the line ref-

erence is lost.

Also setting nIRQ4 terminal of CPU(IC1) to I/O port makes polling possible.

The unit is provided with interrupt processing in order to achieve the consistency with the existing PBX.

Polling with I/O port is disable because nRxMF signal of PRI-IC(IC301) is generated in a periodical frame timing.

• The unit should be kept open with a jumper unpopulated to avoid conflicting between output of nIRQ[0] of ASIC(IC2) and the sig-

nal.

8

KX-NCP1290CJ

3.2.2.

ISDN Primary Rate Interface Function

3.2.2.1.

Line Interface Outline

The reference point of the line interface on the PRI30 card is Point S/T (Point U is not supported.) and the external and internal

line modes are supported as operating mode.

Also, the PRI23/PRI30 cards employ the PRI-IC (IC301) as the IC for Interface. See the "Line Interface Block" or the outline of

the interface connection. Shows the characteristics of the PRI-IC.

See the PRI-IC data sheet for detailed specifications.

line modes are supported as operating mode.

Also, the PRI23/PRI30 cards employ the PRI-IC (IC301) as the IC for Interface. See the "Line Interface Block" or the outline of

the interface connection. Shows the characteristics of the PRI-IC.

See the PRI-IC data sheet for detailed specifications.

Characteristics of the PRI-IC

3.2.2.2.

Line Interface Loopback

This card has a relay for loopback test on the primary side of the line to cut and divide into the line failure or the PBX's own fail-

ure, when there is a defect in operation.

Shows The outline diagram of the line interface loopback.

ure, when there is a defect in operation.

Shows The outline diagram of the line interface loopback.

Outline diagram of the line interface

Item

Contents

Remarks

Line Extraction Clock

2.048MHz/PRI30

DPLL

Low Jitter DPLL for clk generation (IC302)

Elastic Buffer

Two-frame elastic buffer (Rx & Tx)

Signaling Controller

• HDLC Controller

• CAS Controller

• Multiframe synchronization and synthesis ITU-T G.732 etc.

• CAS Controller

• Multiframe synchronization and synthesis ITU-T G.732 etc.

FIFO

64Byte x 2 128Byte x 3

PCM Highway Interface

2.048Mbps highway Interface

µP-Interface

8bit parallel Bus (Intel/Motorola)

Used Intel Mode for PRI30 Card.

Click on the first or last page to see other KX-NCP1290CJ (serv.man2) service manuals if exist.