Panasonic KX-NCP1173XJ (serv.man2) Service Manual ▷ View online

6

KX-NCP1173XJ

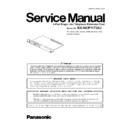

5 Technical Descriptions

5.1.

Block Diagram

BACK BOARD

+3

.3

V

Por

t#

5

Por

t#

6

Por

t#

7

Sa

m

e

as

“

P

o

rt

#

1

”.

Sa

m

e

as

“

P

o

rt

#

1

”.

S

a

m

e

as

“

P

o

rt

#1”

.

+1

5

VPT

+

15V

+

40V

H

W

C

L

K([

1

]

CP

[0

]

nC

S

[1

]

V

R

EF

+

VR

E

F-

nB

R

E

Q

nB

A

C

K

nI

R

Q

[0

]

L_n

R

S

T

nW

A

IT

nW

R

nR

D

nC

S

I

LA

[12:

0]

L

D

[7

:0

]

M

O

D

E

[5

:0

]

P

O

[7

:0

]

n

R

ESET

P

LLC

LK

HW

C

L

K

[0

]

P

3

[3

:0

]

P

2

[5

:4

]

R

X[

3

:0

]

E

C

_C

LK

E

C

_A

D

[15:

0

]

EC

_

P

A

R

EC

_

F

R

A

M

E

E

C

_

T

RDY

EC

_

S

T

O

P

EC

_

BE[

1

:0

]

EC

_

PER

R

EC

_

IN

T

EC

_

ID

SEL

EC

_

N

R

S

T

CT

_

N

E

T

RE

F

CT

_

F

RA

M

E

_

A

C

T

_C

8_A

C

T

_

D

[7

:0

]

CP

[0

]

A

[4:

0]

D

[7:

0]

ASI

C

(C

ID

)

nW

R

nR

D

nR

E

S

VR

E

F

CO

NT

nR

E

S

J

U

M

PER

R

ESET

IC

XT

A

L

16.

38

4

MH

z

J

U

M

PER

D

T

L[

3:

0]

R

inger

(

75V

rm

s

)

CO

DE

C

PEB

2466

ASI

C

(e

SAM

SO

N)

EC

_

D

ET

C

T

_

C

B_

A

RI

N

G

E

R

HW

C

L

K

HW

C

L

K

NC

S

1

HW

C

P

NW

R

NR

S

T

NR

D

UH

W

[0

]

nC

S

[1

]

XT

AL

4.096MH

z

UH

W

D

DR[

3

:0

]

P

1

[3

:0

]

D

T

H

[3:

0]

C

S

_D

LY

_D

T

AC

_

A

L

M

nC

S-

D

M

A

DO

UT

DI

N

DCL

K

CS

DRA

DRB

DX

A

DX

B

PC

L

K

MC

L

K

DI

N

DO

UT

DCL

K

C_

CS

[

1:

0]

FH

LD

H

W

[0

]

LU

H

W

[0

]

C_

CS

[1

:0

]

DH

W

[0

]

UH

W

[0

]

CL

K

FS

C

FH

Se

rg

e

EM

C

TA

RA

Be

ll R

e

la

y

O

PEAM

P

D

C

F

eedi

ng(

+30V

)

D

C

Feedi

ng(

G

N

D

)

Hook-Det

&

Ri

ngtr

ip-Det

Be

ll

Re

la

y

Dr

iv

e

r

DT

M

F

RE

C

1/4

SLT I

/F

nT

O

E

[0

]

ST

D

[0

]

n

H

OOK

[0

]

B

E

LL[

0]

D

[3:

0]

nT

O

E

[7

]

ST

D

[7

]

D

[3:

0]

n

H

OOK

[7

]

B

E

LL[

7]

nT

O

E

[7

]

ST

D

[7

]

D

[3:

0]

n

H

OOK

[7

]

B

E

LL[

7]

P2

0

P

5

[3

:0

]

T

D

E

[3:

0]

P

4

[3

:0

]

P

22

P

23

nC

S

0

nR

E

S

R

ESET

DR

IV

E

R

DR

IV

E

R

+3

.3

V

MO

D

E

4

P

O

[7

:0

]

JU

M

PER

8

Por

t#

2

Por

t#

3

Por

t#

4

Por

t#

8

Sa

m

e

as

“

P

o

rt

#

1”

.

Sa

m

e

as

“

P

o

rt

#

1”

.

Sa

m

e

as

“

P

o

rt

#

1”

.

Sa

m

e

as

“

P

o

rt

#

1

”.

nT

O

E

[6

]

ST

D

[6

]

D

[3:

0]

n

H

OOK

[6

]

B

E

LL[

6]

nT

O

E

[6

]

ST

D

[6

]

D

[3:

0]

n

H

OOK

[6

]

B

E

LL[

6]

nT

O

E

[5

]

ST

D

[5

]

D

[3:

0]

n

H

OOK

[5

]

B

E

LL[

5]

nT

O

E

[5

]

ST

D

[5

]

D

[3:

0]

n

H

OOK

[5

]

B

E

LL[

5]

nT

O

E

[2

]

ST

D

[2

]

D

[3:

0]

n

H

OOK

[2

]

B

E

LL[

2]

nT

O

E

[2

]

ST

D

[2

]

D

[3:

0]

n

H

OOK

[2

]

B

E

LL[

2]

nT

O

E

[4

]

ST

D

[4

]

D

[3:

0]

n

H

OOK

[4

]

B

E

LL[

4]

nT

O

E

[4

]

ST

D

[4

]

D

[3:

0]

n

H

OOK

[4

]

B

E

LL[

4]

nT

O

E

[1

]

ST

D

[1

]

D

[3:

0]

n

H

OOK

[1

]

B

E

LL[

1]

nT

O

E

[1

]

ST

D

[1

]

D

[3:

0]

n

H

OOK

[1

]

B

E

LL[

1]

nT

O

E

[3

]

ST

D

[3

]

D

[3:

0]

n

H

OOK

[3

]

B

E

LL[

3]

nT

O

E

[3

]

ST

D

[3

]

D

[3:

0]

n

H

OOK

[3

]

B

E

LL[

3]

DO

UT

DI

N

DCL

K

CS

DRA

DRB

DX

A

DX

B

PC

L

K

MC

L

K

FS

C

R

ESET

C_

CS

[1

]

C_

CS

[0

]

O

n

-B

oar

d

R

inger

+

40V

+

15V

20H

z

/25H

z

S

ignal

+5

V

DC

/D

C

DC

/D

C

DC

/D

C

DC

/D

C

+2

.5

V

DC

/D

C

DC

/D

C

KX-NCP1

173XJ BLOCK DIAGRAM

7

KX-NCP1173XJ

5.2.

Circuit Operation

5.2.1.

Control-System Circuit

5.2.1.1.

IC100 (ASIC)

• EC bus interface

Independent bus for 16bit/8MHz two-way address data multiplex.

• CT bus interface

Supports eight 8.192MHz highways (128 time slots).

• Local TSW

Exchanges the time slots between CT bus (1024ch) and local highway (64ch).

• Local highway interface

Accommodates 2.048, 4.096, and 8.192MHz highways (Up to 64 time slots).

• Local gain control

Controls the gain of the local highway up-and-down 64ch in 1db step arbitrarily.

• Local TSW

Exchanges the time slots between CT bus (1024ch) and local highway (64ch).

• Local gain control

Controls the gain of the local highway up-and-down 64ch in 1db step arbitrarily.

• PT interface

Allows APT/DPT interface to be selected for each port.

• CODEC interface

Can connect up to four Infineon-manufactured PEB2466, and is intended for enabling the line control.

• GPIO interface

Parallel interface that is arbitrarily programmable bidirectionally.

• Time slot structure

The following is the time slot structure of the local highway on NCP1170.

8

KX-NCP1173XJ

5.2.2.

Line-System Circuit

5.2.2.1.

SLT interface

• CODEC control......IC300

Infineon-manufactured PEB2466 is used. The analog characteristics, such as BN, frequency characteristic, level, and sidetone,

are set by the CODEC interface DCLK, CS, DOUT, and DIN. The built-in I/O port is used for HOOK detection, DTMF detection,

BELL relay control, and DIAG relay control.

are set by the CODEC interface DCLK, CS, DOUT, and DIN. The built-in I/O port is used for HOOK detection, DTMF detection,

BELL relay control, and DIAG relay control.

• A/D, D/A conversion

The conversion of 4-line analog signal and G.711 format PCM code (

µ/A) is carried out.

• SLT current-supply circuit

The current-supply circuit feeds current at the constant-current circuit. When the telephone is taken off the hook, DC loop is

formed.

The feeding current is limited to 30mA by the circuit configurations of R59, Q53, R60, and Q54.

+40VTR

formed.

The feeding current is limited to 30mA by the circuit configurations of R59, Q53, R60, and Q54.

+40VTR

→ R62 → R59 → Q52 → RL52(b → c) → L203 → L204 →R L52(c →b) → Q51 → R60 → R61 → SLTG(0 V)

9

KX-NCP1173XJ

• Bell signal issuing circuit

When feeding and speech paths are connected, BELL relay will be in 'break' state. When the bell signal is issued, BELL relay will

be in “Make” state.

be in “Make” state.

• HOOK detecting circuit

When BELL signal is not output or when dial pulse is received, this circuit distinguishes whether SLT is off hook or on hook.

When SLT is off hook, DC loop is formed and current flows into U52. At this time, the collector of U52 (3, 4, and 5 pin), namely,

HOOK signal changes from H to L and is detected by CPU by way of CODEC R ASIC. When SLT is on hook, DC loop is

interrupted and the current flow into U52 (3, 4, and 5 pin) ceases; the collector of U52, namely, HOOK signal changes from L to

H and is detected by CPU in like manner.

When SLT is off hook, DC loop is formed and current flows into U52. At this time, the collector of U52 (3, 4, and 5 pin), namely,

HOOK signal changes from H to L and is detected by CPU by way of CODEC R ASIC. When SLT is on hook, DC loop is

interrupted and the current flow into U52 (3, 4, and 5 pin) ceases; the collector of U52, namely, HOOK signal changes from L to

H and is detected by CPU in like manner.

• Ring trip circuit

While BELL signal is output, this circuit detects SLT off-hook by the hardware, and makes BELL relay in 'break' state.

While BELL signal is issued, when SLT is on hook, U52 (1, 2, and 6 pin) is off. When SLT is taken off the hook, DC loop is

formed because 40V is superimposed on BELL signal; then, current flows into R52

While BELL signal is issued, when SLT is on hook, U52 (1, 2, and 6 pin) is off. When SLT is taken off the hook, DC loop is

formed because 40V is superimposed on BELL signal; then, current flows into R52

→ R58 → D51 → U52, and U52 (1, 2, and 6

pin) becomes on.

When U52 (1, 2, and 6 pin) has become on, because the base of Q57 that is the driver of BELL relay becomes L, BELL relay will

be in 'break' state and SLT current-supply circuit feeds current to SLT.

When U52 (1, 2, and 6 pin) has become on, because the base of Q57 that is the driver of BELL relay becomes L, BELL relay will

be in 'break' state and SLT current-supply circuit feeds current to SLT.

• DTMF signal detecting circuit

Each port has its DTMF receiver.

Ports A to D carry out detection at IC400.

That DTMF data has become valid at EST terminal = H is detected by CPU by way of CODEC

Ports A to D carry out detection at IC400.

That DTMF data has become valid at EST terminal = H is detected by CPU by way of CODEC

→ ASIC, and then CPU reads and

detects the data of DTMF receiver.

• 2W-4W converting circuit

This circuit converts between the 2-line audio signal of APT or SLT and the 4-line audio signal on CODEC.

The audio signal from SLT is input to the differential amplifying circuit of IC302 (1, 2, and 3 pin) by way of C55 and C56, and its

output is input to CODEC.

CODEC output is issued to SLT in the form of the synthesis of the signal that is output through by way of R63 and the one that is

reversely output by IC302 (5, 6, and 7 pin). Programmable frequency characteristic adjusting filter, sidetone removing filter, and

return loss compensating filter are included in CODEC.

The audio signal from SLT is input to the differential amplifying circuit of IC302 (1, 2, and 3 pin) by way of C55 and C56, and its

output is input to CODEC.

CODEC output is issued to SLT in the form of the synthesis of the signal that is output through by way of R63 and the one that is

reversely output by IC302 (5, 6, and 7 pin). Programmable frequency characteristic adjusting filter, sidetone removing filter, and

return loss compensating filter are included in CODEC.

Click on the first or last page to see other KX-NCP1173XJ (serv.man2) service manuals if exist.