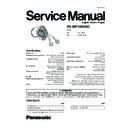

Panasonic SV-MP100VGC Service Manual ▷ View online

TUNER BLOCK

A

IC1

15

14

14

5

7

9

11

13

12

10

8

6

3

4

4

1

2

2

17

16

19

18

21

20

20

23

22

22

24

CN1

(TO MAIN CIRCUIT CN2)

HEADPHONE

SV-MP100V BLOCK DIAGRAM

TP48

TP47

S.S.G

F=87.5MHz

Mod=30%

Mod f=400Hz

F=87.5MHz

Mod=30%

Mod f=400Hz

233.0mV P-P

Radio (analog) Signal Line.

Notes :

MP3 and FM and IC REC Signal Line.

FM RF Signal Line.

FM RF Signal Line.

Voltage from negative terminal of battery.

( )...MP3 position,[ ]...FM position.

No mark...MP3 and FM position.

( )...MP3 position,[ ]...FM position.

No mark...MP3 and FM position.

C1BB00000997

FM TUNER

FM TUNER

15

14

5

7

9

11

13

12

8

6

3

4

2

17

16

19

18

23

22

24

28

29

26

27

25

38

39

36

37

34

35

32

33

W/R

L GAIN

AGND

V CCD

RFI 1

RF GND

RFI 2

TAGC

CP

OUT

VCO

TANK1

VCO

TANK2

VCC (VCO)

DGND

VCCD

DA

TA

CLOCK

BUSENABLE

BUSMODE

SWPORT1

SWPORT1

XTAL1

XTAL2

LIMDEC1

LIMDEC2

TIFC

V

ref

MPXO

TMUTE

V

AFR

V

AFL

PILFIL

PHASEFIL

GAIN

STABILIZTION

RESONANCE

AMPLIFIER

AMPLIFIER

LIMITER

DEMODULATOR

POWER

SUPPLY

SUPPLY

SOFT

MUTE

MUTE

MPX

DECODER

CRYSTAL

OSCILLATOR

OSCILLATOR

SOFTWARE

PROGRAMMABLE

PROGRAMMABLE

PROT

I/O-MIXER

1st FM

1st FM

AGC

N1

2

TUNING SYSTEM

VCO

IF CENTER

FREQUENCY

ADJUST

LEVEL

ADC

ADC

IF

COUNTER

COUNTER

MUX

Programmable

divider output

divider output

reference frequency

divider output

divider output

I C-BUS

AND

3-WIRE BUS

AND

3-WIRE BUS

2

momo

pilot

SDS

X1

13MHz

L1

LOOP SW

FM RF Signal Line

1

2

3

4

VIN

VOUT

CE

VSS

IC6

[0] (0)

[2.8]

(0)

(0)

[3.25]

(1.35)

IC6

Regulate

Voltage

Voltage

[3]

(0)

(0)

EXT

GND

VOUT VDD

CE

5

3

4

1

2

0

[1.38]

[3.26]

(1.36)

(1.36)

[3.26]

(1.36)

(1.36)

[3.0]

(0)

(0)

(0)

0

[1.40]

(1.45)

(1.45)

AAA

SIZE(LR03,AM-4)

BA

TTER

Y

ICP1

C0DBAGZ0021

DC-DC CONV

IC9

D1

S2

S1

D2

G1

G2

[1.33]

(1.33)

[0]

(0)

(0)

[0]

(0)

(0)

[1.33]

(1.33)

[1.33]

(1.33)

[1.33]

(1.33)

1

2

3

4

5

6

Q12

MCH6616

MUTE

MUTE

17

SV-MP100VGC

SV-MP100V BLOCK DIAGRAM

R18

M16

V10

A17

C9

E18

D16 MPMC address 3

MPMC

address 16

MPMC data input/output 0

MPMC data input/output 4

MPMC data input/output 3

MPMC data input/output 2

MPMC data input/output 1

MPMC data input/output 5

MPMC data input/output 7

MPMC data input/output 6

DAI Serial data input

MPMC_NOE:

Output enable for static memories.

Active LOW. Used for static

memory devices.

Output enable for static memories.

Active LOW. Used for static

memory devices.

MPMC_NSTCS_0:

Static memory chip select 0.

Default active LOW. Used

for static memory device.

Static memory chip select 0.

Default active LOW. Used

for static memory device.

U17

U14 T17

T15

J17

H15

B14

A13

A1 A2

A3

B2

A4 B4 A5 B5

G16

IC3

C2HBZG000008

DSP IC

A12

A17

C9

E18

D16

A12

MPMC_BLOUT0:

The signals nMPMCBLSOUT[0]

select byte lane [7:0] on the data bus.

Used for static memories.

The signals nMPMCBLSOUT[0]

select byte lane [7:0] on the data bus.

Used for static memories.

LCD Display

XATLL_OUT

XTALH_IN

HP_OUTR: SDAC Right Headphone Output

HP_OUTCA: HEADPHONE common output reference

HP_OUTCB: HEADPHONE common output reference

ADC_VINR: SADC Right Analog Input

ADC_VINL: SADC Left Analog Input

LCD_RW-WR:

6800 read/write select 8080 active "high" write enable

LCD_E_RD: 6800 enable

8080 active "high" write enable

LCD_DB_4

LCD_DB_5

LCD_DB-7

LCD_DB_6

LCD_DB_1

LCD_DB-3

LCD_DB_2

LCD_RS: 'high' Data

register selsct 'low'

Instruction register select

register selsct 'low'

Instruction register select

LCD_DB-0

LCD_CSB: Chip Select

T1

T4

P3

N1

N2

T10

V9

F3

C2

B3

C1 C3 D2 D1 D3 E2 E3 F2 G2

HP_OUTL: SDAC Left Headphone Output N3

R3

J1

X2

12MHz

15

3.3V

VDD

D18

ADC_MIC:

Microphone Input

Microphone Input

USB_DP: Positive USB data line

usb 2.0 FS

usb 2.0 FS

USB_DM:

Negative USB data line

usb 2.0 FS

Negative USB data line

usb 2.0 FS

USB_RPU: Soft connect output usb 2.0 FS

USB_VBUS:

USB Supply detection line

usb 2.0 FS & usb 2.0

USB Supply detection line

usb 2.0 FS & usb 2.0

USB PORT

CN3

3.3V

USB

CONTROL

CONTROL

MPMC address 2

A18

MPMC_A_6

MPMC address 5

12 MHz clock input

12 MHz clock input

430.0mV P-P

M17

N17

T18

P17

L10

L7

DC_DC_LX2:

Connection to DC/DC2 external coil

Connection to DC/DC2 external coil

DC_DC_LX1:

Connection to DC/DC1 external coil

Connection to DC/DC1 external coil

DC_DC_VBAT:

Battery supply voltage

Battery supply voltage

DC_DC_VUSB:USB supply voltage

MPMC

address 18

IC10

Regulator

DC/DC1 3.3V output voltage

DC/DC1 3.3V input voltage

Analog supply 10-bit ADC

9

7

6

8

13

12

17

16

19

18

42

44

43

41

36

37

32

30

31

29

N.C R/B

RE

CE

Vcc Vss

CLE ALE WE WP

I/O

0

0

I/O

1

1

I/O

2

2

I/O

3

3

Vss

Vcc

I/O

4

4

I/O

5

5

I/O

6

6

I/O

7

7

IC2

FLASH MEMORY

B5

A5

B4

A4

A3

B2

A2

A1

15

14

14

5

7

9

11

13

12

10

8

6

3

4

4

1

2

2

17

16

16

19

18

18

21

20

20

23

22

22

24

CN2 (TO TUNER CIRCUIT CN1)

L17 DC_DC_PLAY

IIC_HDA

IIC_SCL

Key

Control

Control

Notes :

REC Signal Line.

Radio Signal Line.

MP3/FM/IC REC

Signal Line.

Signal Line.

LCD Light

Control

Control

IC8

Regulator

Regulator

3.3V

3.3V

A17

C9

E18

D16

A12

A3

B2

A2

A1

B5

A5

B4

A4

MIC

OPR LED

DD

MAIN BLOCK

B

18

SV-MP100VGC

I/O 0 ~ I/O7: DATA INPUTS/OUTPUTS

The I/O pins are used to input command,address and data, and to output data during read operations.

The I/O pins are used to input command,address and data, and to output data during read operations.

The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.

Vcc: POWER Vcc is the power supply for device.

Vss: GROUND

R/B: READY/BUSY OUTPUT

The R/B output indicates the status of the device operation.When low, it indicates that a program, erase or random read operation is in process

and returns to high state upon completion.It is an open drain output and does not float to high-z condition when the chip is deselected or when

outputs are disabled.

The R/B output indicates the status of the device operation.When low, it indicates that a program, erase or random read operation is in process

and returns to high state upon completion.It is an open drain output and does not float to high-z condition when the chip is deselected or when

outputs are disabled.

RE: READ ENABLE

The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which

also increments the internal column address counter by one.

The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which

also increments the internal column address counter by one.

CE: CHIP ENABLE

The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and the device does not return to standby

mode in program or erase opertion. Regarding CE control during read operation, refer to "Page read" section of Device operation.

The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and the device does not return to standby

mode in program or erase opertion. Regarding CE control during read operation, refer to "Page read" section of Device operation.

CLE: COMMAND LATCH ENABLE

The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the

command register through the I/O ports on the rising edge of the WE signal.

The CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the

command register through the I/O ports on the rising edge of the WE signal.

ALE: ADDRESS LATCH ENABLE

The ALE input controls the activating path for address to the internal address registers.Addresses are latched on the rising edge of

WE with ALE high.

The ALE input controls the activating path for address to the internal address registers.Addresses are latched on the rising edge of

WE with ALE high.

WE: WRITE ENABLE

The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.

The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.

WP: WRITE PROTECT

The WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the

WP pin is active low.

The WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the

WP pin is active low.

PIN DESCRIPTION

9

7

6

8

13

12

17

16

19

18

42

44

43

41

36

37

32

30

31

29

N.C R/B

RE

CE

Vcc Vss

CLE ALE WE WP

I/O

0

0

I/O

1

1

I/O

2

2

I/O

3

3

Vss

Vcc

I/O

4

4

I/O

5

5

I/O

6

6

I/O

7

7

IC2

FLASH MEMORY

IC2 C3FBEC000011 FLASH MEMORY

19

SV-MP100VGC

Solid State Audio

C2HBZG000008

BLOCK DIAGRAM

LCD

Interface

Master/Slave

IIC Interface

SRAM

10-bits ADC

interface

ROM

USB 2.0 FS ATX

Interface

FLASH

Interface

Flash

RAMI

ROMI

Multi-Layer AHB

ADC10B

DAC

INT

32kB

(ASYNC)

(ASYNC)

(ASYNC)

(SYNC)

64kB

SAI

SAO

HP

MIC/

DEC

ADC

M

U

X

X

M

U

X

X

SRC

AUDIO SS

(ASYNC)

MEM CNTR

INTC

IC3 C2HBZG000008

V15

MPMC

A12,A17,C9,E18,

D16,D18,A14,

B14,A13,B13,

A1,A2,B2,A3,

A4,B4,A5,B5.

D16,D18,A14,

B14,A13,B13,

A1,A2,B2,A3,

A4,B4,A5,B5.

U5,T6,U6,T7,

U7,V10,U10

U7,V10,U10

U3,V3,T3,U2,

V1,V2,T1,T4,

U1,R3,T2.

V1,V2,T1,T4,

U1,R3,T2.

M3,M2,L1,L2,

M1,P3,N3,N2,

N1,R1,R2,P2,

P1.

M1,P3,N3,N2,

N1,R1,R2,P2,

P1.

H16,J17

T15,U17,T17,

U14,P16,R17,

R16,T16,U15,

U16,U18,V18

U14,P16,R17,

R16,T16,U15,

U16,U18,V18

G2,F2,E3,E2,

D3,D1,D2,C3,

C1,C2,B3,F3.

D3,D1,D2,C3,

C1,C2,B3,F3.

Micro Processor Unit

(MPU)

(MPU)

(AHB=Advanced High-Performance Bus)

Digital

Audio

Codec

Audio

Codec

(Multi Purpose

Memory Control)

Memory Control)

Fiash-Memory Control

Data,Command and

Address I/O

Address I/O

AHB AND

VPB Bridge

VPB Bridge

AHB AND

VPB Bridge

VPB Bridge

AHB AND

VPB Bridge

VPB Bridge

20

SV-MP100VGC

Click on the first or last page to see other SV-MP100VGC service manuals if exist.