LG 55LW5500-CA (CHASSIS:LC12C) Service Manual ▷ View online

C

- 24 -

(Pr.2~4 of CADTV will be updated automatically after changing channel to Pr.1)

ATV

Pr

System

Band

Name

CH

Freq.

Factory

1 NTSC

M

V/UHF

US-04 C

04

67.25 P/T

LGEND

2

NTSC

M

CABLE

J-01

S 67

91.25

P/T LGEND

3 NTSC

M

V/UHF

US-13 C

13

211.25

P/T

LGEND

4 NTSC

M

Cable US-14 C

14

471.25

P/T

LGEND

5 NTSC

M

V/UHF

US-63 C

63

765.25

P/T

LGEND

6 NTSC

M

CABLE

-

S

15

127.25

LGEND

7 PAL DK

V/UHF

D-10 C

10

200.25

P/T

LGEND

8 PAL DK

V/UHF

D-36 C

36

695.25

P/T

LGEND

9

C34

10 PAL I V/UHF I-11

C

11 231.25 P/T

11 PAL I V/UHF I-41

C

41 631.25 P/T

12

S39

807.25

CATV

Pr

System

Band

Name

CH

Freq.

Factory

1 PAL DK

V/UHF -

C

02 57.75 LGEND

C

- 25 -

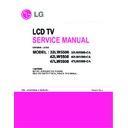

Block diagram for W5500 M/B_Input

H

ig

h

C

ha

ss

is

B

C

M3

52

30

(IC1

01

)

H

ig

h

C

ha

ss

is

H

ig

h

C

ha

ss

is

B

C

M3

52

30

B

C

M3

52

30

(IC1

0

(IC1

0

1

1

)

)

EEPRO

M

( I

C

80

2)

EEPRO

M

( I

C

80

2)

(J

K

804

)

(J

K

801

)

DSUB

_

R/

G/

B

+

, DSUB

_

DE

T

,

RG

B

_DDC

_S

CL/

SDA

P

C

_

R/

L _

IN

AP2

19

1D

SG

(IC

55

02

)

AP2

19

1

AP2

19

1

D

D

SG

SG

(IC

(IC

55

02

55

02

)

)

R

G

B

In

PC

A

udi

o

U

S

B

(Si

de

)

(JK

55

0

1

/2

)

S

PD

IF

J

K

80

2

S

PD

IF

_O

U

T

(J

K

703

)

D0/1/2+/

-, HDM

I_HP

D_1,CK+/

-_HDM

I1

DDC_

SCL

1/S

D

A1

HD

M

I1

In

(J

K

701

)

DD

C

_SCL

2/

S

DA

2

HD

M

I2

In

(J

K

702

)

DD

C

_SCL

3/

S

DA

3

HD

M

I3

In

IC7

01

HD

M

I

SWI

TCH

SI

I9

287

B

HD

M

I_

R

X

0+

/-,

R

X1

+/

-,R

X

2+

/-,

CLK

+/

-

HD

M

I_

SCL

/S

DA

P1302

M

_

Re

m

oc

on

M

_R

em

ot

e_

R

X

/ T

X

M

_R

F

M

odul

e_

r

es

et

D

C/

DD_M

R

EM

O

TE,

3D_

G

PI

O

_0

/1

/2

,3

D_

SY

N

C

_R

F

CVB

S

G

en

de

rJ

K

110

2

Com

p

G

end

er

JK1

10

1

A

V

2_

C

B

V

S_

IN

, AV

2_

C

V

B

S

_D

ET

;

A

V

2_

L/

R

_I

N

CO

M

P1

_Y

/P

b/

Pr

, C

O

M

P1_

D

ET

SC/C

O

M

P2

_R

/L

_I

N

,

SC

_D

ET

/C

O

M

P2

_DET

R

S2

32

C

(J

K

80

5)

R

S2

32

C I

C

M

A

X3

23

2C

D

R

IC8

03

R

S2

32

C I

C

R

S2

32

C I

C

M

A

X3

23

2C

D

R

M

A

X3

23

2C

D

R

IC8

03

IC8

03

Wi

re

le

ss

(J

K

100

1)

Wi

re

le

ss_

D

ET

,Wi

re

less_

PWR

_E

N

N

EC

_

M

ic

om

UPD7

8F

05

14

IC6

02

N

EC

_

M

ic

om

N

EC

_

M

ic

om

UPD7

8F

05

14

UPD7

8F

05

14

IC6

02

IC6

02

N

EC

_T

X

D

/R

X

D

N

EC

_I

S

P_

TX/

R

X

Wi

re

le

ss

_

SCL

/S

DA

(SCL2

/S

DA2

_3

.3

V)

E

PH

Y

_R

DN

/R

DP

ET

H

ER

N

ET

(J

K

140

1)

LAN

CN

:

TD

FR-C

056

D

,T

U2

20

2

HK

:

TD

FR-C2

56

D

,T

U2

20

2

CN

:

CN

:

TD

FR

TD

FR

-

-

C

056

D

,

C

056

D

,T

U2

20

2

TU2

20

2

HK

:

HK

:

TD

FR

TD

FR

-

-

C2

56

D

,

C2

56

D

,T

U2

20

2

TU2

20

2

Tune

r

(r

efe

r

to

pa

ge

3

)

SC/R

_C

IM

P2

_Pr

,SC

/B

_C

O

M

P2_

Pb,

SC

/G

_C

O

M

P2

_Y

Com

p

JK

11

05

CVB

S

JK

110

4

A

V

1_

C

B

V

S_

IN

, AV

1_

C

V

B

S

_D

ET

,A

V

1_

L/

R

_I

N

E

PH

Y

_A

CT

IVI

TY

/

LI

N

K,

E

PH

Y

_T

DP

/T

DP

DD

C

_SCL

4/

S

DA

4

HD

M

I4

In

(J

K

704

)

HD

M

I_

A

R

C

D0/1/2+/

-, HDM

I_HP

D_2,CK+/

-_HDM

I1

D0/1/2+/

-, HDM

I_HP

D_3,CK+/

-_HDM

I1

D0/1/2+/

-, HDM

I_HP

D_4,CK+/

-_HDM

I1

B

CM

_R

X/T

X

EEPRO

M

( I

C

80

1)

EEPRO

M

( I

C

80

1)

DSUB

_

H

/V SYN

C

EEPRO

M

( I

C

60

1)

EEPRO

M

( I

C

60

1)

EE

PR

O

M

_

SCL/

S

DA

AP2

19

1D

SG

(IC

55

01

)

AP2

19

1

AP2

19

1

D

D

SG

SG

(IC

(IC

55

01

55

01

)

)

SI

D

E

_U

S

B

_D

M

/DP

SI

D

E

_U

S

B

_O

C

D1

WI

FI

_D

M

/DP

SI

D

E

_U

S

B

_O

C

D2

C

- 26 -

H

ig

h

C

ha

ss

is

B

C

M3

52

30

(IC1

01

)

H

ig

h

C

ha

ss

is

H

ig

h

C

ha

ss

is

B

C

M3

52

30

B

C

M3

52

30

(IC1

0

(IC1

0

1

1

)

)

N

VR

A

M

(1

M

, I

C1

03

)

N

VR

A

M

N

VR

A

M

(

(

1M

1M

, I

C1

0

, I

C1

0

3

3

)

)

NAND

FLA

SH

(8

G

bi

t, I

C

10

2)

NAND

FLA

SH

NAND

FLA

SH

(

(

8

8

G

G

bi

t

bi

t

, I

C

10

, I

C

10

2

2

)

)

NAND_

DA

TA

[0

-7

]

EE

PR

O

M

_SCL

/S

DA

LE

D

_R

/B

uz

z

KEY

1/

2

,IR

EE

PR

O

M

(IC6

01

)

EE

PR

O

M

(IC6

01

)

N

EC

_M

ic

om

IC6

02

N

EC

_M

ic

om

N

EC

_M

ic

om

IC6

02

IC6

02

IR

& KEY

P9

01

IR

& KEY

IR

& KEY

P9

01

P9

01

SCL2

/S

DA2

_3

.3

V

Po

w

er

B

/D

P5

02

Po

w

er

B

/D

Po

w

er

B

/D

P5

02

P5

02

INV_

CT

L,

R

L_

O

N

De

bu

gg

er

P6

01

De

bu

gg

er

De

bu

gg

er

P6

01

P6

01

N

EC

_I

S

P_

TX/

R

X

,O

C

D1

A/

B

,F

LM

D

0,

M

IN

C

O

M

_R

E

SET

SO

C

_

R

es

et

NAND

_

WEb

/A

LE

/CLE

…

LPF

SCL1

/S

DA1

_3

.3

V

Sp

e

a

ke

r

P1

80

1

A

udi

o

A

M

P

N

TP

-740

0L

IC1

80

2

A

udi

o

A

M

P

A

udi

o

A

M

P

N

TP

N

TP

-

-

740

0L

740

0L

IC1

80

2

IC1

80

2

AUD_

LR

C

H

/LR

CK/

SCK,

A

M

P_

M

ut

e

S

PK

_L

+

/-

S

PK

_R

+

/-

PW

M

S

DA

/SC

L1

_3

.3

V

TXA

/B

/C

/D

[0

-4

] N

/P,

TXA

/B

/C

/D

CLK

N/CLK

P

LV

D

S

_T

XA/

B

[0

-4

] N

/P,

LV

D

S

_T

XA/

B

CLK

N/CLK

P

LV

D

S

_T

XC/

D

[0

-4

] N

/P,

LV

D

S

_T

XC/

D

CLK

N/CLK

P

LG

E7

303

C

IC5

20

1

LG

E7

303

C

LG

E7

303

C

IC5

20

1

IC5

20

1

FR

C_

R

E

SET

LE

D

_B

/LG

L

O

G

O

LE

D

D

riv

ing

B

/D

P3

501

(51

PI

N

)

LE

D

D

riv

ing

B

/D

LE

D

D

riv

ing

B

/D

P3

501

(51

PI

N

)

P3

501

(51

PI

N

)

LE

D

D

riv

ing

B

/D

P3

502

(41

PI

N

)

LE

D

D

riv

ing

B

/D

LE

D

D

riv

ing

B

/D

P3

502

(41

PI

N

)

P3

502

(41

PI

N

)

Woof

er

N

TP

-740

0L

IC1

80

1

Woof

er

Woof

er

N

TP

N

TP

-

-

740

0L

740

0L

IC1

80

1

IC1

80

1

SCL1

/S

DA1

_3

.3

V

AUD_

LR

C

H

/LR

CK/

SCK,

A

M

P_

M

ut

e

SPK_

W

o

o

fe

r

+

/-

Woof

er

P1

80

2

Woof

er

Woof

er

P1

80

2

P1

80

2

AUD_

M

A

ST

ER

_CLK

AUD_

M

A

ST

ER

_CLK

SPI

F

LASH

( I

C

520

2,

2M

)

SPI

F

LASH

( I

C

520

2,

2M

)

S

PI

_DO

/C

S/

SC

LK/

D

I

S/

T_

SC

L/

S

DA

Ea

rp

hon

e

A

M

P

IC8

04

Ea

rp

hon

e

A

M

P

Ea

rp

hon

e

A

M

P

IC8

04

IC8

04

HP_

L/

R

_O

U

T_

N

/P

HP_

L/

R

O

U

T

HP

DDR3

( I

C

530

1)

DDR3

( I

C

530

1)

FR

C_

A

[0

-1

3],

FR

C_

B

A0/

1/

2,

FR

C

_M

CLK/CLE/

M

CLKB

…

(

DD

R3

_A

[0

-13

],DD

R

3_

B

A0/

1/

2,

DD

R

3_

M

CLK

…

)

FR

C_

DQ

U

/DQ

L[0

-7

]

(DD

R

3_

DQ

U/

DQ

L[

0-7

])

DD

R

( I

C4

01

,IC4

02

)

DD

R

( I

C4

01

,IC4

02

)

DD

R

_AA

…

,

DD

R

01

/23

_CLK/C

LKb,

……

DD

R

_DQ

[0

-7

]/[

8-

15

]/[1

6-

23

]/[

24

-3

1]

JK

8

03

Block diagram for LW5500 M/B_Output

C

- 27 -

H

ig

h

C

h

as

si

s

B

C

M3

52

30

(I

C1

01

)

H

ig

h

C

h

as

si

s

H

ig

h

C

h

as

si

s

B

C

M3

52

30

B

C

M3

52

30

(I

C1

0

(I

C1

0

1

1

)

)

T

D

FR-C0

56

D

_

T

U2202

(H/NIM

f

o

r CN)

T

D

FR

T

D

FR

-

-

C0

56

D

C0

56

D

_

T

U2202

(H/NIM

f

o

r CN)

S2

_

R

e

se

t,I

F

_

A

G

C

_M

A

IN

,T

U_

R

ESET

,R

F

_S

WI

T

CH

/B

O

O

ST

ER

_CT

L

FE_

T

S

_

DA

T

A

[0

-7

],I

F

_

P/

N_

M

A

IN

CI S

lo

t

P

19

01

CI S

lo

t

CI S

lo

t

P

19

P

19

01

01

SCL0

/S

DA0

_3

.3

V

(for

A

T

V)

IC1905

B

u

ff

er

IC1905

IC1905

B

u

ff

er

B

u

ff

er

IC2301

(DV

B

-S

,

O

P

T

)

IC2301

IC2301

(DV

B

(DV

B

-

-

S

,

O

P

T

)

S

,

O

P

T

)

LNB

_

O

U

T

LNB

_T

X,

T

U_

T

S

_V

A

L

/ER

R

T

U

_T

S_

SY

N

C

,T

U_

T

S_

CLK

,T

U_

T

S_

VAL

T

S_

V

A

L

_ER

R

SCL3

/S

DA3

_3

.3

V

T

U

_CV

B

S/

SI

F

,

LNB

_I

N

T

CI_

ADD

R

[2

/3

/4

/7

/9

/

1

1/

12

/13

]

P

CM

_

ADD

R

[2

/3

/4

/7

/9

/

1

1/

12

/13

]

IC1903

bu

ff

er

IC1903

IC1903

bu

ff

er

bu

ff

er

CI_

DA

T

A

[0

-7

]

NAND_

DA

T

A

[0

-7

]

IC1904

CI_DE

T

IC1904

IC1904

CI_DE

T

CI_DE

T

CI_

D

ET

/CI_

C

D1

/CD2

CI_

ADD

R

[2

-1

4]

High Chassis

Block diagram –Tuner(GP3)

Click on the first or last page to see other 55LW5500-CA (CHASSIS:LC12C) service manuals if exist.