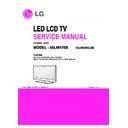

LG 55LW470S (CHASSIS:LD12P) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

CI_TS_DATA[1]

NAND_DATA[6]

FE_TS_DATA[3]

PCM_MDI[3]

NAND_DATA[5]

CI_DATA[1]

PCM_ADDR[2]

PCM_ADDR[4]

PCM_ADDR[9]

FE_TS_DATA[2]

CI_TS_DATA[5]

CI_DATA[6]

FE_TS_DATA[1]

PCM_TS_DATA[2]

CI_DATA[7]

PCM_ADDR[12]

CI_ADDR[1]

NAND_DATA[2]

CI_MDI[5]

PCM_MDI[5]

PCM_MDI[7]

CI_DATA[2]

PCM_TS_DATA[4]

CI_DATA[0]

CI_MDI[4]

CI_MDI[0]

CI_TS_DATA[7]

CI_MDI[1]

CI_DATA[6]

CI_MDI[5]

NAND_DATA[4]

CI_MDI[0]

FE_TS_DATA[0]

CI_ADDR[14]

CI_ADDR[10]

CI_TS_DATA[2]

PCM_MDI[6]

PCM_MDI[2]

PCM_TS_DATA[5]

CI_DATA[0]

CI_TS_DATA[6]

CI_MDI[3]

CI_MDI[6]

PCM_TS_DATA[3]

NAND_DATA[0]

CI_MDI[6]

CI_ADDR[8]

PCM_TS_DATA[6]

FE_TS_DATA[4]

PCM_MDI[4]

PCM_MDI[0]

PCM_TS_DATA[1]

CI_TS_DATA[0]

CI_ADDR[6]

NAND_DATA[7]

CI_MDI[2]

PCM_ADDR[3]

CI_DATA[7]

CI_DATA[5]

CI_MDI[7]

FE_TS_DATA[6]

CI_MDI[4]

PCM_ADDR[7]

PCM_TS_DATA[7]

CI_ADDR[0]

PCM_ADDR[11]

CI_TS_DATA[4]

PCM_TS_DATA[0]

CI_MDI[1]

FE_TS_DATA[5]

CI_DATA[3]

CI_MDI[7]

CI_DATA[3]

CI_DATA[2]

CI_ADDR[5]

CI_DATA[1]

CI_DATA[4]

CI_TS_DATA[3]

CI_DATA[5]

CI_DATA[4]

CI_MDI[2]

CI_MDI[3]

PCM_MDI[1]

FE_TS_DATA[7]

NAND_DATA[3]

PCM_ADDR[13]

NAND_DATA[1]

CI_TS_SYNC

R1954

22

CI

R1970

22

CI

R1961

22

CI

P1901

10067972-000LF CI

G1

G2

57

TS_OUT_CLK

21

ADDR12

52

VPP

16

/IRQA

10

ADDR11

47

TS_IN0

41

TS_OUT7

5

DAT6

36

/CI_DET1

59

CI_WAIT

23

ADDR6

45

IOWR

54

TS_IN5

18

VPP

49

TS_IN2

43

VS1

13

ADDR13

7

/CARD_EN1

38

TS_OUT4

2

DAT3

25

ADDR4

56

TS_IN7

20

TS_IN_CLK

51

VCC

15

/WR_EN

9

/O_EN

46

TS_IN_SYN

40

TS_OUT6

4

DAT5

35

GND

58

CI_RESET

22

ADDR7

53

TS_IN4

17

VCC

11

ADDR10

48

TS_IN1

42

CARD_EN2

12

ADDR8

6

DAT6

37

TS_OUT3

1

GND

24

ADDR5

55

TS_IN6

19

TS_IN_VAL

50

TS_IN3

44

IORD

14

ADDR14

8

ADDR10

39

TS_OUT5

3

DAT4

26

ADDR3

60

INPACK

27

ADDR2

61

REG

28

ADDR1

62

TS_OUT_VAL

29

ADDR0

63

TS_OUT_SYN

30

DAT0

64

TS_OUT0

31

DAT1

32

DAT2

33

/IO_BIT

34

GND

65

TS_OUT1

66

TS_OUT2

67

/CI_DET2

68

GND

69

R1902

22

CI

R1933

10K

OPT

R1917

22 OPT

L1901

BLM18PG121SN1D

CI

R1909

22

OPT

R1953

22

CI

R1919

22 OPT

CI_TS_DATA[3]

+3.3V_CI

AR1903

22

OPT

R1986

22

CI

NIM_TS_SYNC

/PCM_WE

CI 15

/CI_EN1

CI_ADDR[5]

CI_ADDR[0]

R1960

22

CI

PCM_ADDR[13]

NIM_VAL_ERR

R1929

10K

OPT

/PCM_IRQA

C1909

4.7uF

16V

4.7uF

16V

OPT

C1914

0.1uF

16V

0.1uF

16V

CI

CI_TS_DATA[6]

PCM_TS_CLK

R1922

22

CI

+5V_CI_ON

/CI_CE1

R1957

22

CI

CI_ADDR[11]

/CI_CE1

C1912

0.1uF

16V

CI

R1941

10K

CI

R1927

22

CI

R1967

22 CI

NAND_REb

+3.3V_Normal

R1938

62

CI

+5V_CI_ON

R1971

10K

CI

R1951

22

CI

CI_MDI[0-7]

R1907

22

CI

+3.3V_CI

/CI_CD2

+5V_CI_ON

/CI_CD1

R1940

10K

10K

OPT

NIM_TS_CLK

C1901

0.1uF

16V

OPT

+5V_Normal

PCM_TS_DATA[0-7]

R1946

10K

OPT

+3.3V_CI

PCM_ADDR[9]

NAND_WEb

R1910

22

OPT

R1901

22

CI

C1902

0.1uF

16V

OPT

/PCM_IORD

Q1902

AO3407A

CI

G

D

S

/CI_CD2

CI_ADDR[1]

CI_TS_CLK

C1911

0.1uF

16V

OPT

R1969

10K

CI

CI_ADDR[9]

C1915

0.1uF

16V

0.1uF

16V

OPT

R1980

100 CI

R1945

10K

OPT

R1966

10K

CI

R1985

10K

CI

R1936

0

OPT

R1949

22

CI

R1937

62

CI

R1959

22

CI

PCM_MCLKI

PCM_TS_SYNC

C1904

0.1uF

0.1uF

CI

CI_MIVAL_ERR

CI_ADDR[13]

CI_MISTRT

R1947

22

CI

PCM_ADDR[4]

PCM_MDI[0-7]

PCM_ADDR[9]

+3.3V_CI

R1931

22 CI

CI_ADDR[12]

R1918

22 OPT

R1903

22

CI

PCM_MIVAL_ERR

R1939

10K

CI

PCM_ADDR[12]

PCM_ADDR[12]

IC1903

74LVC245A

CI

3

A1

2

A0

4

A2

1

DIR

6

A4

5

A3

7

A5

8

A6

9

A7

10

GND

11

B7

12

B6

13

B5

14

B4

15

B3

16

B2

17

B1

18

B0

19

OE

20

VCC

CI_TS_DATA[0-7]

NAND_REb

PCM_ADDR[13]

R1956

22

CI

/PCM_OE

CI 9

CI_ADDR[2]

CI_ADDR[0]

PCM_ADDR[3]

+3.3V_CI

IC1904

74LVC1G32GW

CI

3

GND

2

A

4

Y

1

B

5

VCC

+3.3V_CI

CI_MDI[0-7]

CI_TS_VAL

PCM_ADDR[2]

CI_TS_DATA[0]

R1948

22

CI

CI_ADDR[10]

C1908

0.1uF

CI

CI_ADDR[3]

C1906

0.1uF

16V

OPT

R1958

22

CI

R1942

4.7K

4.7K

CI

R1934 10K OPT

/PCM_IOWR

R1965

47

CI

FE_TS_DATA[0-7]

/PCM_OE

/PCM_WAIT

CI_TS_DATA[1]

NAND_REb

NAND_RBb

R1962

22

CI

C1907

0.1uF

CI

AR1904 100 CI

/PCM_IOWR

CI 45

PCM_5V_CTL

CI_MISTRT

CI_TS_VAL

R1963

22

CI

L1902

BLM18PG121SN1D

CI

PCM_TS_VAL

GND

+3.3V_CI

CI_MCLKI

R1952

22

CI

PCM_ADDR[7]

R1935

0 CI

R1904

22

CI

CI_TS_DATA[5]

/CI_EN1

/CI_EN1

Q1901

2SC3052

2SC3052

CI

E

B

C

CI_DATA[0-7]

R1964

22

CI

NAND_DATA[0-7]

NAND_CLE

CI_ADDR[8]

PCM_MISTRT

CI_TS_CLK

R1928

22

CI

R1932

10K

CI

R1972

10K

CI

CI_ADDR[4]

/CI_CD1

R1973

10K

CI

CI_MIVAL_ERR

+5V_CI_ON

CI_ADDR[6]

+5V_CI_ON

/PCM_CE1

PCM_ADDR[7]

PCM_RST

/CI_EN1

R1976

22

CI

R1974

22

CI

NAND_WEb

CI_ADDR[7]

+5V_CI_ON

CI_ADDR[1]

+3.3V_CI

CI_TS_DATA[2]

CI_DATA[0-7]

CI_ADDR[14]

PCM_ADDR[2]

PCM_ADDR[11]

PCM_ADDR[4]

R1920

22

CI

R1926

22 CI

R1905

22

CI

C1905

10uF

10V

10uF

10V

CI

R1943

22K

22K

CI

C1903

0.1uF

16V

OPT

R1915

22

OPT

AR1905

100 CI

IC1901

74LVC125APW

CI

3

1Y

2

1A

4

2OE

1

1OE

6

2Y

5

2A

7

GND

8

3Y

9

3A

10

3OE

11

4Y

12

4A

13

4OE

14

VCC

/PCM_WE

/PCM_IORD

CI 44

+5V_CI_ON

R1906

22

CI

R1955

22

CI

CI_TS_SYNC

C1910

0.1uF

CI

PCM_ADDR[11]

R1968

10K

CI

/CI_CE2

/PCM_CE1

CI 7

R1944

0

OPT

R1950

22

CI

R1921

22

CI

/CI_CE2

CI_TS_DATA[7]

R1908

22

CI

+5V_CI_ON

CI_DET

CI_TS_DATA[4]

CI_MCLKI

PCM_ADDR[3]

IC1905

74LVC245A

CI

3

A1

2

A0

4

A2

1

DIR

6

A4

5

A3

7

A5

8

A6

9

A7

10

GND

11

B7

12

B6

13

B5

14

B4

15

B3

16

B2

17

B1

18

B0

19

OE

20

VCC

R1916

22 OPT

C1913

0.1uF

16V

CI

R1930

10K

OPT

R1975

10K

CI

IC1902

74AHC08PW

CI

3

1Y

2

1B

4

2A

1

1A

6

2Y

5

2B

7

GND

8

3Y

9

3A

10

3B

11

4Y

12

4A

13

4B

14

VCC

C1916

12pF

50V

12pF

50V

OPT

R1987

2.2K

2.2K

CI

AR1901

100 CI

AR1902

100 CI

R1924

100 CI

R1925

100 CI

R1923

220 CI

R1977

10K

OPT

1ST : EBK60752501, 2ND : EBK61011501

Close to CI Slot

3,3V_CI POWER

Close to Tuner

Q1901

NAND F/M Data

CI DETECT

1ST : 0TRIY80001A 2ND : 0TR387500AA

Close to CI Slot

Close to BCM35230

Close to BCM35230

CI

BCM INT Demod

CI TS OUTPUT

CI CONTROL INTERFACE

OE DIR CI_DATA NAND_DATA

L L OUTPUT INPUT

L H INPUT OUTPUT

H X Z Z

L L OUTPUT INPUT

L H INPUT OUTPUT

H X Z Z

CI TS INPUT

CI POWER ENABLE CONTROL

DUAL COMPONENT

Q1902

19

IC1904

BCM INT Demod

BCM35230

1ST : 0ISTLPH062A, 2ND : EAN40055001

58

2010.11.11

THERMAL

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

R2302

33

LNB

LNB_TX

L2301

33UH

SP-7850_33

LNB

C2324

68uF

35V

LNB

C2303

0.1uF

50V

0.1uF

50V

LNB

R2303

0

LNB

+3.3V_Normal

C2304 0.1uF

LNB

SCL1_3.3V

C2305

68uF

35V

LNB

D2301

40V

SMAB34

LNB

C2310

27pF

OPT

DCDC_GND

L2302

BLM18PG121SN1D

LNB

A_GND

LNB_OUT

C2308

0.22uF

LNB

+12V

+12V_LNB

D2304

40V

SMAB34

LNB

A_GND

DCDC_GND

C2312

0.1uF

50V

0.1uF

50V

LNB

A_GND

A_GND

A_GND

D2303

40V

SMAB34

LNB

R2314

0

C2309

27pF

OPT

DCDC_GND

+12V_LNB

A_GND

A_GND

A_GND

C2311

10uF

25V

10uF

25V

LNB

R2301

33

LNB

C2307

0.01uF

50V

LNB

SDA1_3.3V

C2302

1uF

50V

50V

LNB

LNB_INT

R2304

4.7K

LNB

DCDC_GND

A_GND

C2306

22000pF

LNB

C2301

0.22uF

25V

IC2301

A8290SETTR-T

LNB

1

BOOST

3

TCAP

7

TDI

9

VREG

10

SDA

11

ADD

12

SCL

13

NC_2

14

IRQ

15

NC_3

16

NC_4

17

NC_5

18

NC_6

19

BFC

20

NC_7

21

NC_8

22

BFO

23

NC_9

24

BFI

25

VIN

26

LX

27

GNDLX

28

LNB

5

TDO

8

GND

6

EXTM

4

NC_1

2

VCP

29

[EP]

D2302

1000V

US1M(suzhou)

LNB

R2313

0

DCDC_GND and A_GND are connected in pin#27

LNB

Input trace widths should be sized to conduct at least 3A

close to Boost pin(#1)

57

DVB-S2 LNB Part Allegro

23

close to VIN pin(#25)

2A

DCDC_GND and A_GND are connected

3A

Ouput trace widths should be sized to conduct at least 2A

BCM35230

2.4A

Max 1.3A

(Option:LNB)

PCB_GND and A_GND are connected

2010.11.02

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

CHBO_TS_SYNC

CHBO_TS_SERIAL

CHB_RESET

CHBO_TS_VAL_ERR

CHBO_TS_CLK

TS Output

50

28

BCM35230

NON CHB

NON CHB

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

LVDS_TXD4P

LVDS_TXC4N

LVDS_TXD3N

C3502

1000pF

50V

1000pF

50V

LVDS_TXA4N

LVDS_TXB3P

LVDS_TXC3P

R3506

33

LVDS_TXACLKN

LVDS_TXB4P

LVDS_TXC0N

LVDS_TXD0N

LVDS_TXD0P

R3502

10K

LVDS_SEL_LOW

LVDS_TXACLKP

LVDS_TXB3N

C3503

0.1uF

50V

0.1uF

50V

LVDS_TXA0N

+3.3V_Normal

LVDS_TXD1P

R3507

33

LVDS_TXD4N

LVDS_TXA3N

LVDS_TXA4P

LVDS_TXB4N

LVDS_TXBCLKN

P3502

FI-RE41S-HFK-A

1

NC

2

NC

3

NC

4

NC

5

NC

6

NC

7

NC

8

NC

9

GND

10

RC0N

11

RC0P

12

RC1N

13

RC1P

14

RC2N

15

RC2P

16

GND

17

RCCLKN

18

RCCLKP

19

GND

20

RC3N

21

RC3P

22

RC4N

23

RC4P

24

GND

25

GND

26

RD0N

27

RD0P

28

RD1N

29

RD1P

30

RD2N

31

RD2P

32

GND

33

RDCLKN

34

RDCLKP

35

GND

36

RD3N

37

RD3P

38

RD4N

39

RD4P

40

GND

41

GND

42

GND

C3501

10uF

25V

10uF

25V

OPT

LVDS_TXCCLKP

LVDS_TXB1N

LVDS_TXC2N

LVDS_TXC3N

LVDS_TXD2P

L_VS

LVDS_TXCCLKN

LVDS_TXB1P

LVDS_TXA0P

LVDS_TXC0P

LVDS_TXA3P

LVDS_TXC1N

P3501

FI-RE51S-HFK-A

1

NC

2

NC

3

NC

4

NC

5

NC

6

AUO_65_MIRROR

7

LVDS_SEL

8

NC

9

NC

10

L/DIM_ENABLE

11

GND

12

RA0N

13

RA0P

14

RA1N

15

RA1P

16

RA2N

17

RA2P

18

GND

19

RACLKN

20

RACLKP

21

GND

22

RA3N

23

RA3P

24

RA4N

25

RA4P

26

GND

27

BIT_SEL

28

RB0N

29

RB0P

30

RB1N

31

RB1P

32

RB2N

33

RB2P

34

GND

35

RBCLKN

36

RBCLKP

37

GND

38

RB3N

39

RB3P

40

RB4N

41

RB4P

42

GND

43

GND

44

GND

45

GND

46

GND

47

NC

48

VLCD

49

VLCD

50

VLCD

51

VLCD

52

GND

R3501

3.3K

LVDS_SEL_HIGH

LVDS_TXB2P

LVDS_TXDCLKP

LVDS_TXA1N

LVDS_TXBCLKP

LVDS_TXD3P

LVDS_TXB0N

LVDS_TXD1N

LVDS_TXA2P

LVDS_TXB2N

SDA2_3.3V

PANEL_VCC

LVDS_TXC2P

LVDS_TXA1P

R3503

10K

10K

BIT_SEL_LOW

LVDS_TXC1P

SCL2_3.3V

LVDS_TXB0P

LVDS_TXDCLKN

LVDS_TXC4P

LVDS_TXD2N

R3508

33

LVDS_TXA2N

L/DIM0_VS

M3_SCLK

M2_SCLK

M3_MOSI

M1_SCLK

L/DIM0_MOSI

M2_MOSI

M1_MOSI

L/DIM0_SCLK

M0_SCLK

M0_MOSI

R3509

10K

OPT

10K

OPT

R3510

10K

10K

+3.3V_FRC

L3501

MLB-201209-0120P-N2

P3503

12507WR-08L

1

2

3

4

5

6

7

8

9

R3512

33

LGD_2D/3D_CTRL

2D/3D_CTL

R3513

4.7K

4.7K

R3504

0

LPB_42/47/55

R3505

0

LPB_42/47/55

R3511

3.3K

AUO_65_MIRROR

+3.3V_Normal

R3514

33

AUO_2D/3D_CTRL

2D/3D_CTL

LVDS

LVDS_SEL

35

[51Pin LVDS OUTPUT Connector]

NON USED L/DIMMING

(FOR EDGE_LED)

(FOR EDGE_LED)

LOCAL DIMMING

BCM35230

58

Interface block

[To LED DRIVER]

BIT_SEL

[41Pin LVDS OUTPUT Connector]

PLACE SERIAL RESISTORS CLOSE TO URSA4

2010. 10. 20

Click on the first or last page to see other 55LW470S (CHASSIS:LD12P) service manuals if exist.