LG 50PA4900-TE (CHASSIS:PA21A) Service Manual ▷ View online

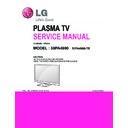

4-6. GP4

LM1

I2C MAP

I2C_SCKM1/GPIO75

I2C_SDAM1/GPIO76

I2C_SDAM1/GPIO76

GPIO49

GPIO50

GPIO50

I2S_IN_WS/GPIO149

SPDIF_IN/GPIO152

I2S_IN_SD/GPIO151

I2S_IN_BCK/GPIO150

I2C_SCKM2/DDCR_CK/GPIO72

I2C_SDAM2/DDCR_DA/GPIO71

I2C_SDAM2/DDCR_DA/GPIO71

IC400

AE6

AD6

AB5

AB3

AB3

D9

D7

D7

D8

C8

C8

P23

P24

P24

TU_SCL

TU_SDA

AMP_SCL

AMP_SDA

P_SCL

P_SDA

SUB_SCL

SUB_SDA

I2C_SCL

I2C_SDA

P500

LVDS

LVDS

TU300

TDSS-G201D

TDSS-G201D

IC300

STA368BWG

STA368BWG

P501

KEY/IR PIN8

KEY/IR PIN8

+3.3V_TU

R3082.2K

R309 2.2K

+3.3V

R624 2K

R623 2K

+3.3V_AVDD

R468 3.3K

R466 3.3K

+3.3V_ST

R539 4.7K

R538 4.7K

SCL_3.3V_MOD

SDA_3.3V_MOD

SDA_3.3V_MOD

IC503 EEPROM

IC502 HDCP (OTP)

IC502 HDCP (OTP)

+3.3V_AVDD

R469 2.2K

R468 2.2K

EAX64337201_0

5. GP4 LM1 SOC Power Sequence Procedure

▶

Hot Point

SOC_RESET

+3.3V_AVDD

+1.10V_VDDC

+1.5V_DDR_IN

+3.3V_AVDD

+1.10V_VDDC

+1.5V_DDR_IN

0ms

Multi_PWR

288ms

/

[Spec] before all pwr input raise

SOC_RESET

◈ SOC_RESET timing and Power sequence are ok.

Threshold

◈ Solution

█ Value of Capacitor and resister.

1

2

0CK226DC67A 22uF 6.3V

$0.0117

① Cap

Æ 22uF.

② Resister

Æ 100㏀.

+3.3V_AVDD

SOC_RESET

Threshold

5. GP4 LM1 SOC Power Sequence Procedure

STEP1. Setting like below. (Red box)

STEP2. Call “direct MIU Auto BIST” function from Menu.

6. Memory margin test. (DDR)

Click on the first or last page to see other 50PA4900-TE (CHASSIS:PA21A) service manuals if exist.