LG 47GA6400-UD / 47GA6450-UD (CHASSIS:LA37G) Service Manual ▷ View online

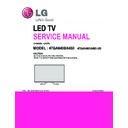

System Diagram – Focused on Digital Chip

Flexnoc ( 64 x 40 0 MHz)

AAD AFE

Demod

AFE (CHB)

AFE (1ch)

AFE (3ch)

L9A

L9D

AAD

(BTSC)

GFX

Headphone

Digital

Audio output

UART x3

I2C x12

SPI x2

DMAC

GPIO

WDG

Timer

eMMC/SD

SCI

USB x3

USB PHY

HP out

Line out

Audio L/R

LVDS RX (HS)

LVDS RX (HS)

Tuner

Audio L/R

x6 ch

Tuner

HDMI x4

DAC

SP

DIF

CVBS(CHB)

CVBS(x8ch)

HDMI RX

STP out

Sound

DSP

Speake

r

vpes

MCU

Line out

apes

Component

LVDS TX (HS)

LVDS TX (HS)

LVDS RX (HS)

LVDS TX (HS)

DAC

CVD

SC

SRAM

SMC

CI

eMMC/SD

USB x3

DVB-CI

EB

NANDC

GEM

NAND (SLC)

RGMII/RMII

DDRC

DDR3 PHY

DDRC

DDR3 PHY

DDRC

DDR3 PHY

UART x3

I2C x9

SPI x2

SCI

GPIO

JTAG

Flex

no

c (

64 x

40

0 MHz)

VDEC

core

VDEC

core

VDEC

MCU

SDCAS

DES

TDES

AES

DVB-CSA

SDIO

TP

I0

STP

I1

STP

I0

STP

O

TP

I1

SDCORE

2-channel

time-shared

TP engine

Download

TE

ADEC

VENC

DDR3 x16

DDR3 x16

Flex

no

c (

64 x

40

0 MHz)

DDR3

x16

APB Br

CA9

CA9

L2 $

1MB

DVR

MAU

SDEC

MAU

ADEC

MAU

PREP

MAU

IME

HME

QME

Core

MAU

DEBLOCK

CMC

Audio

DSP

MIC

Ex

tern

al

I

2

S

DAC

ADC

ADC

DIF

SIF

DE

TP out

TP in

(CI)

STP in

(CHB)

TS

PES

DEC

PES

DEC

PES

DEC

Upload

vpes

(thumbnail)

senc

TS

- Dual-core CPU (CA9)

- Dual-core GPU (Mail400)

- Multiple MCU (x4)

- Multiple DSP (x2)

- Multiple DDR3 Channel (x3)

Audio

TS

PREP

CVD

ES

Display

CPU/GPU

ADC

PES

DEC

PESDEC

MAU

SP

ROM

MCU

OTP

Mail400

L2 $

64KB

VP

PP

PP

AHB

Scaler(R)

IPC(R)

NR(R)

Scaler(L)

IPC(L)

NR(L)

MCU

CVE

SMUX

PRE3D

MIXED IPs (Bus)

DCO

Global clock/reset/power mgt.

with PLL + DFT inside

DDR3

PLL

DDR3

PLL

DCO

Display

PLL

CPU

PLL

CRG

+DFT

CRG

+DFT

DISP

IF

ICOD

DEC

JPEG

PNG

ENC

JPEG

SPE

VLC

MAU

AUD

PLL

LVDS TX (HS)

LVDS TX (HS)

LVDS TX (HS)

L9-3D

L9-3D

L9-3D

OSD

Right

Left

PQ(L)

PQ(R)

OSD

Scaler(sub)

2Dto3D

Flex

no

c

유첨. B0 USB 3조 대응 Mid/High모델 Power Block Diagram(Typ)

USB3

$0.055

USB2

$0.055

USB1

$0.055

Wi-Fi

$0.044

DC-DC

$0.145

DC-DC

(4A)

+ OCP

$0.24

OCP

Fixed

1.2A

OCP

1.8A

HDD Only

External

Hub Only

Hub Only

( 4:1 or 6:1)

400mA

12V

1.2A

24V

0.4A

OCP

Fixed

1.2A

* DC-DC 효율 미 고려

5V

Tol. 20%

Tol. 20%

Tol. 10%

L9A

L9D

USB2.0x3

DDR3 X 3

16

16

16

eMMC

8

HDMI1

HDMI2

HDMI3

HDMI4

HDMI

(1 Ch)

CVBS

(

8

Ch)

Audio L/R

(5 Ch)

SIF

CVBS-Out

SCART

Component

(2 Ch)

MICOM

IR

Keypad

HDMI

SW

RMII

PHY

SPIDF_OUT

Built-in WiFi

Ethernet

TXA/B

51Pin LVDS

Qwerty-R

Qwerty-Remote_R/TX

AUD

BB_TP_DATA

CHB_DATA

DAC_DATA

AAD_DATA

HSR_P/M

DTV TS

L9 Block Diagram (L9-B0 Features)

DIF

유첨. B0 Block Diagram (Features)

2D Graphic Engine

(w/ StretchBLT)

CPU

System

Demux

USB

2

.0

x

3

Channel

Browser II

Dual Full HD Display Engine

DVR Engine

Clear Voice II

Perceptual

Volume Control

Slim SPK

DivX

Sound DSP

Video Decoder

Multi-STD

HD Decoder

Audio DSP

Multi-STD

Audio Decoder

400MHz

Video Encoder

HD up to 720p

DDR3 Controller

TMDS

(1 Ch)

(1 Ch)

CVBS

(

6

Ch)

Audio L/R

(5 Ch)

SIF(1 Ch)

HS

-LVD

S

Tx

1CH

Audio

ADC

24b@48KHz

TP In(P)

DVB-CI/CI+

Digital

Audio

Output

Headphone

SPIDF

I2S

CVBS

DAC

CVBS Output

(pin sharing

w/ SCART out)

(pin sharing

w/ SCART out)

CVBS-Out

SCART

Analog

Video

Decoder

Video

3CH ADC

(11b@165MHz)

CVBS

Encoder

AXI Bus

AX

I B

u

s

Global DTV

Demodulator

(VSB/ClearQAM,

DVB-T/C)

DVB-C PLL

Xtal

Clock

(24MHz)

Clock

(24MHz)

Sw

itch

Sw

itch

Sw

itch

Line-Out

SCART

Component

Audio

DAC

HP AMP

I2S

DDR3

DDR3

DDR3

16

16

16

eMMC

RMII

PHY

USB2.0x3

DTV IF

GBB AFE

10b@30MHz

UART

x

3

I2Cx

9

SP

Ix2

G

P

IOx

60

Ethernet

MAC

SC

I

eMMC/

SDIO

DMA

Cx

8

VIC

8K

B S

R

AM

Timer

W

atc

hdog

Capture

Block

w/

LLPLL

CVBS AFE

12b@54MHz

Analog Audio AFE

10b@81MHz

Video Buffer

Analog

Audio

Decoder

Mux & HS-LVDS(x2)

Mux

ARM Cortex-A9

Dual 1GHz

w/ Dual NEON

32KB I$

32KB D$

1MB L2 $

DDR PLL

(x2)

DCO

SPLL

DPLL

CPU PLL

DDR3 PHY

8

SCART Out

Line Out

I2S

Encoder

Bluetooth

Audio

DAC

Audio

DAC

SCART Out

CHB ADC

CVBS(CHB)

Analog Video Decoder

TS In(CHB)

Micom

IR

Keypad

DDR3 Controller

DDR3 PHY

DDR3 Controller

DDR3 PHY

T

rustZon

e

Dual HD

Video Decoder

Multi-STD

HD Decoder

NR(R)

IPC(R)

Scaler (R)

PQ(R)

NR(L)

IPC(L)

Scaler (L)

PQ(L)

3D GPU

Mali-400

Quad-Core

@400MHz

HW Image Codec

(JPEG Enc/Dec,

PNG Dec)

HS

-LVD

S

Tx

FHD

FHD

OSD/

PIP

HDMI

Rx 1.4

(PHY)

HDMI

Rx 1.4

(Link)

NANDC

(EC

C)

HDMI

SW

I2S

Copyright ⓒ 2013 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Only for training and service purposes

LGE Internal Use Only