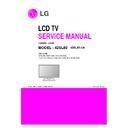

LG 42SL85-UA (CHASSIS:LA92M) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+5V_GENERAL

1/8W

75K

1%

R405

12K

1%

R407

22uF

16V

C455

Q400

1

2

3

+12V

1/10W

56K

1%

R438

MP2212DN

IC404

3

IN

2

GND

4

BS

1

FB

5

VCC

6

SW_1

7

SW_2

8

EN/SYNC

PWM_DIM

006:AF11;008:AK16

100

OPT

R473

0

R425

100K

5%

R452

1/10W

10

1%

R444

0

R430

10uF

10V

C459

+3.3V_AVDD_MPLL

10uF

6.3V

C475

BG2012B080TF

L404

+3.3V_MEMC

22uF

16V

C400

1/10W

10

1%

R409

1/10W

27K

1%

R458

MLB-201209-0120P-N2

L402

AP1117E33G-13

IC406

2

OUT

3

IN

1

ADJ/GND

10K

OPTR446

CB3216PA501E

L411

0

OPT

R416

22uF

16V

C429

CB3216PA501E

L420

0 . 1 u F

50V

C405

GND

2SC3875S(ALY)

OPT

Q403

E

B

C

1/8W

390K

1%

R460

NR8040T3R6N

3.6uH

L422

BLM18PG121SN1D

L408

1/10W

10

1%

R470

47uF

25V

C408

+3.3V_ST

0

OPT

R402

R402

0 . 1 u F

16V

OPT

C426

+24V

22uF

16V

C432

0 . 1 u F

16V

OPT

C423

POWER_EN

2SC3052

Q407

E

B

C

OPC_OUT1

008:AK16

+5V_GENERAL

2SC3052

OPT

Q404

E

B

C

0

R412

BLM18PG121SN1D

L410

0 . 1 u F

16V

16V

C477

10uF

6.3V

C448

10K

OPT

R423

L400

0 . 1 u F

16V

OPT

C416

10K

R422

47K

R454

+1.26V_MEMC

10K

OPT

R440

BLM18PG121SN1D

OPT

L414

+12V

1/10W

22K

1%

R404

0

R434

10uF

10V

10V

C468

10K

R426

0 . 1 u F

16V

16V

C419

22K

R451

0 . 1 u F

16V

16V

C478

0 . 1 u F

50V

C424

2K

R474

22uF

16V

16V

C461

0 . 1 u F

50V

OPT

C415

1N4148W_DIODES

100V

OPT

D401

68uF

35V

35V

C425

10uF

6.3V

C433

+5V_ST

+3.3V_ST

GND

22uF

25V

25V

C464

10

R443

10uF

10V

C402

GND

GND

RL_ON

006:AS32;006:AV31

0 . 1 u F

50V

50V

C422

PANEL_CTL

006:AS31

A_DIM

006:AF11

NR8040T3R6N

3.6uH

L412

ERROR_OUT

006:AB20

+5V_GENERAL

0

R465

MP2212DN

IC405

3

IN

2

GND

4

BS

1

FB

5

VCC

6

SW_1

7

SW_2

8

EN/SYNC

L419

0 . 1 u F

16V

16V

C454

+5V_EXT

22uF

16V

C404

0 . 1 u F

50V

50V

C473

1N4148W_DIODES

100V

OPT

D402

22uF

OPT

C457

CB3216PA501E

L416

1N4148W_DIODES

100V

OPT

D403

+5V_GENERAL

SC4215ISTRT

IC400

3

VIN

2

EN

4

NC_2

1

NC_1

5

NC_3

6

VO

7

ADJ

8

GND

2SC3052

Q406

E

B

C

560

R450

10

R469

0 . 1 u F

C450

POWER_ON/OFF

006:AV31

POWER_ON_DELAY

CB3216PA501E

L409

0 . 1 u F

16V

16V

C479

100

OPT

R471

BLM18PG121SN1D

L415

0 . 1 u F

C431

15pF

50V

C421

22uF

C411

+1.8V_MEMC

10uF

C458

10uF

OPT

C445

100uF

16V

C412

FM20020-24

P400

19

NC

14

12V

9

5.2V

4

GND

18

24V

13

12V

8

5.2V

3

GND

17

12

GND

7

5.2V

2

PWR ON

16

GND

11

GND

6

GND

1

NC

20

15

GND

10

5.2V

5

GND

21

22

23

NC

24

PWM_DIM

25

10K

OPT

R424

1uF

16V

C436

+3.3V_FE

10uF

10V

C460

APE8953MP

IC403

3

VOUT_1

2

FB

4

VOUT_2

1

GND

5

VIN

6

VCNTL

7

POK

8

EN

100uF

16V

C407

OPT

C437

4.7K

R427

L405

T o B e E x t i n c t e d

+3.3V

1/10W

30K

1%

R456

0 . 4 7 u F

16V

OPT

C406

0 . 1 u F

16V

16V

C470

+3.3V_ST

1uF

10V

C471

4 . 7 u F

25V

25V

C442

MP2212DN

IC402

3

IN

2

GND

4

BS

1

FB

5

VCC

6

SW_1

7

SW_2

8

EN/SYNC

+3.3V

10uF

6.3V

C447

CB3216PA501E

L418

22uF

16V

C428

1uF

16V

C420

1/10W

18K

1%

R439

3.3K

R400

22uF

16V

OPT

C401

BLM18PG121SN1D

L423

10K

OPT

R429

GND

0 . 1 u F

50V

OPT

C413

22uF

16V

C451

4 . 7 u F

6.3V

OPT

OPT

C439

1uF

35V

35V

C430

22uF

16V

C472

10K

OPT

R445

R445

22uF

OPT

C417

1/10W

10K

R413

GND

4.7K

R401

1/10W

10

1%

R463

POWER_EN

006:AR30;004:AL8;004:AN20;005:AG7

NR8040T3R6N

3.6uH

L406

0

R403

CB3216PA501E

L417

1/10W

10K

R464

0

R442

6.8K

OPT

R415

0 . 0 1 u F

25V

C444

+5V_ST

10K

R435

20K

R421

120K

OPT

R428

BG2012B080TF

L403

+5V_ST

CB3216PA501E

L421

120K

OPT

R436

22K

R447

MP2212DN

IC401

3

IN

2

GND

4

BS

1

FB

5

VCC

6

SW_1

7

SW_2

8

EN/SYNC

22uF

16V

C474

+3.3V

0 . 1 u F

16V

OPT

C414

10K

OPT

OPT

R432

+5V_EXT

0

R433

0 . 1 u F

16V

16V

C469

3225

22uF

16V

16V

C476

1uF

25V

C409

0 . 1 u F

16V

16V

C453

+5V

+3.3V_ST

10K

R468

POWER_EN

006:AR30;004:X20;004:AL8;005:AG7

22uF

OPT

C434

+5V_GENERAL

33K

OPT

OPT

R417

+5V_GENERAL

CB3216PA501E

L401

10uF

6.3V

C446

100

R414

0.1uF

C449

12V_TCON

0 . 1 u F

16V

16V

C403

1uF

25V

25V

C456

+1.8V_DDR

0

R431

+3.3V_ST

1uF

10V

C440

47K

R455

2SC3052

Q405

E

B

C

10

R462

+3.3V_ST

10

R408

GND

BLM18PG121SN1D

L413

INV_CTL

006:AS32

+5V_ST

+5V_ST

10K

OPT

R472

1uF

10V

10V

C443

22uF

16V

OPT

C465

2SC3052

OPT

Q402

E

B

C

1/8W

300K

1%

R461

22uF

C452

0 . 1 u F

50V

50V

C441

3.3K

R418

10uF

6.3V

C435

9.1K

1%

1%

R406

0

R420

+12V

1uF

16V

C466

1uF

50V

OPT

C410

0 . 1 u F

16V

16V

C463

100

OPT

R453

1N4148W_DIODES

100V

OPT

D400

0 . 1 u F

50V

50V

C467

+5V

NR8040T3R6N

3.6uH

L424

10K

R437

+5V_ST

2SC3052

Q401

E

B

C

+1.8V_MEMC

1K

R448

0

OPT

R419

+12V

1/8W

24K 1%

R411

68uF

35V

35V

C427

10K

R441

0 . 1 u F

16V

16V

C462

10K

R449

SI4925BDY

Q408

3

S2

2

G1

4

G2

1

S1

5

D2_1

6

D2_2

7

D1_1

8

D1_2

22uF

16V

C418

+1.26V_VDDC

4 . 7 u F

6.3V

OPT

OPT

C438

1/10W

10K

OPT

R410

1/10W

33K

1%

R459

OPC_OUT2

008:AK17

82K

R457

R457

13K

1%

R467

L407

T o B e E x t i n c t e d

68K

1%

R466

560pF

50V

50V

OPT

C480

560pF

50V

50V

OPT

C482

100pF

50V

50V

C483

390pF

50V

50V

C481

4

14

SL80-UX

POWER

0 9 . 0 2 . 2 5

C l o s e t o I C

R1

$ 0 . 0 7

24V

V o u t = 0 . 8 * ( 1 + R 1 / R 2 )

C OUT

C l o s e t o I C

2 2 0 u F = = > 1 0 0 u F * 2 + 2 2 u F f o r D e p t h

A.DIM

C IN

Placed on SMD-TOP

V o u t = 0 . 8 * ( 1 + R 1 / R 2 )

C l o s e t o I C

C l o s e t o I C

R2

FROM LIPS & POWER B/D

R1

C IN

R2

$ 0 . 0 7

Placed on SMD-TOP

450 mA

+1.8V_MEMC for URSA DDR

P I R e s u l t

415 mA @85% efficiency

V o u t = 0 . 8 * ( 1 + R 1 / R 2 )

C l o s e t o I C

R1

+5V_EXT

$ 0 . 2 4

Placed on SMD-TOP

+3.3V

INV ON

+ 1 . 8 V f o r S a t u r n 5 D D R

C l o s e t o I C

R 1 / R 2 : 2 7 K / 2 0 K = > V o u t = 1 . 8 8

R2

400 mA + 600 mA

Placed on SMD-TOP

R 1 / R 2 : 1 2 K / 9 . 1 K = > V o u t = 1 . 8 5

Placed on SMD-TOP

Placed on SMD-TOP

R2

R 1 / R 2 : 1 5 K / 1 2 K = > V o u t = 1 . 8 0

C OUT

R 1 / R 2 = 1 2 K / 2 0 K = > V o u t = 1 . 2 8

4.9A 0.0150OHM 34MHZ

MAX 3A

+ 1 . 2 6 C o r e f o r S a t u r n 5

+ 1 . 2 6 C o r e f o r U R S A

A b o u t 1 . 8 4 V

R1

S t a n d - b y + 3 . 3 V

R1

4.9A 0.0150OHM 34MHZ

Placed on SMD-TOP

R2

V o u t = 0 . 8 * ( 1 + R 1 / R 2 )

3A, DCR=0.025 ohm

+5V_+12V

Placed on SMD-TOP

Placed on SMD-TOP

C l o s e t o I C

Err OUT

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

4.7K

R516

UCA36AL

T u n e r - S a n y o

TU500-*1

14

IF_AGC

13

D_IF2

5

NC_3[RF_AGC]

12

D_IF1

11

NC_5

2

NC_2

19

VIDEO

18

NC_7

10

AS

4

+5V[MAIN]

1

NC_1

17

NC_6[AFT]

9

SCL

8

SDA

3

GND_1

16

S I F

7

GND_2

6

NC_4[VT]

15

+5V[VIF]

20

SHIELD

0 . 1 u F

50V

50V

C531

0 . 1 u F

50V

50V

C551

100uF

16V

C550

+5V_TU

0 . 1 u F

50V

C535

+5V_EXT

1uF

10V

10V

C552

36pF

50V

IF_LC_Filter

C528

OPT

R546

0 . 0 4 7 u F

50V

OPT

C512

MLB-201209-0120P-N2

L509

0

I F _ S h o r t

R523-*1

VSB_RESET

0

R501

0 . 1 u F

16V

C500

22 R548

100

R528

+1.2V_DVDD_PVSB

J P 5 0 0

0 . 1 u F

50V

50V

C539

0.1uF

50V

C525

I F _ P

0 . 0 1 u F

25V

C504

500

OPT

L511

+3.3V_AVDD_PVSB

3216

10uF

16V

16V

C534

+12V

100uF

16V

C555

20K

R549

100

OPT

R541

1/16W

100

AR500

OPT

R532

IF_AGC

0 . 1 u F

16V

C502

0 . 1 u F C538

4.7K

R512

0 . 1 u F

50V

C540

100

OPT

R502

+3.3V_AVDD_PVSB

22

R506

1M

R539

27pF

50V

50V

C548

27pF

50V

OPT

C520

+3.3V_AVDD_PVSB

0 . 1 u F

C521

0 . 1 u F

50V

50V

C544

100pF

50V

C507

OPT

C553

0 . 1 u F

50V

C543

SC156515M-1.8TR

IC504

2

VIN

1

EN

3

GND

5

ADJ

4

VO

OPT

R545

5.1K

OPT

R534

27pF

50V

C546

J P 5 0 2

0 . 0 1 u F

25V

25V

C524

AS7809DTRE1

IC500

2

GND

3

OUTPUT

1

INPUT

OPT

R533

3216

10uF

16V

C532

0 . 0 1 u F

C542

0 . 1 u F

50V

50V

C537

100

R527

47uF

16V

16V

C519

TS_CLK

+3.3V_PVSB

+1.2V_PVSB

20K

R538

4.7K

R540

470

PV

R535

0 . 1 u F

50V

C508

220nHI F _ L C _ F i l t e r

R524

+3.3V_DVDD_PVSB

ISA1530AC1

Q501

E

B

C

CB3216PA501E

L510

TS_VALID

0

OPT

R510

+5V_TU

FE_DEMOD_SCL

+3.3V_PVSB

LGDT3305

IC502

1

NC_1

2

VINA2

3

VINA1

4

INCAP

5

VSSAAD10A

6

I2CSEL

7

ANTCON

8

VDD_1

9

I2CRPT_SCL

10

I2CRPT_SDA

11

IFOUT

12

RFOUT

13

TPERR

14

VDD33_1

15

TPVALID

16

TPDATA[0]

17

VSS33_1

18

TPDATA[1]

19

TPDATA[2]

20

TPDATA[3]

21

TPDATA[4]

22

TPDATA[5]

23

TPDATA[6]

24

TPDATA[7]

25

TPCLK

26

TPSOP

27

NIRQ

28

SDA

29

VDD33_2

30

SCL

31

VSS_1

32

VDD_2

33

VSS_2

34

VSS33_2

35

PLLAVDD

36

PLLAVSS

37NRST

38OPM

39VDD33_3

40NC_2

41VSS33_3

42XTALI

43XTALO

44VSS_3

45XM

46VDD_3

47VSSDAD10

48VCCAAD10A

J P 5 0 1

25MHz

X500

+3.3V_FE

VSB_CTRL

0

R519

22

R505

CB3216PA501E

L507

FE_TUNER_SDA

POWER_EN

006:AR30;004:X20;004:AL8;004:AN20

0

OPT

R500

ISA1530AC1

Q500

E

B

C

220uF

16V

16V

C522

0 . 1 u F

50V

50V

C558

0 . 0 1 u F

50V

C513

100uF

16V

C556

0 . 3 3 u F

16V

C505

PV

LD500

FE_VMAIN

006:C23

36pF

50V

IF_LC_Filter

C527

VCOMO

006:C23

0

OPT

R542

0 . 1 u F

C533

+1.2V_PVSB

SC4215ISTRT

IC503

3

VIN

2

EN

4

NC_2

1

NC_1

5

NC_3

6

VO

7

ADJ

8

GND

10K

R508

KIA78R05F

IC501

1

VIN

2

VC

3

VOUT

4

NC

5

GND1

6

GND2

CM2012F6R8KT

6.8uH

L502

IF_P

0

R531

270

R515

FE_TUNER_SCL

+5V_TU

0 . 1 u F

50V

C506

100

AR501

OPT

C554

100

R530

0

R511

0 . 1 u F

50V

50V

C557

10uF

10V

10V

C514

270nH

L506

8.2K

R552

IF_N

82pF

50V

50V

C526

TDVW-H103F

Tuner-LGIT

TU500

14

IF_AGC

13

D I F [ - ]

5

RF_AGC

12

D I F [ + ]

11

NC_3

2

NC_2

19

VIDEO

18

AUDIO

10

AS

4

+B1

1

NC_1

17

NC_4

9

CLOCK

8

DATA

3

GND_1

16

S I F

7

GND_2

6

NC[VT]

15

+B2

20

SHIELD

TS_DATA[0-7]

+3.3V_DVDD_PVSB

GND

100

AR502

0 . 1 u F

16V

16V

OPT

C511

0 . 1 u F

C536

220uF

16V

16V

C517

+3.3V_DVDD_PVSB

+3.3V_PVSB

15K

R551

0 . 0 1 u F C541

0

R520

3216

10uF

16V

C530

1K

R526

2 . 2 u F

16V

16V

C547

500

L508

270

R514

IF_AGC

100pF

50V

50V

C510

22 R547

BG2012B800

L500

IF_N

OPT

R509

2 . 2 u F

16V

16V

C545

100uF

16V

16V

C501

0

5%

1/4W

R525

+5V_TU

0

I F _ S h o r t

R524-*1

470

R513

2.2K

OPT

R504

1K

R529

27pF

50V

50V

OPT

C523

FE_TUNER_SDA

TS_VALID

CM3216F100KE

10uH

L503

10K

R550

100uF

16V

C503

FE_TUNER_SCL

TS_SYNC

TS_SYNC

0

R517

TS_CLK

0

R518

+1.2V_DVDD_PVSB

0 . 1 u F

50V

OPT

C516

12K

R507

FE_DEMOD_SDA

FE_SIF

006:V30

1uF

16V

C549

+5V_TU

47K

R544

1N4148W

D500

220nHI F _ L C _ F i l t e r

R523

10K

OPT

R503

1K

R543

47pF

C529

TS_DATA[2]

TS_DATA[1]

TS_DATA[7]

TS_DATA[5]

TS_DATA[6]

TS_DATA[0-7]

TS_DATA[3]

TS_DATA[4]

TS_DATA[0]

0 9 . 0 2 . 2 5

5

SL80-UX

14

TUNER

VSB +3.3V B+ BLOCK

VSS33

PLLAVDD

T h e v a l u e o f c o i l & c a p ’ c o u l d b e c h a n g e d t o o p t i m i z e d e a c h

M S t a r A p p l i c a t i o n

VSB +1.0V B+ BLOCK

TPDATA[0]

VDD

O p t i o n f o r F M R e j e c t i o n

TPVALID

VSS33

R2

JTAG

SDA

R1

VDD33

TPCLK

TPDATA[7]

SCL

TPERR

VDD33

TPDATA[6]

VSS

TPDATA[5]

VROA

TPDATA[4]

ANTCON

TPDATA[3]

INCAP

TPDATA[2]

VDD

TPDATA[1]

RF OUT

XTALI

C l o s e t o t u n e r

VSS

VINA2

( I 2 C C h a n n e l 6 )

OPM

I2CSEL

NRST

SLIM_SCAN

XTALO

VSS33

VINA1

XM

VDD

I2CRPT_SCL

NIRQ

VCCAAD10A

I2CRPT_SDA

VSS

VSSAD10

IF OUT

TPSOP

M S t a r A p p l i c a t i o n

VDD33

VSSAAD10A

PLLAVSS

V 0 = 0 . 8 ( R 1 + R 2 ) / R 2

UNER

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

56

R12

56

R33

56

R27

56

AR13

0.1uF

C20

56

AR10

0.1uF

C24

56

R41

33

R8

0 . 1 u F

C22

0.1uF

C4

56

R14

+1.8V_S_DDR

+1.8V_S_DDR

0.1uF

C6

0.1uF

C10

56

R37

0.1uF

C35

56

AR12

0.1uF

C31

56

R7

56

AR9

10uF

C23

0.1uF

C12

0.1uF

C37

0.1uF

C27

56

R39

0.1uF

C32

56

R10

56

R36

56

AR3

56

R20

56

AR1

0.1uF

C29

10uF

C13

56

R30

56

AR7

56

R22

56

AR2

150

OPT

R45

56

AR14

0.1uF

C9

56

R19

0.1uF

C34

1000pF

C2

10uF

C3

56

R17

1000pF

C18

56

R6

56

R43

0.1uF

C8

0.1uF

C38

56

AR4

33

R9

+1.8V_S_DDR

0.1uF

C5

150

OPT

R2

56

R42

56

AR8

56

R40

56

R16

10uF

C30

HYB18TC512160B2F-2.5

IC2

QIMONDA

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

+1.8V_S_DDR

+1.8V_S_DDR

0 . 1 u F

C1

56

AR6

1K

1

%

R23

56

R11

56

R21

+1.8V_S_DDR

0.1uF

C25

33

R31

1K

1%

R44

56

R35

0.1uF

C39

0.1uF

C41

56

AR5

0.1uF

C11

56

R18

+1.8V_DDR

+1.8V_S_DDR

33

R32

1K

1

%

R5

1000pF

C42

56

AR11

0.1uF

C7

56

R38

56

R15

0.1uF

C36

+1.8V_S_DDR

1K

1%

R4

0.1uF

C15

1K

1

%

R24

0.1uF

C19

BLM18PG121SN1D

L1

56

R34

0 . 1 u F

C40

0.1uF

C14

56

R13

56

R28

1K

1%

R47

0.1uF

C33

0.1uF

C21

0.1uF

C16

0.1uF

C43

0.1uF

C17

56

R29

HYB18TC1G160C2F-2.5

IC1

QIMONDA

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

BA2

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC4

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC5

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

56

R1

0

R48

OPT

0

R49

OPT

0

R50

OPT

+1.8V_S_DDR

IC600

LGE3369A (Saturn6 Non RM)

B_DDR2_A0

T26

B_DDR2_A1

AF26

B_DDR2_A2

T25

B_DDR2_A3

AF23

B_DDR2_A4

T24

B_DDR2_A5

AE23

B_DDR2_A6

R26

B_DDR2_A7

AD22

B_DDR2_A8

R25

B_DDR2_A9

AC22

B_DDR2_A10

AD23

B_DDR2_A11

R24

B_DDR2_A12

AE22

B_DDR2_BA0

AC23

B_DDR2_BA1

AC24

B_DDR2_BA2

AB22

B_DDR2_MCLK

V25

/B_DDR2_MCLK

V24

B_DDR2_CKE

AB23

B_DDR2_ODT

U26

/B_DDR2_RAS

U25

/B_DDR2_CAS

U24

/B_DDR2_WE

AB24

B_DDR2_DQS0

AB26

B_DDR2_DQS1

AA26

B_DDR2_DQM0

AC25

B_DDR2_DQM1

AC26

B_DDR2_DQSB0

AB25

B_DDR2_DQSB1

AA25

B_DDR2_DQ0

W25

B_DDR2_DQ1

AE26

B_DDR2_DQ2

W24

B_DDR2_DQ3

AF24

B_DDR2_DQ4

AF25

B_DDR2_DQ5

V26

B_DDR2_DQ6

AE25

B_DDR2_DQ7

W26

B_DDR2_DQ8

Y26

B_DDR2_DQ9

AD25

B_DDR2_DQ10

Y25

B_DDR2_DQ11

AE24

B_DDR2_DQ12

AD26

B_DDR2_DQ13

Y24

B_DDR2_DQ14

AD24

B_DDR2_DQ15

AA24

A_MVREF

D15

A_DDR2_A0

C13

A_DDR2_A1

A22

A_DDR2_A2

B13

A_DDR2_A3

C22

A_DDR2_A4

A13

A_DDR2_A5

A23

A_DDR2_A6

C12

A_DDR2_A7

B23

A_DDR2_A8

B12

A_DDR2_A9

C23

A_DDR2_A10

B22

A_DDR2_A11

A12

A_DDR2_A12

A24

A_DDR2_BA0

C24

A_DDR2_BA1

B24

A_DDR2_BA2

D24

A_DDR2_MCLK

B14

/A_DDR2_MCLK

A14

A_DDR2_CKE

D23

A_DDR2_ODT

D14

/A_DDR2_RAS

D13

/A_DDR2_CAS

D12

/A_DDR2_WE

D22

A_DDR2_DQS0

B18

A_DDR2_DQS1

C17

A_DDR2_DQM0

C18

A_DDR2_DQM1

A19

A_DDR2_DQSB0

A18

A_DDR2_DQSB1

B17

A_DDR2_DQ0

B15

A_DDR2_DQ1

A21

A_DDR2_DQ2

A15

A_DDR2_DQ3

B21

A_DDR2_DQ4

C21

A_DDR2_DQ5

C14

A_DDR2_DQ6

C20

A_DDR2_DQ7

C15

A_DDR2_DQ8

C16

A_DDR2_DQ9

C19

A_DDR2_DQ10

B16

A_DDR2_DQ11

B20

A_DDR2_DQ12

A20

A_DDR2_DQ13

A16

A_DDR2_DQ14

B19

A_DDR2_DQ15

A17

H5PS5162FFR-S6C

I C 2 - * 1

HYNIX

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

HY5PS1G1631CFP-S6

I C 1 - * 1

HYNIX

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

BA2

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

BDDR2_D[13]

SDDR_D[11]

BDDR2_D[8]

TDDR_A[0-12]

BDDR2_A[4]

BDDR2_A[5]

SDDR_DQM0_P

TDDR_A[7]

TDDR_D[6]

ADDR2_A[6]

SDDR_BA[1]

SDDR_D[10]

BDDR2_A[2]

BDDR2_A[10]

SDDR_D[7]

ADDR2_D[1]

SDDR_A[9]

TDDR_D[14]

TDDR_DQS0_P

BDDR2_A[11]

BDDR2_D[2]

ADDR2_D[0]

BDDR2_D[8]

BDDR2_D[4]

BDDR2_A[12]

ADDR2_A[12]

TDDR_A[1]

TDDR_D[7]

ADDR2_D[5]

SDDR_D[8]

BDDR2_D[0]

ADDR2_D[11]

TDDR_A[1]

TDDR_A[0]

TDDR_D[2]

TDDR_A[3]

BDDR2_D[15]

ADDR2_A[7]

BDDR2_A[5]

ADDR2_A[8]

SDDR_D[14]

ADDR2_A[0]

TDDR_D[15]

TDDR_DQS1_N

TDDR_BA[1]

BDDR2_D[6]

SDDR_A[11]

ADDR2_D[10]

BDDR2_D[11]

SDDR_D[9]

TDDR_D[10]

SDDR_A[2]

SDDR_A[7]

TDDR_D[0]

SDDR_D[12]

SDDR_D[3]

TDDR_D[4]

TDDR_D[8]

SDDR_D[9]

ADDR2_D[6]

SDDR_D[5]

BDDR2_A[0-12]

ADDR2_D[5]

ADDR2_D[13]

SDDR_A[3]

SDDR_A[2]

BDDR2_D[0-15]

BDDR2_D[15]

ADDR2_D[7]

/TDDR_CAS

TDDR_DQM0_P

ADDR2_D[2]

ADDR2_D[1]

TDDR_A[10]

TDDR_MCLK

SDDR_A[4]

TDDR_D[13]

ADDR2_D[9]

SDDR_A[0]

ADDR2_A[8]

TDDR_A[11]

TDDR_D[3]

TDDR_BA[0]

BDDR2_A[9]

TDDR_D[13]

ADDR2_D[11]

BDDR2_A[9]

SDDR_D[10]

BDDR2_D[2]

ADDR2_D[10]

ADDR2_A[2]

SDDR_A[8]

TDDR_D[12]

TDDR_D[1]

TDDR_A[7]

SDDR_A[12]

ADDR2_D[3]

SDDR_A[7]

TDDR_A[3]

BDDR2_D[10]

SDDR_D[13]

TDDR_A[8]

ADDR2_A[10]

TDDR_D[11]

SDDR_D[8]

SDDR_A[11]

SDDR_D[2]

BDDR2_A[3]

ADDR2_D[0]

TDDR_DQS1_P

SDDR_A[5]

TDDR_A[2]

SDDR_D[14]

TDDR_D[8]

TDDR_A[6]

SDDR_A[10]

ADDR2_A[11]

BDDR2_D[14]

TDDR_D[12]

ADDR2_A[4]

/TDDR_WE

TDDR_D[9]

TDDR_A[4]

SDDR_D[0-15]

ADDR2_A[5]

SDDR_D[5]

ADDR2_A[9]

SDDR_DQS0_P

TDDR_D[2]

TDDR_A[0]

ADDR2_D[4]

BDDR2_A[10]

ADDR2_A[7]

SDDR_D[12]

SDDR_D[0]

BDDR2_A[8]

TDDR_A[2]

SDDR_D[2]

SDDR_D[0]

ADDR2_D[4]

TDDR_A[6]

BDDR2_D[6]

BDDR2_D[3]

BDDR2_A[4]

TDDR_D[5]

TDDR_A[4]

TDDR_CKE

BDDR2_A[1]

ADDR2_A[12]

SDDR_A[3]

SDDR_A[6]

ADDR2_D[0-15]

TDDR_D[10]

ADDR2_A[1]

TDDR_A[12]

SDDR_D[13]

SDDR_D[11]

SDDR_D[4]

TDDR_A[9]

ADDR2_A[0]

/SDDR_CAS

BDDR2_A[1]

BDDR2_D[7]

BDDR2_D[5]

SDDR_A[8]

/TDDR_MCLK

BDDR2_D[11]

SDDR_D[6]

BDDR2_A[6]

SDDR_DQS0_N

ADDR2_A[5]

ADDR2_D[14]

BDDR2_D[7]

TDDR_A[8]

ADDR2_D[15]

ADDR2_A[11]

BDDR2_A[0]

TDDR_D[0]

ADDR2_D[8]

TDDR_D[14]

BDDR2_A[8]

TDDR_D[7]

TDDR_A[10]

ADDR2_D[9]

SDDR_D[1]

SDDR_A[6]

ADDR2_A[6]

ADDR2_D[3]

BDDR2_D[5]

BDDR2_D[10]

TDDR_A[5]

TDDR_A[12]

ADDR2_A[2]

ADDR2_A[4]

BDDR2_A[7]

BDDR2_D[13]

SDDR_A[4]

ADDR2_D[8]

ADDR2_D[12]

SDDR_A[5]

TDDR_D[11]

ADDR2_MCLK

TDDR_D[9]

TDDR_D[6]

ADDR2_A[1]

SDDR_D[6]

TDDR_D[5]

SDDR_A[12]

BDDR2_D[9]

BDDR2_A[6]

BDDR2_A[7]

SDDR_D[1]

ADDR2_D[14]

ADDR2_D[12]

TDDR_D[4]

BDDR2_D[3]

SDDR_A[0-12]

BDDR2_D[0]

BDDR2_A[11]

TDDR_D[3]

SDDR_D[3]

BDDR2_D[4]

BDDR2_A[12]

BDDR2_A[0]

/SDDR_RAS

ADDR2_BA[1]

SDDR_A[10]

SDDR_D[15]

ADDR2_A[10]

TDDR_DQS0_N

SDDR_A[1]

ADDR2_A[9]

TDDR_D[1]

ADDR2_A[0-12]

ADDR2_BA[0]

SDDR_D[7]

ADDR2_D[13]

BDDR2_D[9]

SDDR_A[9]

TDDR_A[11]

SDDR_BA[0]

BDDR2_D[12]

SDDR_A[1]

ADDR2_A[3]

ADDR2_D[15]

BDDR2_D[12]

SDDR_A[0]

TDDR_D[0-15]

SDDR_D[4]

/TDDR_RAS

ADDR2_A[3]

BDDR2_D[1]

BDDR2_A[2]

BDDR2_D[1]

ADDR2_D[2]

BDDR2_A[3]

TDDR_DQM1_P

TDDR_A[9]

SDDR_D[15]

TDDR_A[5]

ADDR2_D[6]

TDDR_D[15]

ADDR2_D[7]

BDDR2_D[14]

/SDDR_WE

SDDR_DQS1_P

SDDR_DQM1_P

SDDR_DQS1_N

SDDR_CKE

/SDDR_CK

SDDR_CK

ADDR2_BA[2]

SDDR_BA[2]

SDDR_ODT

DDR2 1.8V By CAP - Place these Caps near Memory

DDR2

15

SL80-UX

6

0 9 . 0 2 . 2 5

Click on the first or last page to see other 42SL85-UA (CHASSIS:LA92M) service manuals if exist.