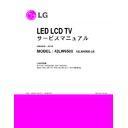

LG 42LW6500-JA (CHASSIS:LE13E) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

BCM-POWER

10/11/25

13 120

BCM-JAPAN

C1088

0.01uF

0.01uF

C1071

0.01uF

0.01uF

C1081

10uF

C1062

1000pF

1000pF

C1052

4.7uF

4.7uF

C1058

4.7uF

4.7uF

C1060

0.1uF

0.1uF

D1.2V

C1055

0.1uF

0.1uF

C1077

0.1uF

0.1uF

C1082

0.1uF

0.1uF

C1078

4.7uF

4.7uF

C1099

0.1uF

0.1uF

C1068

0.01uF

0.01uF

C1079

0.01uF

0.01uF

C1080

1000pF

1000pF

C1069

1000pF

1000pF

C1056

1000pF

1000pF

C1083

4.7uF

4.7uF

C1057

1000pF

1000pF

D1.8V

C1095

0.01uF

0.01uF

C1072

0.1uF

0.1uF

C1075

0.1uF

0.1uF

C1066

0.1uF

0.1uF

C1054

0.01uF

0.01uF

D1.8V

C1065

1000pF

1000pF

C1073

1000pF

1000pF

C1098

10uF

C1053

0.1uF

0.1uF

C1051

1000pF

1000pF

C1094

0.1uF

0.1uF

C1059

0.1uF

0.1uF

C1064

4.7uF

4.7uF

C1085

0.01uF

0.01uF

C1063

0.01uF

0.01uF

L1007

BLM18PG121SN1D

C1093

0.01uF

0.01uF

C1084

4.7uF

4.7uF

C1302

0.1uF

C1076

4.7uF

4.7uF

C1097

0.01uF

0.01uF

C1067

1000pF

1000pF

D1.2V

C1092

1000pF

1000pF

D1.8V

C1074

0.01uF

0.01uF

C1089

1000pF

1000pF

C1061

1000pF

1000pF

C1091

4.7uF

4.7uF

C1301

0.01uF

0.01uF

C1086

4.7uF

4.7uF

C1070

0.1uF

0.1uF

C1087

10uF

D1.2V

IC900

LGE3558

EAN61546201

VDDC_1

H8

VDDC_2

J8

VDDC_3

K8

VDDC_4

L8

VDDC_5

M8

VDDC_6

N8

VDDC_7

P8

VDDC_8

R8

VDDC_9

H9

VDDC_10

H10

VDDC_11

H11

VDDC_12

H12

VDDC_13

H13

VDDC_14

H14

VDDC_15

H15

VDDC_16

H16

VDDC_17

H17

VDDC_18

H18

VDDC_19

H19

VDDC_20

J19

VDDC_21

K19

VDDC_22

L19

VDDC_23

M19

VDDC_24

N19

VDDC_25

P19

VDDC_26

R19

VDDC_27

T19

VDDC_28

U19

VDDC_29

V19

AGC_VDDO

V24

VDDO_1

W11

VDDO_2

W12

VDDO_3

W17

VDDO_4

W18

VDDO_5

E26

VDDO_6

L26

VDDO_7

T26

DDRV_1

A9

DDRV_2

G9

DDRV_3

G11

DDRV_4

G13

DDRV_5

A14

DDRV_6

G15

DDRV_7

G17

DDRV_8

A19

DDRV_9

G19

IC900

LGE3558

EAN61546201

DVSS_1

T6

DVSS_2

J7

DVSS_3

K7

DVSS_4

L7

DVSS_5

M7

DVSS_6

T7

DVSS_7

AA7

DVSS_8

T8

DVSS_10

AA8

DVSS_11

D9

DVSS_12

W9

DVSS_13

Y9

DVSS_14

K10

DVSS_15

L10

DVSS_16

M10

DVSS_17

N10

DVSS_18

P10

DVSS_19

R10

DVSS_20

T10

DVSS_21

U10

DVSS_22

W10

DVSS_23

A11

DVSS_24

K11

DVSS_25

L11

DVSS_26

M11

DVSS_27

N11

DVSS_28

P11

DVSS_29

R11

DVSS_30

T11

DVSS_31

U11

DVSS_32

D12

DVSS_33

G12

DVSS_34

K12

DVSS_35

L12

DVSS_36

M12

DVSS_37

N12

DVSS_38

P12

DVSS_39

R12

DVSS_40

T12

DVSS_41

U12

DVSS_42

K13

DVSS_43

L13

DVSS_44

M13

DVSS_45

N13

DVSS_46

P13

DVSS_47

R13

DVSS_48

T13

DVSS_49

U13

DVSS_50

G14

DVSS_51

K14

DVSS_52

L14

DVSS_53

M14

DVSS_54

N14

DVSS_55

P14

DVSS_56

R14

DVSS_57

T14

DVSS_58

U14

DVSS_59

K15

DVSS_60

L15

DVSS_61

M15

DVSS_62

N15

DVSS_63

P15

DVSS_64

R15

DVSS_65

T15

DVSS_66

U15

DVSS_67

W15

DVSS_68

A16

DVSS_69

G16

DVSS_70

K16

DVSS_71

L16

DVSS_72

M16

DVSS_73

N16

DVSS_74

P16

DVSS_75

R16

DVSS_76

T16

DVSS_77

U16

DVSS_78

D17

DVSS_79

K17

DVSS_80

L17

DVSS_81

M17

DVSS_82

N17

DVSS_83

P17

DVSS_84

R17

DVSS_85

T17

DVSS_86

U17

DVSS_87

AA17

DVSS_88

AB17

DVSS_89

G18

DVSS_91

AB18

DVSS_92

AC18

DVSS_95

D20

DVSS_96

G20

DVSS_97

H20

DVSS_98

J20

DVSS_99

K20

DVSS_100

L20

DVSS_101

M20

DVSS_102

N20

DVSS_103

P20

DVSS_104

R20

DVSS_105

U20

DVSS_106

A21

DVSS_107

N21

DVSS_90

V21

DVSS_93

W24

DVSS_94

F26

DVSS_9

K26

D3.3V

D3.3V

D3.3V

D3.3V

C1090

33uF

C1096

33uF

C1300

33uF

BCM3549 DDR 1.8V By CAP : Place near to BCM3549

JANG JAE HO

BCM3558 POWER

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

R3506

33

R3507

33

L_VS

SDA1_3.3V

SCL1_3.3V

R3508

33

M3_SCLK

M2_SCLK

M3_MOSI

M1_SCLK

M2_MOSI

M1_MOSI

M0_SCLK

M0_MOSI

R3509

10K

OPT

10K

OPT

R3510

10K

10K

+3.3V_FRC

P3503

12507WR-08L

1

2

3

4

5

6

7

8

9

R3513

4.7K

4.7K

R3504

0

LPB_42/47/55

R3505

0

LPB_42/47/55

35

NON USED L/DIMMING

(FOR EDGE_LED)

(FOR EDGE_LED)

LOCAL DIMMING

BCM35230

58

Interface block

[To LED DRIVER]

PLACE SERIAL RESISTORS CLOSE TO URSA4

2010. 10. 20

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

FRC_DQU[5]

FRC_DQU[0]

FRC_DQL[0]

FRC_DQU[7]

FRC_A[0]

FRC_DQL[1]

FRC_DQU[4]

FRC_A[6]

FRC_A[10]

FRC_A[4]

FRC_DQL[5]

FRC_A[2]

FRC_A[8]

FRC_A[9]

FRC_A[7]

FRC_A[1]

FRC_A[5]

FRC_A[3]

FRC_DQU[6]

FRC_A[11]

FRC_DQL[2]

FRC_A[12]

FRC_DQU[2]

FRC_A[13]

FRC_DQL[4]

FRC_DQL[3]

FRC_DQU[1]

FRC_DQL[7]

FRC_DQU[3]

FRC_DQL[6]

SPI_DO

AVDD_LVDS_3.3V

+1.26V_FRC

PWM1

C5208

0.1uF

0.1uF

R5210

10K

OPT

AVDD33

DVDD_DDR_1V

AVDD_PLL

R5211

10K

R5217

10K

OPT

R5231

100

R5226

100

C5240

0.1uF

AVDD_PLL

SPI_SCLK

VDDC10

C5220

0.1uF

0.1uF

C5217

0.1uF

0.1uF

C5238

0.1uF

0.1uF

SCL1_+3.3V_URSA

VDDC10

C5210

22uF

10V

22uF

10V

2D/3D_CTL

C5239

0.1uF

0.1uF

+3.3V_FRC

C5233

0.1uF

0.1uF

R5212

10K

OPT

R5213

10K

LVDS_EXT_URSA5

FRC_DQSL

R5242

33

URSA_MODEL_OPT_1

AVDD33

C5227

0.1uF

0.1uF

C5207

0.1uF

0.1uF

C5201

0.1uF

0.1uF

SPI_DI

C5232

0.1uF

0.1uF

R5251

33

R5208

10K

OPT

R5225

100

+1.5V_FRC_DDR

R5237

1M

R5215

10K

OPT

VDD33

C5225

0.1uF

0.1uF

DVDD_DDR_1V

SPI_SCLK

R5245

33

FRC_CASB

C5231

0.1uF

0.1uF

+3.3V_FRC

R5204

10K

OPT

+3.3V_FRC

FRC_MCLK

P5201

12507WR-04L

URSA5_DEBUG

1

2

3

4

5

SDA1_+3.3V_URSA

M1_SCLK

R5209

10K

OPT

SDA1_+3.3V_DB

C5205

0.1uF

0.1uF

FRC_DQL[0-7]

+3.3V_FRC

FRC_DQSU

URSA_MODEL_OPT_0

L5205

CIC21J501NE

FRC_RASB

SCL1_+3.3V_DB

M2_SCLK

FRC_BA0

C5234

0.1uF

0.1uF

R5230

100

R5223

33

AVDD_PLL

URSA_MODEL_OPT_0

FRC_DQSUB

SW5201

JS2235S

URSA5_DEBUG

3

2

1

4

5

6

FRC_WEB

PWM0

L5202

CIC21J501NE

R5203

10K

GPIO[1]

C5236

0.1uF

0.1uF

R5224

100

R5214

10K

LVDS_S7M-PLUS

C5215

10uF

6.3V

10uF

6.3V

PWM0

C5219

0.1uF

0.1uF

R5244

4.7K

R5206

10K

L/DIM_EDGE_42/47/55

SDA1_+3.3V_DB

GPIO[8]

M3_MOSI

R5234

100

L5206

CIC21J501NE

R5221

4.7K OPT

R5249

33

+1.5V_FRC_DDR

FRC_ODT

L/R_SYNC

R5216

10K

M0_MOSI

C5202

0.1uF

0.1uF

+3.3V_FRC

VDD33

R

5

2

3

8

0

FRC_DQSLB

C5223

0.1uF

0.1uF

R5205

10K

L/DIM_EDGE_32/37

C5213

0.1uF

0.1uF

AVDD_LVDS_3.3V

L5204

CIC21J501NE

VDDC10

R5235

100

3D_SYNC_RF

URSA_MODEL_OPT_1

+3.3V_FRC

L5201

CIC21J501NE

M0_SCLK

L_VS

R5202

22

URSA5_DEBUG

2D/3D_CTL

R5232

100

+1.26V_FRC

SDA1_3.3V

M3_SCLK

AVDD_LVDS_3.3V

FRC_DML

R5250

33

SPI_CS

L5203

CIC21J501NE

FRC_A[0-13]

C5209

0.1uF

0.1uF

SPI_DO

R

5

2

4

1

0

R5248

33

R

5

2

3

9

0

R5218

10K

OPT

R5207

10K

C5216

0.1uF

0.1uF

SPI_CS

M1_MOSI

R5229

100

R5227

100

C5204

0.1uF

0.1uF

+1.5V_FRC_DDR

+3.3V_FRC

C5203

0.1uF

0.1uF

FRC_BA1

R

5

2

4

0

0

R5247

33

R5233

100

URSA_MODEL_OPT_2

VDD33

FRC_DQU[0-7]

R5228

100

M2_MOSI

R5253

33

3D-SG

C5228

0.1uF

0.1uF

URSA_MODEL_OPT_2

C5206

0.1uF

0.1uF

C5214

0.1uF

0.1uF

SCL1_3.3V

FRC_MCLKB

SDA1_+3.3V_URSA

FRC_DMU

FRC_CKE

R5201

22

URSA5_DEBUG

R

5

2

3

6

0

R5246

10K

PWM1

+3.3V_FRC

SCL1_+3.3V_URSA

AVDD33

GPIO[1]

R5222

33

R5252

3.3K

SCL1_+3.3V_DB

R5220

4.7K OPT

C5211

22uF

10V

22uF

10V

SPI_DI

GPIO[8]

FRC_BA2

C5243

0.22uF

6.3V

0.22uF

6.3V

C5244

0.22uF

6.3V

0.22uF

6.3V

C5245

0.22uF

6.3V

0.22uF

6.3V

R5258

0

0

URSA5_MP

R5260

0

OPT

OPT

R5261

0

OPT

OPT

R5259

0

URSA5_MP

X5201

24MHz

C5242

13pF

C5241

13pF

C5246

22uF

10V

22uF

10V

FRC_DDR3_RESETB

C5247

1uF

6.3V

1uF

6.3V

IC5202

W25X20BVSNIG

URSA5_FLASH_WINBOND_2M

3

WP

2

DO

4

GND

1

CS

5

DIO

6

CLK

7

HOLD

8

VCC

IC5202-*1

MX25L2006EM1I-12G, HF

URSA5_FLASH_MACRONIX_2M

3

WP

2

SO/SIO1

4

GND

1

CS

5

SI/S

6

SCL

7

HOL

8

VCC

+3.3V_FRC

R5254

4.7K

4.7K

URSA5_UO2_RESET

Q5201

2SC3052

URSA5_UO2_RESET

2SC3052

URSA5_UO2_RESET

E

B

C

R5255

22K

22K

URSA5_UO2_RESET

FRC_RESET

R5243

33

URSA5_UO3_RESET

C5212

4.7uF

16V URSA5_UO2_RESET

4.7uF

16V URSA5_UO2_RESET

R5219

10K

10K

OPT

Q5202

AO3407A

URSA5_UO2_RESET

G

D

S

R5256

10K

OPT

R5262

2.2K

2.2K

URSA5_UO2_RESET

IC5201

LGE7303C

DDR3_A0/DDR2_NC

P14

DDR3_A1/DDR2_A8

G15

DDR3_A2/DDR2_NC

N14

DDR3_A3/DDR2_A10

L15

DDR3_A4/DDR2_A2

H15

DDR3_A5/DDR2_A3

L14

DDR3_A6/DDR2_A4

G14

DDR3_A7/DDR2_A5

N12

DDR3_A8/DDR2_A6

G13

DDR3_A9/DDR2_A9

N13

DDR3_A10/DDR2_RASZ

H14

DDR3_A11/DDR2_A11

F15

DDR3_A12/DDR2_A0

H13

DDR3_A13/DDR2_A12

P13

DDR3_BA0/DDR2_BA2

M12

DDR3_BA1/DDR2_CASZ

H12

DDR3_BA2/DDR2_A1

L13

DDR3_MCLK/DDR2_MCLK

F16

DDR3_MCLKZ/DDR2_MCLKZ

F17

DDR3_CKE/DDR2_ODT

J13

DDR3_ODT/DDR2_CKE

K12

DDR3_RASZDDR2_WEZ

L12

DDR3_CASZ/DDR2_BA1

K13

DDR3_WEZ/DDR2_BA0

K14

DDR3_RESET/DDR2_A7

M14

DDR3_DQSL/DDR2_DQSL

N16

DDR3_DQSU/DDR2_DQSU

M17

DDR3_DQSBL/DDR2_DQSBL

M16

DDR3_DQSBU/DDR2_DQSBU

M15

DDR3_DQML/DDR2_DQU5

J15

DDR3_DQMU/DDR2_DQU4

R16

DDR3_DQL0/DDR2_DQU3

R17

DDR3_DQL1/DDR2_DQL0

H17

DDR3_DQL2/DDR2_DQL6

R15

DDR3_DQL3/DDR2_DQL7

J17

DDR3_DQL4/DDR2_DQL3

T17

DDR3_DQL5/DDR2_DQL2

H16

DDR3_DQL6/DDR2_DQL1

T15

DDR3_DQL7/DDR2_DQL5

G16

DDR3_DQU0/DDR2_DQU7

K15

DDR3_DQU1/DDR2_DQML

N15

DDR3_DQU2/DDR2_DQU2

K17

DDR3_DQU3/DDR2_DQU6

P17

DDR3_DQU4/DDR2_NC

L17

DDR3_DQU5/DDR2_DQU1

P16

DDR3_DQU6/DDR2_DQU0

K16

DDR3_DQU7/DDR2_DQMU

P15

I2CM_SCL

D14

I2CM_SDA

D15

I2CS_SCL

P1

I2CS_SDA

P2

DDR3_NC/DDR2_A13

F14

DDR3_NC/DDR2_DQL4

T16

VSS_1

D6

VSS_2

D7

VSS_3

D8

VSS_4

D9

VSS_5

E6

VSS_6

E7

VSS_7

E8

VSS_8

E9

VSS_9

E10

VSS_10

E16

VSS_11

F3

VSS_12

F6

VSS_13

F7

VSS_14

F8

VSS_15

F9

VSS_16

G1

VSS_17

G2

VSS_18

G4

VSS_19

G5

VSS_20

G6

VSS_21

G7

VSS_22

G8

VSS_23

G9

VSS_24

G17

VSS_25

H1

VSS_26

H2

VSS_27

H4

VSS_28

H5

VSS_29

H6

VSS_30

H7

VSS_31

H8

VSS_32

H9

VSS_33

H10

VSS_34

H11

VSS_35

J4

VSS_36

J5

VSS_37

J6

VSS_38

J7

VSS_39

J8

VSS_40

J9

VSS_41

J10

VSS_42

J11

VSS_43

J12

VSS_44

J14

VSS_45

J16

VSS_46

K4

VSS_47

K5

VSS_48

K6

VSS_49

K7

VSS_50

K8

VSS_51

K11

VSS_52

L6

VSS_53

L7

VSS_54

L8

VSS_55

L11

VSS_56

L16

VSS_57

M6

VSS_58

M7

VSS_59

M8

VSS_60

M11

VSS_61

M13

VSS_62

N6

VSS_63

N7

VSS_64

N8

VSS_65

N17

VSS_66

P3

VSS_67

P4

VSS_68

P5

VSS_69

P6

VSS_70

P7

VSS_71

P12

VSS_72

U16

NC

L9

HW_RESET

J3

TESTPIN_1

D1

TESTPIN_2

D2

TESTPIN_3

D3

TESTPIN_4

E1

TESTPIN_5

E2

TESTPIN_6

E3

TESTPIN_7

F1

TESTPIN_8

F2

M0_SCLK

C17

M0_MOSI

D16

M1_SCLK

D17

M1_MOSI

E15

M2_SCLK

E14

M2_MOSI

E13

M3_SCLK

E12

M3_MOSI

F13

SPI_CK

T9

SPI_CZ

U10

SPI_DI

U9

SPI_DO

T10

TXA0P/GCLK6/BLUE[7]

C8

TXA0N/GCLK5/BLUE[6]

C9

TXA1P/OPT_N/LK3/BLUE[9]

B8

TXA1N/FLK/BLUE[8]

A8

TXA2P/GREEN[1]

A7

TXA2N/OPT_P/LK2/GREEN[0]

B7

TXACLKP/RLV0N/GREEN[3]

C6

TXACLKN/RLV0P/GREEN[2]

C7

TXA3P/RLV1N/GREEN[5]

B6

TXA3N/RLV1P/GREEN[4]

A6

TXA4P/RLV2N/GREEN[7]

A5

TXA4N/RLV2P/GREEN[6]

B5

TXB0P/RLV3N/GREEN[9]

C4

TXB0N/RLV3P/GREEN[8]

C5

TXB1P/RLVCLKN/RED[1]

B4

TXB1N/RLVCLKP/RED[0]

A4

TXB2P/RLV4P/RED[3]/EPI_A3P

A3

TXB2N/RLV4N/RED[2]/EPI_A3N

B3

TXBCLKP/RLV5N/RED[5]/EPI_A2P

C2

TXBCLKN/RLV5P/RED[4]/EPI_A2N

C3

TXB3P/RLV6N/RED[7]/EPI_A1P

B2

TXB3N/RLV6P/RED[6]/EPI_A1N/

A2

TXB4P/RLV7N/RED[9]/EPI_A0P

C1

TXB4N/RLV7P/RED[8]/EPI_A0N

B1

TXC0P/SOE

C16

TXC0N/POL

B17

TXC1P/GSP_R

B16

TXC1N/GSP/VST

A16

TXC2P/GOE/GCLK1

A15

TXC2N/GSC/GCLK3

B15

TXCCLKP/LLV0N

C14

TXCCLKN/LLV0P

C15

TXC3P/LLV1N

B14

TXC3N/LLV1P

A14

TXC4P/LLV2N

A13

TXC4N/LLV2P

B13

TXD0P/LLV3N

C12

TXD0N/LLV3P

C13

TXD1P/LLVCLKN

B12

TXD1N/LLVCLKP

A12

TXD2P/LLV4N/EPI_B3P

A11

TXD2N/LLV4P/EPI_B3N

B11

TXDCLKP/LLV5N/BLUE[1]/EPI_B2P

C10

TXDCLKN/LLV5P/BLUE[0]/EPI_B2N

C11

TXD3P/LLV6N/BLUE[3]

B10

TXD3N/LLV6P/BLUE[2]/EPI_B1N

A10

TXD4P/LLV7N/BLUE[5]/EPI_B0P

A9

TXD4N/LLV7P/BLUE[4]/EPI_B0N

B9

MOD_GPIO0/VDD_ODD/HSYNC

D10

MOD_GPIO1/VDD_EVEN/VSYNC

D11

MOD_GPIO2/PWM13/GCLK4/LCK

D12

MOD_GPIO3/PWM14/GCLK2/LDE

D13

PWM0/SCAN_BLK1

U12

PWM1/SCAN_BLK2

T12

LPLL_FBCLK

G3

LPLL_OUTCLK

E17

LPLL_REFIN

H3

AVDD_1

F4

AVDD_2

F5

AVDD_DDR_C_1

F10

AVDD_DDR_C_2

G10

AVDD_DDR_D_1

F11

AVDD_DDR_D_2

F12

AVDD_DDR_D_3

G11

AVDD_DDR_D_4

G12

AVDD_LVDS3.3V_1

D4

AVDD_LVDS3.3V_2

D5

AVDD_LVDS3.3V_3

E4

AVDD_LVDS3.3V_4

E5

AVDD_MPLL3.3V

M5

AVDD_LPLL3.3V

L4

AVDD_PLL3.3V

L5

AVDDL_MOD1.26V

K10

DVDD_DDR_1.26V

L10

DVDD_HF1.26V

K9

VD33_1

M4

VD33_2

N4

VD33_3

N5

VDDC_1.26V_1

M9

VDDC_1.26V_2

M10

VDDC_1.26V_3

N9

VDDC_1.26V_4

N10

VDDC_1.26V_5

N11

VDDC_1.26V_6

P10

VDDC_1.26V_7

P11

RXBCLKP

R2

RXBCLKN

R3

RXB0P

R4

RXB0N

R5

RXB1P

T4

RXB1N

U4

RXB2P

U3

RXB2N

T3

RXB3P

T2

RXB3N

U2

RXB4P

T1

RXB4N

R1

RXACLKP

R6

RXACLKN

R7

RXA0P

R8

RXA0N

R9

RXA1P

T8

RXA1N

U8

RXA2P

U7

RXA2N

T7

RXA3P

T6

RXA3N

U6

RXA4P

U5

RXA4N

T5

XTALO

J1

XTALI

J2

GPIO0/(UART_RX/S_PIF_DA0)

R13

GPIO1

P9

GPIO2/(S_PIF_CLK)

T13

GPIO3/(LTD_DA1)

U15

GPIO4/(LTD_DE)

R14

GPIO5/(LTD_CLK)

K2

GPIO6/(LTD_DA0)

K1

GPIO7(3D_FLAG)

T14

GPIO8

P8

GPIO9/(UART_TX/S_PIF_DA1)

U14

GPIO10/(S_PIF_FC)

U13

GPIO11/(S_PIF_CS)

R12

VSYNC_LIKE

E11

M_S_PIF_CLK

N2

M_S_PIF_CS

M1

M_S_PIF_DA0

N1

M_S_PIF_DA1

N3

M_S_PIF_FC

M3

S_M_PIF_CLK

L1

S_M_PIF_CS

M2

S_M_PIF_DA0

L2

S_M_PIF_DA1

K3

S_M_PIF_FC

L3

SOFT_RST_L

R10

SOFT_RST_R

T11

OP_SYNC_L

R11

OP_SYNC_R

U11

LVDS_TX_1_DATA4_N

LVDS_TX_1_DATA0_P

LVDS_TX_1_CLK_N

LVDS_TX_0_CLK_N

LVDS_TX_0_CLK_P

LVDS_TX_0_DATA1_N

LVDS_TX_0_DATA3_P

LVDS_TX_0_DATA0_N

LVDS_TX_0_DATA1_P

LVDS_TX_1_DATA3_N

LVDS_TX_0_DATA2_N

LVDS_TX_0_DATA2_P

LVDS_TX_1_DATA2_N

LVDS_TX_1_CLK_P

LVDS_TX_1_DATA0_N

LVDS_TX_1_DATA3_P

LVDS_TX_1_DATA2_P

LVDS_TX_0_DATA3_N

LVDS_TX_0_DATA4_N

LVDS_TX_1_DATA4_P

LVDS_TX_1_DATA1_P

LVDS_TX_1_DATA1_N

LVDS_TX_0_DATA4_P

LVDS_TX_0_DATA0_P

RXD3+

RXB2-

RXD1+

RXC4-

RXD3-

RXDCK-

RXB1-

RXB4-

RXB1+

RXC0-

RXD1-

RXB0+

RXB3-

RXA2-

RXC2+

RXD2+

RXB3+

RXD2-

RXACK-

RXC0+

RXD4+

RXA0+

RXB4+

RXA4+

RXD0-

RXBCK+

RXA0-

RXACK+

RXC3+

RXA4-

RXB0-

RXA3+

RXBCK-

RXC1+

RXC1-

RXCCK-

RXA1+

RXA2+

RXD0+

RXD4-

RXCCK+

RXC3-

RXC4+

RXDCK+

RXB2+

RXA3-

RXA1-

RXC2-

3D_SYNC_RF

FRC block

MStar URSA5

55

52

2010. 08.18

L/DIM_10BLOCK

D13

GPIO1 : HI => B8/94, LOW => B4/98

LOW

LVDS_S7M_PLUS

MODEL_OPT_0

MODEL_OPT_3

Debugging for URSA5

CHIP_CONF : {GPIO8, PWM1, PWM0}

CHIP_CONF = 3’d5 : boot from interal SRAM

CHIP_CONF = 3’d6 : boot from EEPROM

CHIP_CONF = 3’d7 : boot from SPI Flash

CHIP_CONF = 3’d5 : boot from interal SRAM

CHIP_CONF = 3’d6 : boot from EEPROM

CHIP_CONF = 3’d7 : boot from SPI Flash

PIN NO.

[SPI FLASH(2Mbit)]

LVDS_EXT_URSA5

D11

D10

D12

RESERVED

MODEL_OPT_2

MODEL OPTION

(VDDP)

HIGH

PIN NAME

RESERVED

PLACE TERMINATION RESISTORS CLOSE TO URSA5

MODEL_OPT_1

URSA5 CONFIGURATION

Place Close to Bead

URSA5 H/W OPTION

L/DIM_16BLOCK

RESERVED

RESERVED

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

DDR3_DQU[1]

DDR3_DQL[1]

DDR3_DQL[3]

DDR3_A[8]

DDR3_A[3]

DDR3_A[12]

DDR3_A[13]

DDR3_A[5]

DDR3_DQL[7]

DDR3_A[7]

DDR3_DQL[0]

DDR3_DQL[6]

DDR3_A[11]

DDR3_A[2]

DDR3_DQU[0]

DDR3_A[10]

DDR3_DQU[2]

DDR3_A[9]

DDR3_DQL[4]

DDR3_DQU[6]

DDR3_A[0]

DDR3_A[4]

DDR3_DQL[5]

DDR3_A[6]

DDR3_DQU[4]

DDR3_A[1]

DDR3_DQU[3]

DDR3_DQL[2]

DDR3_DQU[7]

DDR3_DQU[5]

FRC_DQL[4]

+1.5V_FRC_DDR

FRC_A[10]

FRC_DQSL

R5312

22

MVREFDQ

FRC_DQSUB

DDR3_DQSLB

DDR3_BA0

DDR3_DQSLB

DDR3_ODT

DDR3_A[10]

FRC_DQL[3]

R5310

56

56

R5316

22

FRC_DQL[5]

DDR3_CKE

FRC_CASB

FRC_DQU[3]

DDR3_DMU

FRC_DQU[6]

R5321

22

FRC_BA2

FRC_DQU[7]

FRC_CKE

C5312

0.1uF

AR5306

22

DDR3_DQL[6]

FRC_DQL[7]

FRC_DQL[6]

C5314

0.1uF

+1.5V_FRC_DDR

DDR3_MCK

+1.5V_FRC_DDR

DDR3_BA0

FRC_DQL[0]

DDR3_A[6]

DDR3_DQSUB

DDR3_A[2]

AR5304

22

DDR3_MCK

DDR3_DQL[0-7]

DDR3_DQSL

DDR3_DQU[2]

AR5302

22

DDR3_BA2

DDR3_DQL[0]

FRC_DML

DDR3_DML

DDR3_ODT

DDR3_A[8]

FRC_A[11]

FRC_A[9]

FRC_DQSLB

R5304

1K

1%

1%

DDR3_BA1

DDR3_DQU[0-7]

DDR3_BA1

DDR3_A[9]

DDR3_DQL[4]

DDR3_WEB

DDR3_A[0-13]

FRC_ODT

DDR3_DML

R5302

1K

1%

1%

FRC_BA1

R5301

1K

1%

DDR3_DQU[7]

MVREFDQ

C5313

0.1uF

DDR3_DQU[1]

DDR3_RASB

DDR3_DQL[5]

FRC_A[12]

DDR3_DQL[3]

DDR3_DQU[5]

+1.5V_FRC_DDR

AR5307

22

FRC_A[4]

R5320

22

FRC_A[13]

DDR3_A[1]

AR5305

22

DDR3_DMU

FRC_DQU[2]

FRC_DQU[0]

DDR3_RASB

DDR3_CASB

FRC_A[8]

DDR3_A[11]

+1.5V_FRC_DDR

DDR3_DQSUB

R5309

56

56

FRC_A[2]

C5305

0.1uF

DDR3_A[12]

DDR3_DQU[6]

DDR3_MCK

DDR3_DQU[0]

DDR3_CASB

FRC_MCLK

FRC_DQU[5]

DDR3_WEB

R5313

22

+1.5V_FRC_DDR

AR5309

22

FRC_A[5]

DDR3_A[0]

DDR3_DQU[3]

R5317

22

C5306

0.1uF

R5314

22

FRC_WEB

DDR3_MCKB

C5315

0.01uF

25V

0.01uF

25V

C5308

0.1uF

R5311

22

AR5303

22

DDR3_MCKB

FRC_DQU[1]

DDR3_MCKB

DDR3_DQSU

C5309

0.1uF

FRC_A[7]

FRC_RASB

FRC_DMU

FRC_A[1]

MVREFCA

AR5301

22

C5304

22uF

10V

22uF

10V

DDR3_DQL[7]

DDR3_A[3]

FRC_DQSU

DDR3_A[13]

C5302

0.1uF

C5310

0.1uF

FRC_BA0

DDR3_BA2

DDR3_CKE

MVREFCA

FRC_A[6]

R5318

22

C5303

0.1uF

16V

0.1uF

16V

FRC_DQL[2]

AR5308

22

C5307

0.1uF

R5319

22

DDR3_DQU[4]

C5301

0.1uF

R5303

1K

1%

1%

DDR3_DQL[1]

C5311

0.1uF

FRC_MCLKB

DDR3_A[5]

DDR3_DQL[2]

R5315

22

FRC_DQL[1]

DDR3_DQSU

DDR3_DQSL

FRC_A[0]

DDR3_A[7]

FRC_A[3]

DDR3_A[4]

R5307

150

OPT

FRC_DQU[4]

R5305

240

1%

H5TQ1G63DFR-PBC

IC5301

URSA5_DDR3_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

R5308

0

DDR3_RESETB

FRC_DDR3_RESETB

DDR3_RESETB

R5322

22

K4B1G1646G-BCK0

IC5301-*1

URSA5_DDR3_SS

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

DDR3 4Mbit

53

MStar URSA5

55

2010. 08.18

Place Close to DDR Pin

Place Close to DDR Pin

Close to DDR Pin

Place the serail damping resistors

in the middle of DRAM pattern

in the middle of DRAM pattern

DDR3 1.5V De-Cap Place near Memory

Click on the first or last page to see other 42LW6500-JA (CHASSIS:LE13E) service manuals if exist.