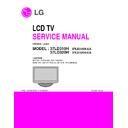

LG 37LD310H / 37LD320H (CHASSIS:LA06A) Service Manual ▷ View online

- 17 -

10.3 b_LAN Main board Check

10.3.1 Overview

It is LNET RF modem & FTG card

It is LNET RF modem & FTG card

10.3.2 Equipment

1) b_LAN Checker: UTC-1000 (with Cable accessory)

2) Computer(for test result monitoring)

3) Connection JIG

1) b_LAN Checker: UTC-1000 (with Cable accessory)

2) Computer(for test result monitoring)

3) Connection JIG

10.3.3 Equipnent connection map & b_LAN Check

4) Check

=========================================

1. Setting Procedure

1) Setting JIG

(1) Connect UTC-1000 Equipment to JIG device as a like left picture

=========================================

1. Setting Procedure

1) Setting JIG

(1) Connect UTC-1000 Equipment to JIG device as a like left picture

- Connection Line:

UTC-1000 TOP1 <--> Game port(RJ21)

-> TV-LINK CFG (Phone Jack)

UTC-1000 TOP2 <--> JIG 11pin Connection

UTC-1000 RF1 <--> b_LAN RF IN

UTC-1000 LAN <--> PC LAN Port

UTC-1000 RF1 <--> b_LAN RF IN

UTC-1000 LAN <--> PC LAN Port

2. Working procedure

1) Connection

1) Connection

UTC-1000 LAN <--> PC LAN Port

UTC-1000 TOP1 <--> Game port(RJ21)

UTC-1000 TOP1 <--> Game port(RJ21)

-> TV-LINK CFG (Phone Jack)

UTC-1000 RF1 <--> b_LAN RF IN

2) Power on JIG

3) Test Start

3) Test Start

UTC-1000 TOP2 <--> JIG 11pin Connection

4) Checking b-LAN MAC Address

Check whether it is same their address numbers or not between B-LAN Label and on the pc address numbers.

TOP1

TOP2

RF1

Pow er

TOP

AC

110V

UTC-1000

LAN PORT

Computer LA N

PORT

b_LAN RF IN

RJ12

Phone Jack (2)

- 18 -

* Checking JIG contents

1. Check whether displaying all “Pass” or not at the number 3.4.6.7.9 contents of UTC-1000 on the PC

2. Check “Version 6.0” of the 1. b_LAN Application version

3. Check whether it is same their address numbers or not between B-LAN Label and 2. MAC Address on the pc.

1. Check whether displaying all “Pass” or not at the number 3.4.6.7.9 contents of UTC-1000 on the PC

2. Check “Version 6.0” of the 1. b_LAN Application version

3. Check whether it is same their address numbers or not between B-LAN Label and 2. MAC Address on the pc.

11. Serial number download.

Connect Bar Code scan equipment and TV set by RS-232C cable.

1) E2PROM Data Write

2) E2PROM Data Read

- 19 -

200

A7

800

LV1

A2

A10

802

400

900

530

550

300

120

510

500

803

804

521

540

805

* Set + Stand

EXPLODED VIEW

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

TS_5

0 0 1 : A J 1 5

0.1uF

16V

C2214

MLB-201209-0120P-N2

L1227

0.1uF

16V

C2199

0

R2401

3 . 3 V _ P r o i d i o m

TS_SYNC

0 0 1 : A J 1 6

3 . 3 V _ P r o i d i o m

TS_3

0 0 1 : A J 1 5

0.1uF

16V

C2202

0.1uF

16V

C2211

0.1uF

16V

C2207

0.1uF

16V

C2215

PM_TS_SYNC

0 0 1 : A J 1 9

+VCCINT_1.5V

0 1 2 : S 2 6 ; 0 1 2 : A J 2 6

0

R2425

MLB-201209-0120P-N2

L1235

PM_TS[0-7]

0 0 1 : A J 1 9

+VCCINT_1.5V

4.7K

R2563

MLB-201209-0120P-N2

L1236

0.1uF

16V

C2205

3 . 3 V _ P r o i d i o m

MSCL_3.3V

FE_DEMOD_SCL

0 0 1 : A G 5 ; 0 0 2 : S 2 0

3 . 3 V _ P r o i d i o m

+VCCINT_1.5V

0.1uF

16V

C2213

BSS83

Q1115

S

B

D

G

10uF

16V

16V

C2176

0.1uF

16V

C2203

AMP_SDA

: A G 6 ; 0 0 2 : Q 2 1 ; 0 0 2 : T 1 9 ; 0 0 7 : C 1 2 ; 0 0 7 : J 5 ; 0 3 8 : F 1 4

1uF

50V

C2192

VSB_RESET

012:B17

AMP_SCL

G 6 ; 0 0 2 : Q 2 1 ; 0 0 2 : U 1 5 ; 0 0 7 : E 1 4 ; 0 0 7 : J 5 ; 0 3 8 : F 1 3

100

R2564

10K

R2391

1K

R2403

0.1uF

16V

C2193

TS_7

0 0 1 : A J 1 4

0.1uF

16V

C2217

0

R2386

OPT

TS_VALID

0 0 1 : A J 1 6

0

R2436

0

R2420

TS_CLK

0 0 1 : A J 1 7

3 . 3 V _ P r o i d i o m

0 . 1 u F

16V

16V

C2181

OPT

3 . 3 V _ P r o i d i o m

0.1uF

16V

C2187

TS_2

0 0 1 : A J 1 5

0

R2385

OPT

3 . 3 V _ P r o i d i o m

TS_1

0 0 1 : A J 1 6

GND

0.1uF

16V

C2204

0

R2431

DE_H_SYSCLK

012:C13

+3.3V_Normal

MLB-201209-0120P-N2

L1232

1uF

25V

C2179

OPT

FPGA_RESET

012:Q17

0

R2426

0.1uF

16V

C2206

1K

R2404

62pF

50V

50V

C2219

OPT

10K

R2392

3 . 3 V _ P r o i d i o m

MLB-201209-0120P-N2

L1231

0.1uF

16V

C2197

MLB-201209-0120P-N2

L1233

3 . 3 V _ P r o i d i o m

0.01uF

C2191

1uF

25V

C2255

1K

R2397

LGDT1129

IC1209

H1

CLK1

B8

IO2_29/TP_SOP

B9

IO2_21/TP_VALID

B10

IO2_17/TP_ERR

C5

IO2_41/TP_DATA[7]

C6

IO2_36/TP_DATA[6]

C7

IO2_31/TP_DATA[5]

C8

IO2_25/TP_DATA[4]

C9

IO2_23/TP_DATA[3]

C10

IO2_18/TP_DATA[2]

C11

IO2_14/TP_DATA[1]

C12

IO2_8/TP_DATA[0]

M1

IO1_29

C3

IO1_2

C2

IO1_3

B1

IO1_4

G5

IO1_5

F4

IO1_6

D3

IO1_7

E4

IO1_8

F5

IO1_9

E3

IO1_10

D2

IO1_11

E2

IO1_12

G1

CLK0

B2

IO2_48/RESET

D14

IO3_37/I2C_SCK

E14

IO3_34/I2C_SDA

K4

DCLK

K13

CONF_DONE

H3

NCONFIG

J 4

NCE

H2

DATA0

G4

IO1_21SO

K3

IO1_22/ASDO

H4

NCEO

J 1 3

NSTATUS

J 3

MSEL0

J 2

MSEL1

J 1 4

TCK

H15

TDO

J 1 5

TMS

H14

TDI

D4

IO1_1/INIT_DONE

D1

IO1_13

F3

IO1_14

G3

IO1_15

F2

IO1_16

E1

IO1_17

G2

IO1_18

F1

IO1_19

H5

IO1_20

J 1

IO1_23

K2

IO1_24

L3

IO1_25

K1

IO1_26

L1

IO1_27

L2

IO1_28

N1

IO1_30

M2

IO1_31

N2

IO1_32

M3

IO1_33

L5

IO1_34

M4

IO1_35

N3

IO1_36

K5

IO1_37

L4

IO1_38

R1

IO1_39

P2

IO1_40

P3

IO1_41

N4

IO1_42

R2

IO4_1

T2

IO4_2

R3

IO4_3

P4

IO4_4

R4

IO4_5

T4

IO4_6

R5

IO4_7

M5

IO4_9

M6

IO4_10

N5

IO4_11

N6

IO4_12

R6

IO4_14

M7

IO4_15

T6

IO4_16

R7

IO4_17

N7

IO4_19

T8

IO4_21

M8

IO4_22

N8

IO4_23

M10

IO4_25

T9

IO4_27

N9

IO4_29

T11

IO4_31

N10

IO4_32

N11

IO4_36

N12

IO4_37

M9

IO4_38

M11

IO4_39

M12

IO4_40

R12

IO4_42

T13

IO4_43

R13

IO4_44

R14

IO4_45

P13

IO4_46

T15

IO4_47

R15

IO4_48

N13

IO3_1

P14

IO3_2

P15

IO3_3

R16

IO3_4

N15

IO3_5

N16

IO3_6

K12

IO3_7

K14

IO3_8

L12

IO3_9

N14

IO3_10

M13

IO3_11

M14

IO3_12

L13

IO3_13

M15

IO3_14

M16

IO3_15

L14

IO3_16

L15

IO3_17

L16

IO3_18

K16

IO3_19

K15

IO3_20

J16

IO3_21

H16

CLK3

G16

CLK2

H12

IO3_22

G14

IO3_23

G13

IO3_24

G15

IO3_25

F16

IO3_26

F14

IO3_27

F13

IO3_28

F15

IO3_29

E16

IO3_30

E15

IO3_31

D16

IO3_32

D15

IO3_33

F12

IO3_35

E13

IO3_36

H13

IO3_38

G12

IO3_39

B16

IO3_40

C15

IO3_41

C14

IO3_42

D13

IO3_43

B15

IO2_1

A15

IO2_2

B14

IO2_3

C13

IO2_4

B13

IO2_5

A13

IO2_6

B12

IO2_7

A2

IO2_47

E12

IO2_9

E11

IO2_10

E9

IO2_11

D12

IO2_12

D11

IO2_13

B3

IO2_46

B11

IO2_15

A11

IO2_16

D10

IO2_19

A9

IO2_20

D9

IO2_22

C4

IO2_45

E10

IO2_24

B4

IO2_44

D8

IO2_26

E8

IO2_27

A8

IO2_28

D7

IO2_30

A4

IO2_43

B7

IO2_32

A6

IO2_33

E7

IO2_34

P12

IO4_41/CH_DATA[7]

P11

IO4_35/CH_DATA[6]

P10

IO4_33/CH_DATA[5]

P9

IO4_28/CH-DATA[4]

P8

IO4_24/CH_DATA[3]

P7

IO4_18/CH_DATA[2]

P6

IO4_13/CH_DATA[1]

P5

IO4_8/CH_DATA[0]

R10

IO4_30/CH_ERR

R9

IO4_26/CH_SOP

R8

IO4_20/CH_VALID

R11

IO4_34/CH_CLK

A7

VCCINT_1

A10

VCCINT_2

G8

VCCINT_3

G10

VCCINT_4

H7

VCCINT_5

H9

VCCINT_6

J8

VCCINT_7

J10

VCCINT_8

K7

VCCINT_9

K9

VCCINT_10

T7

VCCINT_11

T10

VCCINT_12

C1

VCCIO1_1

G6

VCCIO1_2

P1

VCCIO1_3

T3

VCCIO4_1

L7

VCCIO4_2

L10

VCCIO4_3

T14

VCCIO4_4

P16

VCCIO3_1

K11

VCCIO3_2

C16

VCCIO3_3

A14

VCCIO2_1

F10

VCCIO2_2

F7

VCCIO2_3

A3

VCCIO2_4

A1

GND_1

A16

GND_2

A5

GND_3

A12

GND_4

F6

GND_5

F8

GND_6

F9

GND_7

F11

GND_8

G7

GND_9

G9

GND_10

G11

GND_11

H8

GND_12

H10

GND_13

J7

GND_14

J9

GND_15

K6

GND_16

K8

GND_17

K10

GND_18

L6

GND_19

L8

GND_20

L9

GND_21

L11

GND_22

T1

GND_23

T5

GND_24

T12

GND_25

T16

GND_26

J6

GNDA_PLL1

J5

GNDG_PLL1

J11

GNDA_PLL2

J12

GNDG_PLL2

H6

VCCA_PLL1

H11

VCCA_PLL2

B6

IO2_35

B5

IO2_42

D6

IO2_37

D5

IO2_38

E6

IO2_39

E5

IO2_40

MAX809RTR

IC1210

temp

1

GND

3

VCC

2

RESET

0

R2447

0.1uF

16V

C2196

TS_4

0 0 1 : A J 1 5

1K

R2402

3 . 3 V _ P r o i d i o m

MSDA_3.3V

0 . 1 u F

16V

16V

C2178

0

R2446

0.1uF

16V

C2194

SYS_RESET

0 0 1 : A J 2 1

0

R2435

MLB-201209-0120P-N2

L1228

0.1uF

16V

C2212

3 . 3 V _ P r o i d i o m

MSCL_3.3V

PM_TS_VALID

0 0 1 : A J 1 9

GND

22

R2387

1N4148W

D1250

OPT

OPT

MLB-201209-0120P-N2

L1234

FE_DEMOD_SDA

0 0 1 : A G 5 ; 0 0 2 : S 2 0

+5V_Normal

0.1uF

16V

C2190

TS_6

0 0 1 : A J 1 5

PM_TS_CLK

0 0 1 : A J 1 9

0

R2448

1uF

50V

C2185

FPGA_RESET

012:B19

0.1uF

16V

C2200

0

R2421

DE_H_SYSCLK

012:Q17

0.1uF

16V

C2218

MSDA_3.3V

TS_0

0 0 1 : A J 1 6

0.1uF

16V

C2210

0.1uF

16V

C2195

0.1uF

16V

C2216

0

R2399

BSS83

Q1114

S

B

D

G

10K

R2390

OPT

0.01uF

C2188

OPT

R2405

0.1uF

16V

C2208

3 . 3 V _ P r o i d i o m

0.1uF

16V

C2198

0

R2419

0

R2423

0.1uF

16V

C2209

27MHz

X1006

6

1

2

5

3

4

10K

OPT

R2406

0

R2424

100uF

16V

16V

C2177

100

OPT

R2393

0

OPT

R2418

MLB-201209-0120P-N2

L1230

0

R2449

0 . 1 u F

16V

16V

C2180

OPT

100

R2394

OPT

0.1uF

16V

C2201

VSB_RESET

22

R2415

22

R2416

22

R2417

100

R2441

100

R2442

100

R2443

100

R2444

10K

R2412

10K

R2413

10K

R2414

10K

R2409

10K

R2408

10K

R2422

4 . 7 u F

16V

C2186

4 . 7 u F

16V

C2189

PM_TS[2]

TS_7

PM_TS[4]

PM_TS[1]

TS_4

TS_0

TS_6

PM_TS[0]

PM_TS[7]

TS_2

PM_TS[6]

PM_TS[5]

TS_3

TS_1

TS_5

PM_TS[3]

FPGA

RESET

FPGA POWER

I2C

INNER LAYER PATERN

27MHz

FPGA

1 2 ( 1 1 )

21

LD320H-UA_LA06A

2 0 1 0 . 0 9 . 0 4

Click on the first or last page to see other 37LD310H / 37LD320H (CHASSIS:LA06A) service manuals if exist.