LG 32LN570B (CHASSIS:LA33B) Service Manual ▷ View online

- 21 -

6. AUDIO output check

6.1. Audio input condition

(1) RF input: Mono, 1KHz sine wave signal, 100% Modulation

(2) CVBS, Component: 1KHz sine wave signal (0.4Vrms)

(3) RGB PC: 1KHz sine wave signal (0.7Vrms)

6.2. Specification

No

Item

Min

Typ Max Unit

Remark

1

Audio

practical

max Output,

L/R

(Distor-

tion=10%

max Output)

9.0

8.5

10.0

8.9

12.0

9.9

W

Vrms

(1) Measurement

condition

- EQ/AVL/Clear

Voice: Off

(2) Speaker (8Ω

Impedance)

7. GND and HI-POT Test

7.1. GND & HI-POT auto-check preparation

(1) Check the POWER CABLE and SIGNAL CABE insertion

condition

7.2. GND & HI-POT auto-check

(1) Pallet moves in the station. (POWER CORD / AV CORD is

tightly inserted)

(2) Connect the AV JACK Tester.

(3) Controller (GWS103-4) on.

(4) GND Test (Auto)

- If Test is failed, Buzzer operates.

- If Test is passed, execute next process (Hi-pot test).

(Remove A/V CORD from A/V JACK BOX)

(5) HI-POT test (Auto)

- If Test is failed, Buzzer operates.

- If Test is passed, GOOD Lamp on and move to next process

automatically.

7.3. Checkpoint

(1) Test voltage

- GND: 1.5KV/min at 100mA

- SIGNAL: 3KV/min at 100mA

(2) TEST time: 1 second

(3) TEST POINT

- GND Test = POWER CORD GND and SIGNAL CABLE GND.

- Hi-pot Test = POWER CORD GND and LIVE & NEUTRAL.

(4) LEAKAGE CURRENT: At 0.5mArms

8. USB S/W Download

(optional, Service only)

(1) Put the USB Stick to the USB socket

(2) Automatically detecting update file in USB Stick

- If your downloaded program version in USB Stick is lower

than that of TV set, it didn’t work. Otherwise USB data is

automatically detected.

(3) Show the message “Copying files from memory”

(5) Updating Completed, The TV will restart automatically

(6) If your TV is turned on, check your updated version and

Tool option.

* If downloading version is more high than your TV have, TV

can lost all channel data. In this case, you have to channel

recover. If all channel data is cleared, you didn’t have a DTV/

ATV test on production line.

* After downloading, TOOL OPTION setting is needed again.

(1) Push "IN-START" key in service remote controller.

(2) Select "Tool Option 1" and Push “OK” button.

(3) Punch in the number. (Each model has their number.)

(4) Updating is staring.

- 22 -

9. Optional adjustments

9.1. Manual ADC Calibration

9.1.1. Equipment & Condition

(1) Adjustment Remocon

(2) 801GF (802B, 802F, 802R) or MSPG925FA Pattern

Generator

- Resolution : 480i Comp1 (MSPG-925FA: model-209,

pattern-65)

- Resolution : 1080p Comp1 (MSPG-925FA: model-225,

pattern-65)

- Resolution : 1080p RGB (MSPG-925FA: model-225,

pattern-65)

- Pattern : Horizontal 100% Color Bar Pattern

- Pattern level : 0.7±0.1 Vp-p

9.1.2. Adjust method

8.1.2.1 ADC 480i/1080p Comp1, RGB

(1) Check connected condition of Comp1/RGB cable to the

equipment

(2) Give a 480i Mode, Horizontal 100% Color Bar Pattern to

Comp1. (MSPG-925FA -> Model: 209, Pattern: 65)

(3) Change input mode as Component1 and picture mode as

“Standard”

(4) Press the In-start Key on the ADJ remote after at least 1

min of signal reception. Then, select 7.External ADC. And

Press OK or Right Button for going to sub menu.

(5) Press OK in Comp 480i menu

(6) Give a 1080p Mode, Horizontal 100% Color Bar Pattern to

Comp1. (MSPG-925FA -> Model: 225, Pattern: 65)

(7) Press OK in Comp 1080p menu

(8) Perform (6) and (7) in RGB-PC

(9) If ADC Comp is successful, “ADC Component Success” is

displayed. If ADC calibration is failure, “ADC Component

Fail” is displayed.

(10) If ADC calibration is failure, after rechecking ADC pattern

or condition, retry calibration

(11) If ADC RGB calibration is successful, “ADC RGB

Success” is displayed. If ADC calibration is failure, “ADC

RGB Fail” is displayed.

(12) If ADC calibration is failure, after recheck ADC pattern or

condition, retry calibration

9.2. Manual White balance Adjustment

9.2.1. Adj. condition and cautionary items

(1) Lighting condition in surrounding area surrounding lighting

should be lower 10 lux. Try to isolate adj. area into dark

surrounding.

(2) Probe location: Color Analyzer (CA-210) probe should be

within 10cm and perpendicular of the module surface

(80°~ 100°)

(3) Aging time

▪ After Aging Start, Keep the Power ON status during 5

Minutes.

▪ In case of LCD, Back-light on should be checked using no

signal or Full-white pattern.

9.2.2. Equipment

(1) Color Analyzer: CA-210 (NCG: CH 9 / WCG: CH12 / LED:

CH14)

(2) Adj. Computer (During auto adj., RS-232C protocol is

needed)

(3) Adjust Remocon

(4) Video Signal Generator MSPG-925F 720p/216-Gray

(Model: 217, Pattern: 78)

9.2.3. Adjustment

(1) Set TV in Adj. mode using POWER ON

(2) Zero Calibrate the probe of Color Analyzer, then place it on

the center of LCD module within 10cm of the surface.

(3) Press ADJ key -> EZ adjust using adj. R/C -> 6. White-

Balance then press the cursor to the right (KEY►).

When KEY(►) is pressed 216 Gray internal pattern will be

displayed.

(4) One of R Gain / G Gain / B Gain should be fixed at 192,

and the rest will be lowered to meet the desired value.

(5) Adj. is performed in COOL, MEDIUM, WARM 3 modes of

color temperature.

▪ If internal pattern is not available, use RF input. In EZ Adj.

menu 6.White Balance, you can select one of 2 Test-pattern:

ON, OFF. Default is inner(ON). By selecting OFF, you can

adjust using RF signal in 216 Gray pattern.

- 23 -

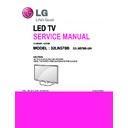

EXPLODED VIEW

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

A2

A9

A10

900

200

400

540

521

570

530

500

301

910

120

300

510

123

122

121

Set + Stand

Stand Base

+

Stand Body

LV

1

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MT5398_TS_OUT[1]

CI_ADDR[5]

EMMC_DATA[6]

MT5398_TS_OUT[6]

CI_ADDR[4]

FE_DEMOD1_TS_DATA[1]

MT5398_TS_OUT[4]

CI_ADDR[12]

EMMC_DATA[3]

CI_DATA[1]

FE_DEMOD1_TS_DATA[6]

MT5398_TS_OUT[3]

CI_DATA[5]

EMMC_DATA[4]

FE_DEMOD1_TS_DATA[0]

CI_ADDR[6]

CI_ADDR[11]

MT5398_TS_OUT[2]

CI_ADDR[10]

CI_DATA[2]

MT5398_TS_OUT[7]

CI_ADDR[14]

CI_ADDR[9]

MT5398_TS_OUT[0]

FE_DEMOD1_TS_DATA[3]

EMMC_DATA[5]

CI_ADDR[13]

EMMC_DATA[2]

FE_DEMOD1_TS_DATA[5]

CI_DATA[3]

CI_DATA[6]

CI_DATA[0]

CI_ADDR[7]

CI_DATA[7]

CI_ADDR[8]

CI_ADDR[1]

EMMC_DATA[7]

FE_DEMOD1_TS_DATA[4]

CI_ADDR[2]

FE_DEMOD1_TS_DATA[7]

MT5398_TS_OUT[5]

CI_ADDR[0-14]

FE_DEMOD1_TS_DATA[2]

CI_DATA[4]

CI_ADDR[0]

CI_ADDR[3]

R111

33

EMMC_RST

SMARTCARD_RST/SD_EMMC_DATA[2]

M_RFModule_RESET

AVDD_33SB

SMARTCARD_RST/SD_EMMC_DATA[2]

+3.3V_NORMAL

OPCTRL7

R189

10K

10K

OPT

I2C_SCL4

R125

4.7K

OPT

R134

33

MT5398_XTAL_OUT

MT5398_MIVAL_ERR

STB_SDA

OPCTRL_11_SCL

R107

4.7K

MTK_HD

OPCTRL_10_SDA

/USB_OCD1

MODEL_OPT_5

I2C_SCL5

R183

4.7K

4.7K

MT5398_XTAL_OUT

R109

33

R128

4.7K

MODULE_V12

R184

4.7K

4.7K

EMMC_CMD

OSCL0

I2C_SCL6

R185

10K

EMMC_DATA[0]

R177

4.7K

4.7K

OPT

R142

2.7K

2.7K

HP_DET

MODEL_OPT_6

EMMC_CLK

/USB_OCD3

R132

2.7K

2.7K

R135

33

C112

4.7uF

10V

4.7uF

10V

/PCM_OE

R104

4.7K

NON_FRC_60Hz

R112

33

AMP_RESET_SOC

R123

4.7K

Country_AJJA

R117

33

/S2_RESET

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

I2C_SDA6

FE_LNA_Ctrl1

AVDD_33SB

+3.3V_NORMAL

/PCM_REG

STB_SCL

OPC_EN

R187

4.7K

OPT

MT5398_TS_IN[5]

I2C_SDA_MICOM

R160

1K

1K

OPT

OPCTRL_1_SCL

+3.3V_NORMAL

R149

4.7K

MTK_EPI

R127

22

OPT

SC_DET

R178

22

CI_ADDR[0-14]

EMMC_CLK

SMARTCARD_DET/SD_EMMC_DATA[3]

I2C_SDA5

R140

4.7K

MTK_DVB_T2_TUNER

R126

22

OPT

L/DIM0_SCLK

R174

4.7K

4.7K

OPT

SMARTCARD_DET/SD_EMMC_DATA[3]

I2C_SDA5

IC101

M24C16-R

OPT

3

NC_3

2

NC_2

4

VSS

1

NC_1

5

SDA

6

SCL

7

WC

8

VCC

OSCL0

R108

4.7K

MTK_FHD

SOC_RX

R147

2.7K

2.7K

SMARTCARD_VCC/SD_EMMC_CMD

OSDA1

R193

4.7K

R146

4.7K

DDR_0.78G

OPCTRL3

R173

1K

1K

PWM1_PULL_DOWN_1K

R124

1.2K

1.2K

R182

33

OSDA1

AV1_CVBS_DET

R100

4.7K

OPT

R136

4.7K

MTK_NON_CP_BOX

USB_CTL3

MODEL_OPT_0

PWM_DIM1

OSDA0

SOC_RESET

+3.3V_NORMAL

USB_CTL1

LED_PWM0

R137

4.7K

MTK_CP_BOX

C107

4.7uF

10V

4.7uF

10V

SMARTCARD_DATA/SD_EMMC_CLK

I2C_SDA4

+3.3V_NORMAL

EMMC_DATA[1]

MODEL_OPT_6

OPCTRL_0_SDA

MODEL_OPT_0

I2C_SCL2

EPI_LOCK6

R106

4.7K

FRC_120Hz

OSCL2

C100

0.1uF

OPT

16V

R170

10K

/PCM_CE1

MODEL_OPT_5

EMMC_DATA[2-7]

/PCM_WE

R179

PWM_DIM2

22

C117

0.1uF

16V

16V

R188

4.7K

4.7K

R119

33

SMARTCARD_PWR_SEL/SD_EMMC_DATA[1]

R113

33

I2C_SDA1

R169

10K

NON_EU

I2C_SCL1

PWM_DIM2

R186

22

OSDA0

/PCM_IRQA

CI_A_VS1

R168

10K

C109

0.1uF

0.1uF

C111

0.1uF

0.1uF

CTS

IC100

AT24C256C-SSHL-T

NVRAM_ATMEL

3

A2

2

A1

4

GND

1

A0

5

SDA

6

SCL

7

WP

8

VCC

MODEL_OPT_7

R143

4.7K

MTK_NON_DVB_S_TUNER

R152

2.7K

2.7K

NON_TU_Q_KR

+3.3V_NORMAL

MT5398_TS_IN[2]

R151

2.7K

2.7K

R141

2.7K

2.7K

R163

1K

1K

MT5398_MCLKI

OPCTRL_10_SDA

MT5398_TS_CLK

MODEL_OPT_3

MODEL_OPT_8

RTS

R150

2.7K

2.7K

SMARTCARD_VCC/SD_EMMC_CMD

FE_DEMOD1_TS_DATA[0-7]

MODEL_OPT_7

MODEL_OPT_3

R155

1K

1K

R110

33

MT5398_TS_VAL

FE_LNA_Ctrl2

OPCTRL3

AVDD_33SB

STB_SCL

OPCTRL_0_SDA

R139

4.7K

MTK_NON_DVB_T2_TUNER

SC_ID_SOC

/PCM_IOWR

SMARTCARD_CLK/SD_EMMC_DATA[0]

R101

4.7K

SMARTCARD_DATA/SD_EMMC_CLK

R161

1K

1K

OPT

/PCM_WAIT

OSCL1

R115

33

OSCL1

+3.3V_NORMAL

R122

4.7K

Non_Country_AJJA

R114

33

MT5398_XTAL_IN

R138

2.7K

2.7K

IC100-*2

R1EX24256BSAS0A

NVRAM_RENESAS

3

A2

2

A1

4

VSS

1

A0

5

SDA

6

SCL

7

WP

8

VCC

MODEL_OPT_10

COMP1_DET

R130

4.7K

MODULE_V13

OSDA2

MT5398_TS_IN[7]

R156

1K

1K

R176

1K

1K

PWM2_PULL_DOWN_1K

/TU_RESET1

MT5398_TS_IN[1]

LED_PWM1

R116

33

OPCTRL_1_SCL

AMP_RESET_N

IC100-*1

M24256-BRMN6TP

NVRAM_ST

3

E2

2

E1

4

VSS

1

E0

5

SDA

6

SCL

7

WC

8

VCC

SOC_TX

L/DIM0_MOSI

RF_SWITCH_CTL

/CI_CD2

STB_SDA

MODEL_OPT_2

MT5398_TS_IN[3]

R105

4.7K

Country_TW

I2C_SDA2

R154

1K

1K

OPT

MODEL_OPT_1

L/DIM0_VS

MT5398_TS_IN[0]

LED_PWM0

/S2_RESET

FE_DEMOD1_TS_CLK

/CI_CD1

+3.3V_NORMAL

R144

4.7K

NON_DDR_0.78G

CI_DATA[0-7]

R102

4.7K

OPT

FE_DEMOD1_TS_VAL

R103

4.7K

NON_Country_TW

MT5398_TS_IN[6]

/PCM_IORD

R129

4.7K

MTK_DDR_1.5GB

AMP_RESET_SOC

/USB_OCD2

I2C_SCL5

R145

4.7K

MTK_DVB_S_TUNER

R153

2.7K

2.7K

NON_TU_Q_KR

MT5398_MISTRT

R121

1.2K

1.2K

R158

22

OPCTRL_11_SCL

MT5398_TS_IN[4]

MODEL_OPT_9

M_REMOTE_RX

SMARTCARD_CLK/SD_EMMC_DATA[0]

C110

0.1uF

0.1uF

I2C_SCL1

+3.3V_NORMAL

I2C_SCL_MICOM

MT5398_TS_SYNC

WOL/ETH_POWER_ON

M_REMOTE_TX

I2C_SDA1

MT5398_TS_OUT[0-7]

R162

1K

1K

R118

33

OPCTRL7

R148

4.7K

MTK_NON_EPI

MT5398_XTAL_IN

FE_DEMOD1_TS_SYNC

R133

2.7K

2.7K

PCM_RST

R131

4.7K

MTK_DDR_1.25GB

R120

33

R157

1K

1K

OPT

VDD3V3

LED_PWM1

R190

10K

D100

100V

1N4148W

OTP_WRITE

R180

4.7K

+3.3V_NORMAL

OTP_WRITE

VDD3V3

R194

10K

R195

10K

Q100

PMV48XP

G

D

S

C115-*1

2.7pF

50V

2.7pF

50V

ATSC_2.7pF

C114-*1

2.7pF

50V

2.7pF

50V

ATSC_2.7pF

#SIL_RESET

R153-*1

1.5K

TU_Q_KR

R152-*1

1.5K

TU_Q_KR

C114

1.0pF

50V DVB_1pF

1.0pF

50V DVB_1pF

C115

1.0pF

50V

1.0pF

50V

DVB_1pF

X100

27MHz

4

GND_2

1

X-TAL_1

2

GND_1

3

X-TAL_2

/RST_HUB

/RST_HUB

CAM_SLIDE_DET

CAM_SLIDE_DET

R196

240

240

IC105

LGE2122[A2_M13]

JTCK

AK10

JTDI

AK11

JTDO

AL9

JTMS

AJ11

JTRST

AJ12

OSDA0

AH11

OSCL0

AH10

OSDA1

AF11

OSCL1

AG11

XTALI

AN29

XTALO

AM29

AVDD33_XTAL_STB

AN30

AVSS33_XTAL_STB

AL29

AVDD33_VGA_STB

AN17

AVSS33_AVSS33_VGA_STB

AL17

AVDD33_PLL

AL26

AVSS33_PLLGP

AC21

AVSS33_CPUPLL

H21

AVDD10_LDO

AM17

AVDD10_ELDO

AN16

U0TX

AH15

U0RX

AH14

U1TX

AH13

U1RX

AG13

POWE

D24

POOE

B25

POCE1

D25

POCE0

A25

PDD7

C22

PDD6

B22

PDD5

A22

PDD4

C23

PDD3

A23

PDD2

B23

PDD1

D23

PDD0

C24

PARB

C25

PACLE

A26

PAALE

B26

EMMC_CLK

C21

OPWRSB

AL15

ORESET

AK20

OIRI

AF17

FSRC_WR

C20

STB_SCL

AL14

STB_SDA

AK15

POR_BND

AE14

IC105

LGE2122[A2_M13]

GPIO0

B30

GPIO1

A31

GPIO2

B31

GPIO3

A32

GPIO4

C30

GPIO5

A33

GPIO6

B32

GPIO7

C31

GPIO8

E30

GPIO9

F29

GPIO10

F27

GPIO11

F28

GPIO12

C32

GPIO13

F30

GPIO14

F32

GPIO15

D30

GPIO16

D32

GPIO17

F31

GPIO18

F33

GPIO19

E31

GPIO20

E32

GPIO21

D31

GPIO22

D33

GPIO23

E29

GPIO24

C33

GPIO25

B33

GPIO26

A30

GPIO27

E28

GPIO28

C29

GPIO29

J28

GPIO30

H29

GPIO31

J26

GPIO32

G30

GPIO33

G27

GPIO34

E27

GPIO35

D29

GPIO36

D28

GPIO37

H28

GPIO38

J27

GPIO39

G29

GPIO40

G31

GPIO41

G28

GPIO42

B28

GPIO43

K28

GPIO44

E25

GPIO45

D21

GPIO46

G23

GPIO47

C28

GPIO48

F24

GPIO49

AB8

GPIO50

AA7

GPIO51

AD6

GPIO52

AC8

GPIO53

AC7

GPIO54

AB6

GPIO55

AC6

ADIN0_SRV

AJ23

ADIN1_SRV

AH23

ADIN2_SRV

AE28

ADIN3_SRV

AD28

ADIN4_SRV

AF22

ADIN5_SRV

AK21

ADIN6_SRV

AG24

ADIN7_SRV

AM18

DEMOD_RST

P30

DEMOD_TSCLK

N32

DEMOD_TSDATA0

R27

DEMOD_TSDATA1

T26

DEMOD_TSDATA2

T27

DEMOD_TSDATA3

P26

DEMOD_TSDATA4

R28

DEMOD_TSDATA5

U27

DEMOD_TSDATA6

U26

DEMOD_TSDATA7

R26

DEMOD_TSSYNC

R29

DEMOD_TSVAL

P27

CI_INT

L25

CI_TSCLK

N33

CI_TSDATA0

K26

CI_TSSYNC

N30

CI_TSVAL

N31

PVR_TSCLK

M31

PVR_TSVAL

M27

PVR_TSSYNC

L27

PVR_TSDATA0

M29

PVR_TSDATA1

M30

SPI_CLK1

L30

SPI_CLK

L33

SPI_DATA

L32

SPI_CLE

K27

OPWM2

AL8

OPWM1

AM8

OPWM0

AM9

SD_D0

D27

SD_D1

C27

SD_D2

D26

SD_D3

C26

SD_CMD

A28

SD_CLK

E24

LED_PWM1

AF15

LED_PWM0

AG15

OPCTRL11

AL16

OPCTRL10

AM16

OPCTRL9

AE17

OPCTRL8

AG19

OPCTRL7

AH17

OPCTRL6

AE19

OPCTRL5

AH19

OPCTRL4

AK16

OPCTRL3

AG17

OPCTRL2

AJ17

OPCTRL1

AF19

OPCTRL0

AJ19

R152-*2

1.2K

TU_N_TW/BR

R153-*2

1.2K

TU_N_TW/BR

8

MID_MAIN_1

2011.12.13

HDCP EEPROM

CI SLOT -> SOC

MODEL_OPT_4

I2C

NON_DDR_0.78G

GPIO45(EMMC_RST) is dedicated to reset

EMMC for improving A1’s leakage current

EMMC for improving A1’s leakage current

X-TAL

DDR_1.25G

MODEL_OPT_4

Support

CI SLOT -> SOC

NVRAM

HD

Write Protection

- Low : Normal Operation

- High : Write Protection

- High : Write Protection

Not Support

CP BOX

CI SLOT -> SOC

SOC -> CI SLOT

EAX64797001* : LD33B

EAX64872101* : LA33B

EAX64872101* : LA33B

Support

MODEL_OPT_2

Disable

Non_AJJA

Module

EPI

Close to eMMC Flash

(IC8100)

(IC8100)

Enable

MODEL_OPT_8

MODEL_OPT_9

Model Option

EXTERNAL DEMOD

-> SOC

-> SOC

AJJA

T2 Tuner

MODEL_OPT_5

DDR_1.5G

MODEL_OPT_7

Not Support

MODEL_OPT_6

DDR

Wake On Lan

Not Support

STRAPPING LED_PWM0 LED_PWM1 OPCTRL3 OPCTRL7

ICE mode + 27M + serial boot 1 0 0 0

ICE mode + 27M + ROM to Nand boot 1 0 0 1

ICE mode + 27M + ROM to 60bit ECC Nand boot 1 0 1 0

ICE mode + 27M + ROM to eMMC boot from 1 0 1 1

EMMC pins (share pins w/s NAND)

EMMC pins (share pins w/s NAND)

ICE mode + 27M + ROM to eMMC 1 1 0 0

Boot from SDIO pins

Boot from SDIO pins

Support

SOC -> CI SLOT

FHD

MODEL_OPT_3

DDR

MODEL_OPT_10

CI SLOT -> SOC

S Tuner

5V Tolerance

I2C_1 : AMP, L/DIMMING,HDCP KEY

I2C_2 : T-CON,

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod, LNB, MHL(Sil1292)

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

I2C_2 : T-CON,

I2C_3 : MICOM

I2C_4 : S/Demod,T2/Demod, LNB, MHL(Sil1292)

I2C_5 : NVRAM

I2C_6 : TUNER_MOPLL(T/C,ATV)

MODEL_OPT_1

Non_TW

MODEL_OPT_0

No FRC(60Hz)

LOW

HIGH

FRC(120Hz)

Country_TW

FRC

V12

V13

Panel

Country_AJJA

DDR_0.78G

MODEL_OPT_5

MODEL_OPT_9

DDR_1.25G

DDR_1.5G

DDR_0.768G

High

Low

Low

Low

High

High

TW

MODEL_OPT_4

Click on the first or last page to see other 32LN570B (CHASSIS:LA33B) service manuals if exist.