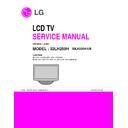

LG 32LH255H (CHASSIS:LA96C) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

IF_AGC

+5V_TU

0 . 1 u F

C1021

OPT

3216

10uF

16V

C1028

+1.2V_DVDD_PVSB

FE_SIF

+3.3V_PVSB

47

R1016

OPT

FE_TUNER_SCL

10K

R1008

3216

10uF

16V

C1023

3216

10uF

16V

16V

C1038

0 . 0 1 u F

50V

C1009

0

5%

1/4W

R1034

+1.2V_PVSB

12K

R1007

+3.3V_AVDD_PVSB

6.8uH

L1004

SIFMO

470

R1010

0 . 1 u F

50V

C1007

4.7K

R1013

2.2K

R1004

OPT

VCOMO

0 . 0 4 7 u F

50V

C1012

0 . 1 u F

50V

C1005

10K

R1006

OPT

+3.3V_DVDD_PVSB

4.7K

R1017

+5V_TU

FE_TUNER_SDA

+3.3V_PVSB

0

R1005

+5V_GENERAL

VSB_CTRL

0 . 1 u F

50V

50V

C1020

100uF

16V

OPT

C1002

100uF

16V

C1018

MLB-201209-0120P-N2

OPT

L1000

+3.3V_PVSB

8.2K

OPT

R1015

15K

OPT

R1014

4.7K

OPT

R1001

1K

OPT

R1002

0 . 1 u F

50V

OPT

50V

OPT

C1003

+3.3V_FE

SC156515M-1.8TR

OPT

IC1001

2

VIN

1

EN

3

GND

5

ADJ

4

VO

VSB_RESET

TS_0

0 . 1 u FC1068

1K

R1063

TS_SYNC

25MHz

X1005

22R1077

0 . 1 u F

C1067

0

R1065

OPT

TS_VALID

100

AR1070

+3.3V_DVDD_PVSB

TS_CLK

22 R1078

27pF

C1072

+3.3V_DVDD_PVSB

0

R1073

470

R1069

1/16W

100

AR1079

LD1000

FE_DEMOD_SCL

27pF

C1071

1N4148W

D1000

1M

R1072

FE_DEMOD_SDA

+3.3V_AVDD_PVSB

+3.3V_AVDD_PVSB

1uF

10V

10V

C1073

100

AR1071

OPT

R1076

47K

R1074

0 . 0 1 u F

C1070

OPT

R1075

OPT

R1066

+1.2V_DVDD_PVSB

IF_AGC

IF_N

0 . 0 1 u F

C1069

5.1K

R1068

OPT

1K

R1060

100

R1064

I F _ P

0 . 1 u F

50V

50V

C1026

0 . 1 u F

50V

C1030

0 . 1 u F

50V

C1032

0 . 1 u F

50V

C1033

0 . 1 u F

50V

C1043

0 . 1 u F

50V

50V

C1044

0 . 1 u F

C1066

100

R1061

100

R1062

AS7809DTRE1

IC1003

2

GND

3

OUTPUT

1

INPUT

100uF

16V

C1035

0 . 1 u F

16V

16V

C1037

OPT

0 . 0 1 u F

25V

25V

C1041

0 . 1 u F

16V

C1034

47uF

16V

16V

C1039

PANEL_POWER

KIA78R05F

IC1002

1

VIN

2

VC

3

VOUT

4

NC

5

GND1

6

GND2

0 . 1 u F

C1040

BG2012B800

L1010

100

R1028

OPT

FE_VMAIN

008:D24

0

R1021

0.1uF

50V

C1014

270

R1019

+5V_TU

0

OPT

R1018

270

R1020

+5V_TU

0 . 0 1 u F

25V

C1008

10uF

10V

10V

C1011

22

R1023

22

R1022

0

R1027

0

R1026

27pF

50V

OPT

C1024

27pF

50V

50V

OPT

C1025

100pF

50V

50V

C1017

100pF

50V

C1015

L1012

L1001

82pF

50V

50V

C1004

500

L1005

500

L1003

500

L1007

500

L1008

220uF

16V

16V

C1013

0

OPT

R1031

0

R1033

0

R1032

ISA1530AC1

Q1001

E

B

C

ISA1530AC1

Q1000

Q1000

E

B

C

OPT

R1067

1uF

16V

C1076

20K

R1011

100

R1035

OPT

SC4215ISTRT

IC1000

3

VIN

2

EN

4

NC_2

1

NC_1

5

NC_3

6

VO

7

ADJ

8

GND

POWER_EN

008:AR30;004:X17;004:AM17

100uF

16V

C1019

+1.2V_PVSB

0 . 1 u F

50V

50V

C1079

10K

R1012

0

R1003

100uF

16V

16V

C1082

0 . 1 u F

16V

C1081

0 . 3 3 u F

16V

C1036

+5V_TU

IF_P

IF_N

LGDT3305

IC1004

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

CB3216PA501E

L1219

0 . 1 u F

50V

50V

C2138

100pF

50V

50V

OPT

C1027

20K

R1036

0

OPT

R1009

220uF

16V

16V

C2250

0

L1014

5%

1/10W

0

L1013

5%

1/10W

TS_1

TS_2

TS_3

TS_4

TS_5

TS_6

TS_7

47pF

C1006

270nH

L1002

TDVW-H104P

TU1001

14

NC_3

13

S I F

5

RF_AGC

12

IF_AGC

11

D I F [ - ]

2

NC_2

10

D I F [ + ]

4

+B1[5V]

1

NC_1

9

AS

8

CLOCK

3

GND_1

16

VIDEO

7

DATA

6

GND_2

15

AUDIF

17

SHIELD

2 . 2 u F

25V

25V

C1078

2 . 2 u F

25V

C1077

SIGN273

TS_0

TS_1

TS_2

TS_3

TS_4

TS_5

TS_6

TS_7

VSB +1.0V B+ BLOCK

VSB +3.3V B+ BLOCK

VDD33

VSSAD10

VCCAAD10A

VDD

VSS33

SLIM_SCAN

OPM

VSS

XTALI

TPDATA[1]

TPDATA[2]

TPDATA[3]

TPDATA[4]

TPDATA[5]

TPDATA[6]

TPERR

TPDATA[7]

VDD33

TPVALID

TPDATA[0]

VSS33

VSSAAD10A

IF OUT

I2CRPT_SDA

I2CRPT_SCL

VINA1

I2CSEL

VINA2

RF OUT

VDD

INCAP

ANTCON

VROA

VSS

VDD33

SCL

TPCLK

SDA

VSS33

VDD

PLLAVDD

PLLAVSS

TPSOP

VSS

NIRQ

XM

XTALO

NRST

C l o s e t o t u n e r

( I 2 C C h a n n e l 6 )

V 0 = 0 . 8 ( R 1 + R 2 ) / R 2

R1

R2

M e r c u r y O p t i o n

T u n e r / 3 3 0 5

5 1 4

F M R e j e c t i o n O p t i o n

T h e v a l u e o f c o i l & c a p ’ c o u l d b e c h a n g e d t o o p t i m i z e d e a c h

M S t a r O p t i o n

M S t a r O p t i o n

TUNER 5V

LGDT3305 POWER

TUNER

LGDT3305

37LH250H

0 9 . 0 5 . 1 9

TUNER

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

56

R40

0.1uF

C38

56

R41

56

AR5

56

AR7

56

R39

0.1uF

C25

0.1uF

C32

0 . 1 u F

C22

56

AR10

56

AR3

10uF

C30

56

R21

56

R16

56

R6

0.1uF

C31

1000pF

C18

56

R34

56

R10

10uF

C13

0.1uF

C20

1000pF

C2

0.1uF

C27

0.1uF

C11

0.1uF

C24

10uF

C3

1K

1%

R24

0.1uF

C37

56

R35

56

R14

56

R17

+1.8V_S_DDR

56

AR8

0.1uF

C41

56

R19

1K

1%

R5

56

R15

56

R20

1K

1%

R23

0.1uF

C8

0.1uF

C34

0.1uF

C29

0.1uF

C14

+1.8V_S_DDR

56

AR13

56

R29

56

AR1

56

AR4

0.1uF

C10

56

R42

56

R33

56

R12

56

R38

0.1uF

C17

0.1uF

C39

56

AR12

56

AR9

56

R11

0.1uF

C5

56

R28

BLM18PG121SN1D

L1

56

R27

56

AR11

0.1uF

C35

1000pF

C42

0.1uF

C7

56

R13

56

R30

+1.8V_DDR

56

AR2

1K

1%

R4

0.1uF

C6

56

AR14

0.1uF

C4

0 . 1 u F

C40

56

R18

0.1uF

C43

56

R37

0.1uF

C15

0.1uF

C12

56

R43

0 . 1 u F

C1

150

OPT

R2

150

OPT

R45

0.1uF

C33

1K

1%

R44

56

R36

0.1uF

C9

56

AR6

+1.8V_S_DDR

10uF

C23

+1.8V_S_DDR

0.1uF

C19

0.1uF

C16

+1.8V_S_DDR

0.1uF

C21

56

R7

0.1uF

C36

1K

1%

R47

56

R22

33

R8

33

R9

33

R32

33

R31

+1.8V_S_DDR

+1.8V_S_DDR

+1.8V_S_DDR

0

R50

OPT

0

R51

0

R49

0

R48

OPT

LGE3369A (SATURN6 NON RM)

IC100

B_DDR2_A0

T26

B_DDR2_A1

AF26

B_DDR2_A2

T25

B_DDR2_A3

AF23

B_DDR2_A4

T24

B_DDR2_A5

AE23

B_DDR2_A6

R26

B_DDR2_A7

AD22

B_DDR2_A8

R25

B_DDR2_A9

AC22

B_DDR2_A10

AD23

B_DDR2_A11

R24

B_DDR2_A12

AE22

B_DDR2_BA0

AC23

B_DDR2_BA1

AC24

B_DDR2_BA2

AB22

B_DDR2_MCLK

V25

/B_DDR2_MCLK

V24

B_DDR2_CKE

AB23

B_DDR2_ODT

U26

/B_DDR2_RAS

U25

/B_DDR2_CAS

U24

/B_DDR2_WE

AB24

B_DDR2_DQS0

AB26

B_DDR2_DQS1

AA26

B_DDR2_DQM0

AC25

B_DDR2_DQM1

AC26

B_DDR2_DQSB0

AB25

B_DDR2_DQSB1

AA25

B_DDR2_DQ0

W25

B_DDR2_DQ1

AE26

B_DDR2_DQ2

W24

B_DDR2_DQ3

AF24

B_DDR2_DQ4

AF25

B_DDR2_DQ5

V26

B_DDR2_DQ6

AE25

B_DDR2_DQ7

W26

B_DDR2_DQ8

Y26

B_DDR2_DQ9

AD25

B_DDR2_DQ10

Y25

B_DDR2_DQ11

AE24

B_DDR2_DQ12

AD26

B_DDR2_DQ13

Y24

B_DDR2_DQ14

AD24

B_DDR2_DQ15

AA24

A_MVREF

D15

A_DDR2_A0

C13

A_DDR2_A1

A22

A_DDR2_A2

B13

A_DDR2_A3

C22

A_DDR2_A4

A13

A_DDR2_A5

A23

A_DDR2_A6

C12

A_DDR2_A7

B23

A_DDR2_A8

B12

A_DDR2_A9

C23

A_DDR2_A10

B22

A_DDR2_A11

A12

A_DDR2_A12

A24

A_DDR2_BA0

C24

A_DDR2_BA1

B24

A_DDR2_BA2

D24

A_DDR2_MCLK

B14

/A_DDR2_MCLK

A14

A_DDR2_CKE

D23

A_DDR2_ODT

D14

/A_DDR2_RAS

D13

/A_DDR2_CAS

D12

/A_DDR2_WE

D22

A_DDR2_DQS0

B18

A_DDR2_DQS1

C17

A_DDR2_DQM0

C18

A_DDR2_DQM1

A19

A_DDR2_DQSB0

A18

A_DDR2_DQSB1

B17

A_DDR2_DQ0

B15

A_DDR2_DQ1

A21

A_DDR2_DQ2

A15

A_DDR2_DQ3

B21

A_DDR2_DQ4

C21

A_DDR2_DQ5

C14

A_DDR2_DQ6

C20

A_DDR2_DQ7

C15

A_DDR2_DQ8

C16

A_DDR2_DQ9

C19

A_DDR2_DQ10

B16

A_DDR2_DQ11

B20

A_DDR2_DQ12

A20

A_DDR2_DQ13

A16

A_DDR2_DQ14

B19

A_DDR2_DQ15

A17

H5PS5162FFR-S6C

IC2

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

HY5PS1G1631CFP-S6

IC1

J 2

VREF

J 8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

BA2

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J 7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J 1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J 3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J 9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

SDDR_A[4]

BDDR2_D[15]

TDDR_D[4]

SDDR_A[0]

TDDR_A[8]

SDDR_D[8]

TDDR_D[12]

ADDR2_D[0]

TDDR_D[9]

ADDR2_DQM1_P

BDDR2_D[3]

ADDR2_D[0-15]

TDDR_D[8]

BDDR2_A[0]

ADDR2_A[2]

SDDR_A[2]

BDDR2_A[10]

TDDR_D[11]

BDDR2_BA[1]

TDDR_A[10]

ADDR2_D[13]

ADDR2_D[13]

TDDR_D[10]

SDDR_D[3]

ADDR2_D[9]

ADDR2_A[0]

TDDR_D[7]

ADDR2_DQS0_N

ADDR2_A[8]

ADDR2_D[0]

/BDDR2_MCLK

SDDR_D[8]

ADDR2_A[10]

TDDR_BA[0]

TDDR_A[7]

BDDR2_A[3]

TDDR_A[11]

BDDR2_A[5]

SDDR_D[11]

ADDR2_A[12]

SDDR_A[4]

BDDR2_D[13]

ADDR2_A[1]

ADDR2_DQS1_P

SDDR_D[6]

ADDR2_D[5]

TDDR_D[13]

ADDR2_A[0]

BDDR2_D[13]

ADDR2_A[5]

BDDR2_A[11]

ADDR2_D[12]

BDDR2_D[14]

BDDR2_D[11]

BDDR2_A[2]

SDDR_A[12]

TDDR_D[9]

SDDR_D[2]

ADDR2_A[5]

ADDR2_BA[1]

ADDR2_A[12]

SDDR_A[5]

BDDR2_D[1]

ADDR2_CKE

ADDR2_A[2]

BDDR2_A[7]

BDDR2_D[7]

ADDR2_A[7]

TDDR_D[14]

SDDR_A[11]

ADDR2_D[6]

TDDR_A[2]

SDDR_A[0]

SDDR_D[4]

BDDR2_D[0]

BDDR2_A[4]

BDDR2_A[12]

BDDR2_D[6]

BDDR2_D[1]

SDDR_D[5]

BDDR2_D[3]

BDDR2_DQM1_P

SDDR_D[0-15]

SDDR_D[0]

ADDR2_A[1]

BDDR2_A[5]

BDDR2_D[2]

ADDR2_DQM0_P

BDDR2_A[7]

TDDR_D[7]

BDDR2_D[10]

BDDR2_DQS0_P

ADDR2_D[2]

ADDR2_D[8]

ADDR2_D[10]

BDDR2_A[4]

SDDR_D[1]

SDDR_D[14]

TDDR_A[6]

TDDR_A[9]

ADDR2_A[6]

TDDR_D[1]

BDDR2_A[12]

TDDR_D[15]

BDDR2_D[5]

BDDR2_CKE

SDDR_D[13]

BDDR2_D[7]

SDDR_A[9]

SDDR_D[14]

TDDR_D[8]

ADDR2_BA[0]

BDDR2_D[4]

TDDR_D[5]

BDDR2_DQM0_P

SDDR_D[12]

SDDR_A[6]

SDDR_A[8]

TDDR_D[13]

ADDR2_ODT

SDDR_D[4]

SDDR_A[2]

SDDR_D[10]

BDDR2_D[14]

ADDR2_D[15]

TDDR_A[4]

SDDR_D[11]

/ADDR2_MCLK

BDDR2_D[12]

ADDR2_DQS1_N

ADDR2_D[12]

SDDR_A[10]

SDDR_A[1]

SDDR_D[1]

BDDR2_A[11]

BDDR2_DQS0_N

ADDR2_D[8]

SDDR_BA[0]

BDDR2_A[1]

ADDR2_D[15]

SDDR_A[9]

BDDR2_D[9]

TDDR_D[6]

ADDR2_D[3]

ADDR2_DQS0_P

ADDR2_D[14]

BDDR2_A[6]

/ADDR2_CAS

SDDR_A[7]

TDDR_D[12]

TDDR_A[8]

BDDR2_BA[0]

TDDR_D[11]

ADDR2_A[11]

TDDR_A[0-12]

SDDR_D[10]

BDDR2_A[0]

BDDR2_D[8]

BDDR2_DQS1_P

ADDR2_D[10]

ADDR2_A[7]

SDDR_A[6]

TDDR_D[3]

BDDR2_D[9]

SDDR_DQS1_N

ADDR2_D[14]

ADDR2_A[11]

TDDR_A[3]

TDDR_A[7]

BDDR2_D[5]

BDDR2_A[8]

/BDDR2_WE

BDDR2_ODT

BDDR2_D[0-15]

SDDR_A[3]

TDDR_D[0]

BDDR2_D[15]

SDDR_A[7]

TDDR_D[1]

SDDR_DQM1_P

SDDR_D[13]

ADDR2_A[4]

TDDR_D[5]

TDDR_A[0]

ADDR2_D[5]

TDDR_A[12]

SDDR_D[5]

TDDR_D[15]

ADDR2_D[7]

SDDR_A[0-12]

SDDR_BA[1]

SDDR_D[0]

TDDR_D[0-15]

SDDR_D[7]

BDDR2_A[6]

ADDR2_D[6]

SDDR_A[11]

SDDR_A[8]

SDDR_A[5]

SDDR_D[6]

TDDR_D[2]

TDDR_A[9]

ADDR2_A[9]

SDDR_D[15]

ADDR2_D[7]

SDDR_A[3]

SDDR_DQS1_P

SDDR_A[12]

SDDR_D[15]

BDDR2_A[0-12]

TDDR_D[10]

TDDR_D[6]

BDDR2_A[9]

TDDR_A[1]

ADDR2_D[1]

BDDR2_A[10]

/ADDR2_WE

BDDR2_D[8]

/SDDR_WE

ADDR2_A[4]

ADDR2_A[3]

ADDR2_A[10]

BDDR2_A[3]

ADDR2_MCLK

TDDR_A[3]

SDDR_D[9]

ADDR2_D[1]

BDDR2_DQS1_N

SDDR_A[1]

ADDR2_A[0-12]

BDDR2_D[4]

TDDR_A[0]

/BDDR2_CAS

TDDR_D[14]

BDDR2_D[12]

BDDR2_D[6]

BDDR2_D[0]

SDDR_D[12]

/BDDR2_RAS

BDDR2_D[10]

TDDR_A[10]

TDDR_A[4]

TDDR_D[4]

TDDR_A[2]

TDDR_D[0]

ADDR2_D[2]

/ADDR2_RAS

BDDR2_A[2]

TDDR_A[5]

BDDR2_A[1]

BDDR2_MCLK

SDDR_D[9]

SDDR_D[2]

BDDR2_D[2]

BDDR2_A[8]

SDDR_CKE

TDDR_A[6]

ADDR2_D[9]

BDDR2_D[11]

TDDR_D[3]

ADDR2_D[4]

ADDR2_D[11]

TDDR_BA[1]

ADDR2_D[11]

TDDR_A[5]

TDDR_D[2]

ADDR2_A[8]

ADDR2_A[9]

SDDR_D[7]

BDDR2_A[9]

ADDR2_A[3]

SDDR_A[10]

ADDR2_D[3]

SDDR_D[3]

TDDR_A[12]

ADDR2_D[4]

ADDR2_A[6]

TDDR_A[11]

TDDR_A[1]

ADDR2_BA[2]

BDDR2_BA[2]

SDDR_CK

SDDR_ODT

/SDDR_RAS

/SDDR_CAS

SDDR_DQS0_P

SDDR_DQM0_P

SDDR_DQS0_N

TDDR_BA[2]

TDDR_MCLK

TDDR_CKE

/TDDR_WE

TDDR_DQM1_P

TDDR_DQS1_N

DDR2

6 1 4

DDR2 1.8V By CAP - Place these Caps near Memory

DDR

37LH250H

512M_HYNIX

1G_HYNIX

0 9 . 0 5 . 1 9

DDR

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MDS61887701

GAS1

22uF

25V

C2259

PANEL_POWER

1000pF

C2257

0.1uF

OPT

C2258

0

R845

BIT_SEL

0

R844

OPT

0

OPT

R841

OPC_EN

OPC_OUT

LVDS_SEL

008:AR30;007:O14

PWM_DIM

LVDS_TXA2+

LVDS_TXA0+

LVDS_TXA3+

LVDS_TXA2-

LVDS_TXA0-

LVDS_TXA1+

TXA1+[8]

TXA4-[1]

0

Except FHD

R847

0

Except FHD

R850

TXAC-[5]

0

Except FHD

R851

TXA2-[7]

LVDS_TXA1-

TXA3+[2]

LVDS_TXAC-

TXA2+[6]

0

Except FHD

R848

0

Except FHD

R856

TXAC+[4]

TXA1-[9]

0

Except FHD

R849

0

Except FHD

R853

LVDS_TXAC+

TXA3-[3]

LVDS_TXA3-

TXA4+[0]

0

Except FHD

R854

0

Except FHD

R855

0

Except FHD

R852

LVDS_TXA0-

LVDS_TXA0+

LVDS_TXA3-

LVDS_TXA1-

LVDS_SEL

008:AR30;007:Z21

LVDS_TXAC+

0

R859

OPT

0

OPT

R857

0

R860

OPT

PWM_DIM

0 0 8 : A F 1 1 ; 0 0 4 : M 2 0 ; 0 0 7 : Z 2 1

OPC_OUT

0 0 4 : M 1 9 ; 0 0 7 : Z 2 1

LVDS_TXA2-

OPC_EN

008:AQ28;007:Z20

LVDS_TXA2+

0

OPT

R858

GND

GND

FI-X30SSL-HF

Except FHD

P800

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

LVDS_TXAC-

LVDS_TXA1+

LVDS_TXA3+

0

OPT

R842

0

OPT

R843

0

OPT

R840

PANEL_POWER

10K

R861

OPT

+3.3V_ST

0

R4000

OPT

+3.3V_ST

10K

OPT

R862

0

R863

OPT

TF05-51S

FHD

P801

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

TXB0-[11]

TXB0+[10]

TXB1-[9]

TXB1+[8]

TXB2-[7]

TXB2+[6]

TXBC-[5]

TXBC+[4]

TXB3-[3]

TXB3+[2]

TXB4-[1]

TXB4+[0]

TXA0-[11]

TXA0+[10]

TXA1-[9]

TXA1+[8]

TXA2-[7]

TXA2+[6]

TXAC-[5]

TXAC+[4]

TXA3-[3]

TXA3+[2]

TXA4-[1]

TXA4+[0]

LVDS

7

14

LVDS

37LH250H

0 9 . 0 5 . 1 9

Click on the first or last page to see other 32LH255H (CHASSIS:LA96C) service manuals if exist.