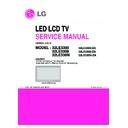

LG 32LE3300 / 32LE3308 / 32LE330N (CHASSIS:LD01D) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

B-MA0

A-TMDML

A-TMWEB

B-TMDQU6

A-MDQL2

A-MDQU4

B-TMDQL3

A-MDQSLB

B-TMDQU6

B-TMA7

A-TMCKE

A-TMCKB

B-MDMU

C1236

0.1uF

A-MDQSLB

A-MA10

A-TMA10

B-TMCKB

A-TMA3

B-TMDQSUB

B-TMWEB

B-TMA3

A-TMODT

A-TMDQU0

A-TMDQSU

B-TMDQL6

B-TMCKE

A-TMBA1

B-MODT

B-MDQU2

B-MVREFDQ

B-MDQL0

B-TMA5

B-TMCASB

B-TMBA1

VCC_1.5V_DDR

A-MBA0

A-TMDQU6

A-MDQU2

A-MDQL7

B-MDQSLB

A-MVREFCA

B-MA9

B-MA2

A-MDQL3

A-MODT

B-MDQL4

A-TMDQU0

B-TMA13

A-MCKB

A-TMDQL7

B-TMDQU2

B-MRASB

B-TMDQU4

B-MDQU6

A-TMDQU3

B-MA7

B-MDQU7

B-TMDQL4

A-TMA2

A-MDQL0

B-TMODT

A-MDQSU

L1201

A-MBA1

B-MDQU6

A-TMODT

B-MWEB

B-MDQL6

A-MCKE

A-TMDQL1

A-TMA12

A-MDQL1

C1231

0.1uF

B-MVREFCA

A-TMRASB

B-MDQL1

A-TMDQL7

A-TMDQL6

A-MDQU7

A-MDQU6

C1227

0.1uF

A-MDQL3

B-MCASB

A-MDQU3

B-TMA10

B-TMA11

+1.5V_DDR

A-TMCK

A-MDQL4

B-MA5

B-TMODT

B-TMA12

A-MCK

C1239

0.1uF

A-TMA2

A-MA9

C1221

0.1uF

B-MDQL2

A-TMDQL0

B-TMDQU7

A-MCASB

B-TMDQU3

B-TMA1

A-MDQL6

B-MA8

B-MA3

A-TMCK

B-MDQU1

C1238

0.1uF

C1244

0.1uF

B-MA12

A-TMRASB

A-MA3

A-TMRESETB

B-TMRASB

A-MA5

A-TMDQL4

C1226

0.1uF

16V

0.1uF

16V

A-MVREFDQ

C1202

1000pF

B-MDQL4

C1230

0.1uF

A-MA11

C1235

0.1uF

R1202

1K

1%

A-TMCASB

A-MA2

B-TMA7

R1224

1K

1%

A-MCK

B-MCK

B-MDQU5

A-MDQU5

A-TMDQU2

B-TMCASB

B-TMA4

B-TMDQL0

C1219

0.1uF

B-TMDQL7

C1201

0.1uF

B-TMDQL4

B-TMDQL2

B-MODT

C1206

0.1uF

B-TMCK

B-TMDQU1

B-TMDQL2

C1224

0.1uF

A-MDQU6

R1228

1K

1%

B-TMDQU0

C1232

0.1uF

B-MDQU7

A-MA9

A-TMA0

A-MDQL1

B-TMDQL5

R1203

240

1%

B-TMA6

C1242

0.1uF

B-MA9

B-TMDQL1

A-TMA4

B-TMA12

A-MODT

B-TMDML

B-MDQSUB

B-TMA3

B-MVREFCA

B-MA5

A-MDQSL

A-MA1

B-TMDMU

A-TMDQSL

B-MBA0

C1203

0.1uF

C1237

0.1uF

B-MA12

VCC_1.5V_DDR

A-TMDQL1

A-MA11

B-MCKE

B-MDQSU

B-MDQL7

B-MA4

B-MA4

R1227

1K

1%

A-TMDQSLB

A-MDQU1

B-MDQU5

A-TMCKB

A-TMA6

A-MA6

C1223

0.1uF

VCC_1.5V_DDR

A-TMA8

C1248

0.1uF

B-TMA4

B-MDQL2

A-TMRESETB

C1247

1000pF

B-MDQU2

A-TMDMU

B-TMA9

B-MDQU0

B-TMRESETB

B-TMDQU2

A-TMDMU

B-MA13

C1241

0.1uF

A-MA0

B-TMA8

A-TMDQL5

A-TMDQU6

A-MA4

A-TMDQL3

A-MDML

B-MDQL3

B-MDQU3

B-TMBA0

VCC_1.5V_DDR

R1204

1K

1%

A-MRESETB

A-MWEB

A-TMDQU1

B-MA0

A-TMA13

A-MBA2

A-TMDQSUB

A-TMDQL5

VCC_1.5V_DDR

A-TMBA1

VCC_1.5V_DDR

B-TMDQL6

B-MDQL7

B-TMA10

B-MRESETB

C1214

0.1uF

R1205

1K

1%

A-MA6

B-MA2

B-TMA13

A-TMBA2

C1228

0.1uF

C1208

0.1uF

C1245

0.1uF

A-MRASB

C1210

0.1uF

A-MDQL5

B-MWEB

C1218

0.1uF

A-TMCKE

A-MDQL4

C1229

0.1uF

B-MDQL1

C1233

0.1uF

A-MDQL6

B-TMA11

B-TMDQSU

A-MA3

A-TMDQSL

A-TMDQSLB

R1226

240

1%

A-MA7

B-MA8

A-TMDQL6

A-TMBA0

A-MDQSU

A-MA13

A-MDQSUB

B-MA1

C1250

0.1uF

A-TMA10

B-TMDQU1

B-TMWEB

B-MDQU3

B-TMRESETB

A-MA13

B-TMDML

B-MCKE

B-TMA0

A-MA8

A-MCKB

A-TMDQL3

A-TMA5

A-TMDQU4

A-MA7

B-TMDQSU

A-TMDQSUB

B-MDML

A-MBA2

B-TMDQU4

B-TMA5

A-MDQL2

B-TMDQU0

A-MVREFCA

C1204

1000pF

A-MBA0

C1215

0.1uF

A-MA8

B-MRESETB

B-TMDQSLB

B-TMDQSL

A-MRASB

B-TMA0

B-MBA1

A-TMDQU7

A-MA1

B-MDQU0

A-MDQU0

B-MRASB

B-TMA1

B-TMBA2

A-TMDQL2

A-TMDQU2

A-MRESETB

A-TMDQL2

A-MDQL0

A-TMDML

B-MDQL5

B-TMA8

B-MBA1

A-TMA13

B-MDQSL

B-MDQL3

A-MDQL7

A-TMDQSU

C1212

0.1uF

A-TMA5

A-TMDQU4

B-MDQL0

A-MWEB

B-TMA9

A-TMA0

B-MA10

A-MA12

A-MCKE

B-TMDQSL

A-TMA4

B-TMDQSLB

B-MDQU4

R1225

1K

1%

B-TMDQL1

C1249

1000pF

B-MBA2

B-TMBA1

B-MDQU1

A-MA0

B-MA10

A-MVREFDQ

B-TMDQU7

B-MDQSUB

C1243

0.1uF

A-MDQU2

B-MA13

C1211

0.1uF

A-TMA1

A-MBA1

A-MCASB

B-TMDQL0

B-MDQSL

A-TMA8

B-TMDQL7

A-MDQU3

A-MA5

B-MVREFDQ

B-MA1

B-MDML

B-MDQSU

B-MA6

B-MDMU

B-MCKB

A-MDMU

B-TMDQU5

A-TMDQL0

B-MCK

B-MCASB

A-TMDQU7

A-TMCASB

VCC_1.5V_DDR

A-MA4

VCC_1.5V_DDR

A-MDQU4

B-TMDMU

A-TMA6

A-TMA12

B-TMCK

R1201

1K

1%

B-TMBA2

C1216

0.1uF

C1220

0.1uF

A-MDML

B-TMBA0

VCC_1.5V_DDR

A-MDMU

B-MDQL6

A-MDQU1

B-MBA0

B-TMDQU3

A-TMDQL4

A-MA10

B-TMRASB

B-MCKB

B-MA11

B-MDQU4

A-TMA11

A-TMWEB

A-TMDQU3

B-MA11

B-MBA2

B-TMCKE

B-MDQL5

B-TMDQSUB

A-TMA7

A-TMA9

B-TMA6

B-TMDQL5

B-MA6

A-TMA9

B-MA7

B-MA3

C1222

0.1uF

A-TMA1

A-TMA11

A-MA2

B-TMDQU5

C1217

0.1uF

A-MDQL5

A-TMBA0

C1213

0.1uF

C1207

0.1uF

A-TMDQU1

A-TMDQU5

A-TMDQU5

A-TMBA2

B-TMA2

A-TMA3

C1234

0.1uF

A-MA12

A-MDQU0

B-TMA2

B-MDQSLB

B-TMCKB

A-MDQSUB

A-MDQSL

B-TMDQL3

A-TMA7

A-MDQU7

A-MDQU5

C1205

10uF

C1225

10uF

10V

10uF

10V

C1246

10uF

VCC_1.5V_DDR

R1231

10K

10K

VCC_1.5V_DDR

R1232

10K

R1223

10

R1217

10

R1216

10

R1211

10

R1213

10

R1222

10

R1215

10

R1220

10

R1218

10

R1221

10

R1210

10

R1206

10

R1214

10

R1208

10

R1207

10

R1209

10

R1219

10

R1212

10

AR1218

10

AR1215

10

AR1208

10

AR1219

10

AR1216

10

AR1214

10

AR1211

10

AR1220

10

AR1201

10

AR1202

10

AR1217

10

AR1204

10

AR1207

10

AR1210

10

AR1213

10

AR1209

10

AR1203

10

AR1205

10

AR1212

10

AR1206

10

R1234

10K

B-MCKE

A-MCKE

R1233

10K

H5TQ1G63BFR-H9C

IC1202

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

H5TQ1G63BFR-H9C

IC1201

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J1

NC_2

J9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J2

VSS_6

J8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

R1235

56

1%

R1236

56

1%

C1209

0.01uF

25V

R1237

56

1%

R1238

56

1%

C1240

0.01uF

25V

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX

A_DDR3_A0/DDR2_A13

B8

A_DDR3_A1/DDR2_A8

B9

A_DDR3_A2/DDR2_A9

A8

A_DDR3_A3/DDR2_A1

C21

A_DDR3_A4/DDR2_A2

B10

A_DDR3_A5/DDR2_A10

A22

A_DDR3_A6/DDR2_A4

A10

A_DDR3_A7/DDR2_A3

B22

A_DDR3_A8/DDR2_A6

C9

A_DDR3_A9/DDR2_A12

C23

A_DDR3_A10/DDR2_RASZ

B11

A_DDR3_A11/DDR2_A11

A9

A_DDR3_A12/DDR2_A0

C10

A_DDR3_A13/DDR2_A7

B23

A_DDR3_BA0/DDR2_BA2

B21

A_DDR3_BA1/DDR2_CASZ

A11

A_DDR3_BA2/DDR2_A5

A23

A_DDR3_MCLK/DDR2_MCLK

A12

A_DDR3_MCLKZ/DDR2_MCLKZ

C11

A_DDR3_CKE/DDR2_DQ5

B12

A_DDR3_ODT/DDR2_ODT

C20

A_DDR3_RASZ/DDR2_WEZ

A20

A_DDR3_CASZ/DDR2_BA1

B20

A_DDR3_WEZ/DDR2_BA0

A21

A_DDR3_RESETB

C22

A_DDR3_DQSL/DDR2_DQS0

C16

A_DDR3_DQSLB/DDR2_DQSB0

B16

A_DDR3_DQSU/DDR2_DQSB1

A16

A_DDR3_DQSUB/DDR2_DQS1

C15

A_DDR3_DML//DDR2_DQ13

A14

A_DDR3_DMU/DDR2_DQ6

B18

A_DDR3_DQL0/DDR2_DQ3

C18

A_DDR3_DQL1/DDR2_DQ7

B13

A_DDR3_DQL2/DDR2_DQ1

A19

A_DDR3_DQL3/DDR2_DQ10

C13

A_DDR3_DQL4/DDR2_DQ4

C19

A_DDR3_DQL5/DDR2_DQ0

A13

A_DDR3_DQL6/DDR2_CKE

B19

A_DDR3_DQL7/DDR2_DQ2

C12

A_DDR3_DQU0/DDR2_DQ15

A15

A_DDR3_DQU1/DDR2_DQ9

A17

A_DDR3_DQU2/DDR2_DQ8

B14

A_DDR3_DQU3/DDR2_DQ11

C17

A_DDR3_DQU4/DDR2_DQM1

B15

A_DDR3_DQU5/DDR2_DQ12

A18

A_DDR3_DQU6/DDR2_DQM0

C14

A_DDR3_DQU7/DDR2_DQ14

B17

B_DDR3_A0/DDR2_A13

A25

B_DDR3_A1/DDR2_A8

B24

B_DDR3_A2/DDR2_A9

A24

B_DDR3_A3/DDR2_A1

P25

B_DDR3_A4/DDR2_A2

C24

B_DDR3_A5/DDR2_A10

P26

B_DDR3_A6/DDR2_A4

B26

B_DDR3_A7/DDR2_A3

R24

B_DDR3_A8/DDR2_A6

B25

B_DDR3_A9/DDR2_A12

T26

B_DDR3_A10/DDR2_RASZ

D24

B_DDR3_A11/DDR2_A11

A26

B_DDR3_A12/DDR2_A0

C25

B_DDR3_A13/DDR2_A7

T25

B_DDR3_BA0/DDR2_BA2

P24

B_DDR3_BA1/DDR2_CASZ

C26

B_DDR3_BA2/DDR2_A5

R26

B_DDR3_MCLK/DDR2_MCLK

D26

B_DDR3_MCLKZ/DDR2_MCLKZ

D25

B_DDR3_CKE/DDR2_DQ5

E24

B_DDR3_ODT/DDR2_ODT

N25

B_DDR3_RASZ/DDR2_WEZ

M26

B_DDR3_CASZ/DDR2_BA1

N24

B_DDR3_WEZ/DDR2_BA0

N26

B_DDR3_RESETB

R25

B_DDR3_DQSL/DDR2_DQS0

J25

B_DDR3_DQSLB/DDR2_DQSB0

J24

B_DDR3_DQSU/DDR2_DQSB1

H26

B_DDR3_DQSUB/DDR2_DQS1

H25

B_DDR3_DML/DDR2_DQ13

F26

B_DDR3_DMU/DDR2_DQ6

L24

B_DDR3_DQL0/DDR2_DQ3

L25

B_DDR3_DQL1/DDR2_DQ7

F24

B_DDR3_DQL2/DDR2_DQ1

L26

B_DDR3_DQL3/DDR2_DQ10

F25

B_DDR3_DQL4/DDR2_DQ4

M25

B_DDR3_DQL5/DDR2_DQ0

E26

B_DDR3_DQL6/DDR2_CKE

M24

B_DDR3_DQL7/DDR2_DQ2

E25

B_DDR3_DQU0/DDR2_DQ15

G26

B_DDR3_DQU1/DDR2_DQ9

J26

B_DDR3_DQU2/DDR2_DQ8

G24

B_DDR3_DQU3/DDR2_DQ11

K25

B_DDR3_DQU4/DDR2_DQM1

H24

B_DDR3_DQU5/DDR2_DQ12

K26

B_DDR3_DQU6/DDR2_DQM0

G25

B_DDR3_DQU7/DDR2_DQ14

K24

DDR3(256MB)

GP2_Saturn7M

DDR3 1.5V By CAP - Place these Caps near Memory

DDR3 1.5V By CAP - Place these Caps near Memory

CLose to DDR3

CLose to Saturn7M IC

CLose to Saturn7M IC

Close to DDR Power Pin

Close to DDR Power Pin

CLose to DDR3

Ver. 1.0

21

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPI_SCK

/FLASH_WP

R1402

0

0

R1401

0

OPT

/SPI_CS

R1404

4.7K

C1401

0.1uF

+3.3V_Normal

+3.3V_Normal

Q1401

KRC103S

KRC103S

E

B

C

+3.3V_Normal

R1403

10K

R1405

33

33

SPI_SDO

SPI_SDI

IC1401

MX25L8005M2I-15G

S_FLASH

3

WP#

2

SO

4

GND

1

CS#

5

SI

6

SCLK

7

HOLD#

8

VCC

S-Flash(1MB)

GP2_Saturn7M

Ver. 1.2

23

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

FE_TS_DATA[3]

FE_TS_DATA[6]

FE_TS_DATA[7]

FE_TS_DATA[1]

FE_TS_DATA[4]

FE_TS_DATA[0]

FE_TS_DATA[2]

FE_TS_DATA[5]

R3758

82

82

R3734

0

+5V_TU

C3726

0.1uF

16V

0.1uF

16V

FE_TS_SYNC

R3729

0

CHINA_OPT

R3721

0

CHINA_OPT

C3731

10uF

10V

10uF

10V

OPT

Q3705

ISA1530AC1

E

B

C

R3747

9.1K

1608

CHINA_OPT

R3745

10K

10K

CHINA_OPT

+3.3V_TU

RF_SWITCH_CTL

R3722

0

CHINA_OPT

R3743

10K

CHINA_OPT

R3724

0

CHINA_OPT

C3708

0.1uF

16V

16V

IF_AGC_MAIN

Q3703

ISA1530AC1

E

B

C

R3739

100

CHINA_OPT

+5V_Normal

R3748

4.7K

1608

CHINA_OPT

TU_SIF

IF_AGC_SEL

R3762

0

OPT

TU_CVBS

C3702

0.1uF

16V

C3704

0.1uF

16V

16V

R3731

0

CHINA_OPT

FE_TS_CLK

TUNER_RESET

R3738

100

CHINA_OPT

IC3701

SC4215ISTRT

CHINA_OPT

3

VIN

2

EN

4

NC_2

1

NC_1

5

NC_3

6

VO

7

ADJ

8

GND

R3733

100K

R3730

0

CHINA_OPT

L3703

BLM18PG121SN1D

LNA2_CTL

R3701

0

CHINA_OPT

R3766

1

1

1/10W

EU_OPT

Q3704

2SC3052

OPT

E

B

C

R3750

1K

OPT

C3725

0.1uF

16V

16V

+3.3V_TU

L3702

BLM18PG121SN1D

C3729

0.1uF

16V

R3754

10K

10K

OPT

R3737

2.2K

2.2K

CHINA_OPT

R3702

0

CHINA_OPT

FE_TS_VAL_ERR

R3744

4.7K

CHINA_OPT

C3710

0.1uF

16V

FE_TS_DATA[0-7]

Q3701

ISA1530AC1

CHINA_OPT

E

B

C

C3707

100pF

50V

100pF

50V

+1.2V/+1.8V_TU

+5V_TU

IF_P_MSTAR

R3764

0

1/10W

CHINA_OPT

+3.3V_TU

C3703

100pF

50V

100pF

50V

R3723

0

CHINA_OPT

R3707

0

OPT

+3.3V_TU

TU_SDA

+1.2V/+1.8V_TU

C3716

22pF

50V

22pF

50V

OPT

C3727

0.1uF

16V

DEMOD_SDA

+3.3V_Normal

C3717

0.1uF

16V

+3.3V_TU

C3728

0.1uF

16V

16V

OPT

C3714

22pF

50V

CHINA_OPT

22pF

50V

CHINA_OPT

C3724

0.1uF

16V

16V

R3742

4.7K

CHINA_OPT

DEMOD_RESET

C3715

22pF

50V

22pF

50V

OPT

+5V_TU

+1.2V/+1.8V_TU

+3.3V_TU

R3749

0

CONTROL_ATTEN

R3728

0

CHINA_OPT

IF_N_MSTAR

R3727

0

CHINA_OPT

C3701

0.1uF

16V

0.1uF

16V

Q3702

2SC3052

CHINA_OPT

E

B

C

L3701

BLM18PG121SN1D

CHINA_OPT

C3712

22pF

50V

22pF

50V

CHINA_OPT

TU_SCL

R3753

4.7K

4.7K

DEMOD_SCL

R3725

0

CHINA_OPT

R3726

0

CHINA_OPT

R3705

0

CHINA_OPT

+5V_TU

+5V_TU

R3732

100

100

C3709

0.01uF

25V

0.01uF

25V

CHINA_OPT

R3760

0

EU_OPT

R3761

0

EU_OPT

C3730

10uF

10V

10uF

10V

C3719

22uF

10V

OPT

22uF

10V

OPT

C3722

22uF

10V

22uF

10V

C3723

22uF

10V

22uF

10V

C3737

100pF

50V

100pF

50V

C3738

0.1uF

16V

0.1uF

16V

R3704

0

EU_OPT

IC3703

AZ1117H-ADJTRE1(EH11A)

EU_OPT

2

OUTPUT

3

INPUT

1

ADJ/GND

R3768

1.2K

1.2K

EU_OPT

R3767

10

EU_OPT

R3740

1.2K

1.2K

R3741

1.2K

1.2K

R3735

33

R3736

33

C3711

18pF

50V

18pF

50V

C3713

18pF

50V

18pF

50V

R3752

220

R3751

220

R3755

470

TU3702

TDTJ-S001D

TDTJ-S001D

EU_TUNER

14

3.3V

13

1.2V

5

AS

12

GND

11

VIDEO

2

BST_CNTL

10

NC

4

NC[RF_AGC]

1

ANT_PWR[OPT]

17

DIF_1

9

SIF

8

NC[IF_TP]

3

+B

16

IF_AGC_CNTL

7

SDA

6

SCL

15

RESET

18

DIF_2

19

SHIELD

C3705

100uF

16V

16V

CHINA_OPT

R3703

150

OPT

OPT

TU3701

TDFR-C035D

TDFR-C035D

1

RF_S/W_CNTL

2

BST_CNTL

3

+B1[+5V]

4

NC[RF_AGC]

5

NC_1

6

SCLT

7

SDAT

8

NC_2

9

SIF

10

NC_3

11

VIDEO

12

GND

13

+B2[1.2V]

14

+B3[3.3V]

15

RESET

16

NC_4

17

SCL

18

SDA

19

ERR

20

SYNC

21

VALID

22

MCL

23

D0

24

D1

25

D2

26

D3

27

D4

28

D5

29

D6

30

D7

31

SHIELD

TU3701-*1

TDFR-C155D

TDFR-C155D

1

RF_S/W_CNTL

2

BST_CNTL

3

+B1[+5V]

4

NC[RF_AGC]

5

NC_1

6

SCLT

7

SDAT

8

NC_2

9

SIF

10

NC_3

11

VIDEO

12

GND

13

+B2[1.2V]

14

+B3[3.3V]

15

RESET

16

NC_4

17

SCL

18

SDA

19

ERR

20

SYNC

21

VALID

22

MCL

23

D0

24

D1

25

D2

26

D3

27

D4

28

D5

29

D6

30

D7

31

SHIELD

VER 1.0

EU/CHINA CAN TUNER

should be guarded by ground

The pull-up/down of LNA2_CTL

is depended on MODLE_OPT_1.

GPIO must be added for FE_BOOSTER_CTL

is depended on MODLE_OPT_1.

GPIO must be added for FE_BOOSTER_CTL

FE_BOOSTER_CTL

60mA

FE_AGC_SPEED_CTL

R2

LGIT CAN NIM_H/N TUNER for EU & CHINA

380mA

Vo=0.8*(1+R1/R2)

R1

close to TUNER

close to TUNER

close to TUNER

Close to the tuner

200mA

This was being applied to the only china demod,

so this has to be deleted in both main and ISDB sheet.

so this has to be deleted in both main and ISDB sheet.

Pull-up can’t be applied

because of MODEL_OPT_2

because of MODEL_OPT_2

GPIO must be added.

Close to the CI Slot

1. should be guarded by ground

2. No via on both of them

3. Signal Width >= 12mils

Signal to Signal Width = 12mils

Ground Width >= 24mils

2. No via on both of them

3. Signal Width >= 12mils

Signal to Signal Width = 12mils

Ground Width >= 24mils

OPTION : RF AGC

close to IF line

GP2_Saturn7M

27

R1

R2

BOOSTER : CHINA OPT

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

GMA18

H_CONV

RXA3-

RXA3-

GMA16

GMA18

I2C_SCL

GMA7

RXA1+

GMA4

L702

120-ohm

WAFER_FHD

RXD1-

RXACK+

RXB3-

RXB4-

L701

120-ohm

WAFER_HD

PANEL_VCC

RXA0+

RXB0+

RXC4+

RXC0-

GMA9

RXC0-

RXC2+

RXC3+

RXB2+

RXDCK-

I2C_SDA

GMA4

RXD0-

R710

10K

LVDS_SEL_LOW

RXD3-

P703

TF05-51S

WAFER_FHD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

RXC3-

RXC0+

RXA0-

RXC4-

H_CONV

OPC_EN

R706

33

240Hz

C711

10uF

16V

10uF

16V

MINI_LVDS

RXA2-

VCOML

GSP/GVST_I

POL

RXA2-

RXA2+

RXCCK+

GMA3

RXD0+

RXD2+

GMA12

OPC_EN

RXA1-

PWM_DIM

RXCCK-

GMA9

R709

10K

10K

BIT_SEL_LOW

RXA1+

RXB4+

RXB1-

C706

0.1uF

16V

0.1uF

16V

MINI_LVDS

OPC_OUT

RXB4-

R708

33

240Hz/3D

RXA3+

RXDCK+

C704

0.1uF

50V

0.1uF

50V

MINI_LVDS

RXC1+

RXACK+

P705

FF10001-30

WAFER_HD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

RXB2+

RXB3+

VCOMLFB

RXD2-

R705

3.3K

LVDS_SEL_HIGH

RXC2-

RXA4-

RXD1+

C712

10uF

16V

10uF

16V

MINI_LVDS

RXC0+

GMA3

R707

33

240Hz/3D

C710

0.1uF

16V

0.1uF

16V

WAFER_FHD

RXC1-

PWM_DIM

RXA3+

RXB0-

RXD0+

GMA10

RXA0+

+3.3V_Normal

RXC1+

RXC4-

FRC_RESET

R700

3.3K

MINI_LVDS

RXA1-

RXB3+

VCOMRFB

RXD4-

SOE

RXC2+

RXA0+

VDD_LCM

GMA6

RXBCK+

RXA2+

RXA0-

VCC_LCM

GMA13

VCC_LCM

RXC3+

GMA1

RXA1+

R717

0

OPT

RXA4+

RXB4+

RXC3-

SOE

R712

3.3K

LVDS_SEL_HIGH

RXD0-

C709

1000pF

50V

1000pF

50V

WAFER_FHD

GMA6

RXD1-

GSP/GVST_I

SCAN_BLK2

VDD_LCM

+3.3V_Normal

RXA0-

RXB2-

RXB1+

RXD4+

R716

0

WAFER_HD

RXBCK-

PANEL_VCC

GMA16

RXC4+

RXB1+

RXB0-

RXD1+

RXACK-

C708

0.01uF

50V

0.01uF

50V

MINI_LVDS

RXB1-

RXACK-

GMA7

GMA10

HVDD

C703

0.01uF

50V

0.01uF

50V

MINI_LVDS

HVDD

C707

0.1uF

50V

0.1uF

50V

MINI_LVDS

GMA15

GMA15

P704

TF05-41S

WAFER_FHD_120HZ

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

R711

10K

LVDS_SEL_LOW

C700

10uF

16V

10uF

16V

OPT

RXB2-

RXC2-

VCOMR

POL

RXB3-

RXC1-

C701

0.1uF

16V

0.1uF

16V

MINI_LVDS

GMA1

GMA13

RXB0+

RXA1-

RXD3+

GMA12

R703

3.3K

MINI_LVDS

R721

0

OPT

R728

0

SCAN

R720

0

SCAN

R723

0

OPT

R713

0

NON_SCAN

SCAN_BLK1/OPC_OUT

R714

0

OPT

R724

0

OPT

VDD_EVEN

CLK1

VGL

(-5V)

Z_OUT

CLK4

VGI_N

VGI_P

VST

CLK2

VGL_I

CLK5

CLK6

R745

0

NON_GIP

CLK3

VDD_ODD

VGI_N

R767

0

NON_GIP

VGH_M

(+25V)

CLK1

R752

0

NON_GIP

R753

0

NON_GIP

R771

0

NON_GIP

CLK5

VDD_ODD

R751

0

NON_GIP

CLK4

Z_OUT

R750

0

NON_GIP

R748

0

NON_GIP

VST

GOE/GCLK1_I

CLK6

VGL_I

CLK3

R770

0

NON_GIP

R749

0

NON_GIP

R754

0 MINI_LVDS

VGL

(-5V)

VGI_P

VDD_EVEN

GSC/GCLK3_I

R772

0

NON_GIP

R768

0

NON_GIP

R769

0

NON_GIP

CLK2

R765

0 GIP

R729

0 GIP

R773

3.3K

NON_GIP

R701

0 GIP

P701

104060-6017

MINI_LVDS

1

GND

2

GMA1

3

GMA3

4

GMA4

5

GMA6

6

GMA7

7

GMA9

8

GMA10

9

GMA12

10

GMA13

11

GMA15

12

GMA16

13

GMA18

14

GND

15

OPT_N

16

H_CONV

17

VST_IN

18

POL

19

SOE

20

GND

21

LV0+

22

LV0-

23

LV1+

24

LV1-

25

LV2+

26

LV2-

27

LVCLK+

28

LVCLK-

29

LV3+

30

LV3-

31

LV4+

32

LV4-

33

LV5+

34

LV5-

35

GND

36

VCC

37

VCC

38

GND

39

HALF_VDD

40

HALF_VDD

41

VDD

42

VDD

43

GND

44

VCOM_IN

45

VCOM_FB

46

GND

47

VST

48

VSS

49

VGH_EVEN

50

VGH_ODD

51

VGI_P

52

VGI_N

53

CLK6

54

CLK5

55

CLK4

56

CLK3

57

CLK2

58

CLK1

59

Z_OUT

60

GND

61

.

P702

104060-6017

MINI_LVDS

1

GND

2

Z_OUT

3

CLK1

4

CLK2

5

CLK3

6

CLK4

7

CLK5

8

CLK6

9

VGI_N

10

VGI_P

11

VGH_ODD

12

VGH_EVEN

13

VSS

14

VST

15

GND

16

VCOM_FB

17

VCOM_IN

18

GND

19

VDD

20

VDD

21

HALF_VDD

22

HALF_VDD

23

GND

24

VCC

25

VCC

26

GND

27

RV0+

28

RV0-

29

RV1+

30

RV1-

31

RV2+

32

RV2-

33

RVCLK+

34

RVCLK-

35

RV3+

36

RV3-

37

RV4+

38

RV4-

39

RV5+

40

RV5-

41

GND

42

SOE

43

POL

44

VST_IN

45

H_CONV

46

OPT_N

47

GND

48

GMA18

49

GMA16

50

GMA15

51

GMA13

52

GMA12

53

GMA10

54

GMA9

55

GMA7

56

GMA6

57

GMA4

58

GMA3

59

GMA1

60

GND

61

.

3D_POWER_EN

C714

1000pF

50V

1000pF

50V

3D

C715

0.1uF

16V

0.1uF

16V

3D

C713

10uF

16V

10uF

16V

OPT

L703

120-ohm

3D

PANEL_VCC

VCC_LCM

VCC_LCM

VCC_LCM

R704

33

3D

/3D_FPGA_RESET

R702

33

3D

C702

10uF

MINI_LVDS

C705

10uF

MINI_LVDS

GP2_Saturn7M

LVDS

[51Pin LVDS Connector]

(For FHD 60/120Hz)

(For FHD 60/120Hz)

[41Pin LVDS Connector]

(For FHD 120Hz)

(For FHD 120Hz)

[30Pin LVDS Connector]

(For HD 60Hz_Normal)

(For HD 60Hz_Normal)

[LEFT FFC Connector]

(60Pin Mini-LVDS)

(60Pin Mini-LVDS)

10uF/25V(3216)

10uF/25V(3216)

[Right FFC Connector]

(60Pin Mini-LVDS)

(60Pin Mini-LVDS)

36

Ver. 1.3

BIT_SEL

LVDS_SEL

LVDS_SEL

Click on the first or last page to see other 32LE3300 / 32LE3308 / 32LE330N (CHASSIS:LD01D) service manuals if exist.