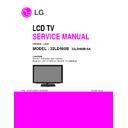

LG 32LD460B (CHASSIS:LJ01Z) Service Manual ▷ View online

- 16 -

300

200

530

810

400

510

120

500

A7

A2

A5

A10

A21

900

910

800

LV1

540

521

550

EXPLODED VIEW

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

0.1uF

C4058

FRC_LPLL

0 . 0 4 7 u F

C219

0 . 0 4 7 u F

C227

FRCVDDC

VDD33

BLM18PG121SN1D

L212

+1.5V_DDR

DDC_SDA_1

SIDEAV_L_IN

0.1uF

C4019

0.1uF

C4056

0.1uF

C4027

VDD33

0.1uF

C291

FRC

0.1uF

C4032

10uF

C263

LNA2_CTL

DDC_SCL_2

D2-_HDMI1

33

R257

SCART1_Lout

100

R203

DSUB_B-

0 . 0 4 7 u F

C218

COMP2_R_IN

0.1uF

C4011

2 . 2 u F

C236

AVDD_DDR0

SC1_R-/COMP1_Pr-

VDD33_DVI

BLM18PG121SN1D

L227

33

R230

TU_SDA

IF_AGC_SEL

D1-_HDMI1

33

R4016

DEMOD_SDA

EPHY_MDIO

SC1_B-/COMP1_Pb-

33

R239

33

R282ETHERNET

33

R255

+3.3V_Normal

SC1/COMP1_L_IN

COMP2_Y-

IF_P_MSTAR

100

R289

0.1uF

C4038

TU_CVBS

AVDD_DDR0

+3.3V_Normal

COMP2_Pb-

68

R252

COMP2_L_IN

1000pF

OPT

C264

MODEL_OPT_0

68

R231

+1.26V_VDDC

MVREF

AVDD_DDR_FRC

BLM18PG121SN1D

L219

AMP_SDA

33

R285ETHERNET

0 . 0 4 7 u F

C222

MODEL_OPT_1

33

R237

1/16W

1K

1%

R4014

AUD_SCK

BLM18SG700TN1D

L226

HPD1

24MHz

X201

0.1uF

C283

0.1uF

C4009

0.1uF

C4002

33

R232

0 . 0 4 7 u F

C204

PC_R_IN

0 . 0 4 7 u F

C225

SC1_B+/COMP1_Pb+

0 . 0 4 7 u F

C215

0 . 0 4 7 u F

C233

AU25

+1.5V_FRC_DDR

VDD_RSDS

COMP2_Y+

33

R228

AVDD2P5

AVDD25_PGA

AVDD_DDR0

68

R256

33

R253

DDC_SCL_1

DSUB_B+

BT_LOUT

33

R244

22

R4024

HP_LOUT

ADC2P5

BT_DP

BLM18SG700TN1D

L225

AVDD_DMPLL

D0-_HDMI2

MODEL_OPT_5

2 . 2 u F

C4059

SIDE_USB_DM

22

R4018

FRC

DEMOD_SCL

10K

R4023

2 . 2 u F

C244

BLM18PG121SN1D

L213

OPT

0.1uF

C4012

0 . 0 4 7 u F

C205

AVDD_DDR0

2 . 2 u F

C238

EPHY_RXD1

SOC_RESET

+3.3V_Normal

AVDD_DMPLL

0.1uF

C295

0.1uF

C4017

MVREF

0.1uF

C4062

0 . 0 4 7 u F

C211

0.1uF

C285

0

NON_EU

R236

D1+_HDMI1

COMP2_Pr-

CEC_REMOTE_S7

EPHY_TXD0

0.1uF

C4023

EPHY_TXD1

AV_L_IN

+3.3V_Normal

1000pF

OPT

C203

SC1_CVBS_IN

68

R238

BLM18PG121SN1D

L207

1/10W

0

5%

R4027

100

R201

DSUB_VSYNC

AVDD_DMPLL

0 . 0 4 7 u F

C207

AVDD25_PGA

FRC_RESET

33

R278ETHERNET

0 . 0 4 7 u F

C230

DSUB_HSYNC

AVDD_DDR1

D0-_HDMI1

FRC_VDD33_DDR

2 . 2 u F

C245

DSUB_G-

0.1uF

C286

2 . 2 u F

C237

1000pF

C210

COMP2_Pr+

0 . 1 u F

C4015

0 . 1 u F

C258

VDD33

AVDD2P5

33

R249

BLM18PG121SN1D

L209

10K

R4020

0.1uF

C292

0.1uF

C294

0 . 0 4 7 u F

C226

EPHY_REFCLK

AVDD2P5

2 . 2 u F

C243

1uF

C253

CK+_HDMI1

SC1_G-/COMP1_Y-

100

R288

1K

R4019

0 . 0 4 7 u F

C221

VDD33

RF_SWITCH_CTL

0.1uF

C4007

PC_L_IN

0 . 0 4 7 u F

C208

TP204

100

R204

AU33

+2.5V_Normal

CK-_HDMI1

+2.5V_Normal

+2.5V_Normal

D2+_HDMI1

D0+_HDMI2

0 . 0 4 7 u F

C213

0.1uF

C4003

68

R254

0 . 0 4 7 u F

C229

AVDD_DDR_FRC

+2.5V_Normal

MODEL_OPT_3

SC1_FB

0 . 0 4 7 u F

C212

COMP2_Pb+

SIDEAV_CVBS_IN

2 . 2 u F

C247

OPT

AMP_SCL

0.1uF

C4006

1000pF

C217

AU33

BLM18PG121SN1D

L222

47

R4002

0.1uF

C280

33

R245

CK-_HDMI2

SPDIF_OUT

EPHY_RXD0

10K

R4006

0.1uF

C4013

10K

R4026

SC1_ID

BT_ON/OFF

BLM18PG121SN1D

FRC

L214

+1.26V_VDDC

100

R202

SC1_SOG_IN

BLM18PG121SN1D

L217

FRC_AVDD

D2-_HDMI2

68

R258

33

R283ETHERNET

BLM18PG121SN1D

L210

FRC

0 . 0 4 7 u F

C206

0 . 0 4 7 u F

C232

DTV/MNT_VOUT

0.1uF

C290

0.1uF

C4026

COMP2_DET

TU_SIF

0 . 0 4 7 u F

C231

CK+_HDMI2

0 . 0 4 7 u F

C4057

TU_SCL

TP206

0.1uF

C4036

68

R233

AUD_LRCH

BLM18PG121SN1D

L221

FRC

VDD33

MIU1VDDC

0.1uF

C4004

FRC

D2+_HDMI2

+1.26V_VDDC

ADC2P5

AUD_LRCK

0.1uF

C4008

0.1uF

C298

FRC

0

R243

1/16W

1K

1%

R4015

EPHY_CRS_DV

AV_R_IN

BT_DM

D1+_HDMI2

0 . 0 4 7 u F

C216

0.1uF

C4041

0.1uF

C297

DSUB_R-

1M

R287

SC1_G+/COMP1_Y+

DSUB_G+

100

R296

D0+_HDMI1

0 . 1 u F

C256

68

R242

0 . 0 4 7 u F

C214

33

R284ETHERNET

EPHY_EN

0.1uF

C4024

2 . 2 u F

OPT

C235

1/10W

0

5%

R4022

BLM18PG121SN1D

L215

HPD2

0.1uF

C4028

2 . 2 u F

OPT

C234

IR

0 . 0 2 2 u F

16V

16V

C4065

IF_AGC_MAIN

0 . 1 u F

C257

AUD_MASTER_CLK

0.1uF

C296

2 . 2 u F

C239

FRC_AVDD

33

R246

TP205

VDD33_DVI

33

R241

47

R4003

SCART1_Rout

100

R298

OPT

FRC_VDD33_DDR

0 . 1 u F

C4064

IF_N_MSTAR

0.1uF

C4014

33

R248

DSUB_R+

HP_ROUT

AVDD_DDR1

33

R251

0

R234

2 . 2 u F

C242

+2.5V_Normal

1000pF

C224

0 . 0 4 7 u F

C209

0 . 1 u F

C251

AVDD2P5

SIDEAV_R_IN

0.1uF

C4016

33

R280

ETHERNET

2 . 2 u F

C246

OPT

0 . 0 4 7 u F

C223

SIDE_USB_DP

MODEL_OPT_2

2 . 2 u F

C4060

SC1_R+/COMP1_Pr+

TP201

33

R250

22

R4025

BLM18PG121SN1D

L211

68

R240

FRC_LPLL

AV_CVBS_IN

DDC_SDA_2

0 . 1 u F

C250

0 . 0 4 7 u F

C220

68

R229

+1.26V_VDDC

TP202

AU25

VDD_RSDS

10K

R4017

OPT

0.1uF

C277

BLM18PG121SN1D

L206

0.1uF

C299

BLM18PG121SN1D

L204

FRCVDDC

EPHY_MDC

0.1uF

C4040

TP203

D1-_HDMI2

0 . 1 u F

C288

VDD33

SC1/COMP1_R_IN

0.1uF

C4010

FRC

BLM18SG121TN1D

L202

BLM18SG121TN1D

L223

0 . 1 u F

C4005

TP207

TP208

TP209

TP210

D1+_HDMI3

D0-_HDMI3

HPD3

CK+_HDMI3

CK-_HDMI3

D1-_HDMI3

DDC_SCL_3

D2+_HDMI3

D0+_HDMI3

DDC_SDA_3

D2-_HDMI3

D1-_HDMI4

D2+_HDMI4

HPD4

DDC_SCL_4

D0+_HDMI4

D0-_HDMI4

DDC_SDA_4

D2-_HDMI4

CK+_HDMI4

D1+_HDMI4

CK-_HDMI4

10uF

C275

10uF

C276

10uF

C279

FRC

10uF

C278

10uF

C282

FRC

10uF

C281

10uF

C284

10uF

C287

10uF

C289

10uF

C293

10uF

C4001

10uF

C4018

10uF

C4022

10uF

C4061

10uF

C4063

4 . 7 u F

C249

1uF

C4045

0.1uF

C4020

0.1uF

C4025

0.1uF

C4031

MIU1VDDC

VDD33

NEC_SCL

NEC_SDA

0 OPT

R4029

0 OPT

R4028

AMP_SCL

AMP_SDA

CHB_CVBS_IN

0

R4032

0

R4033

22

R292

DEMOD_OPT

22

R291

DEMOD_OPT

AV_CVBS_IN2

AV_CVBS_IN2

TP211

1K

NO_FRC

R227

1K

LVDS

R212

1K

FRC

R226

1K

DDR_256MB

R209

1K

MINI_LVDS

R211

1K

HD

R207

1K

FHD

R206

1K

DDR_512MB

R208

MODEL_OPT_4

10uF

C4066

BLM18SG700TN1D

L228

MODEL_OPT_5

MODEL_OPT_4

1K

100/120Hz LVDS

R294

1K

50/60Hz LVDS

R297

1K

GIP

R295

1K

NON_GIP

R293

MIU0VDDC

MIU0VDDC

+1.26V_VDDC

10uF

C228

0.1uF

FRC

C240

0.1uF

C241

0.1uF

C4042

0.1uF

C4046

0.1uF

C4043

0.1uF

C4044

27pF

C261

27pF

C262

+3.3V_Normal

10K

R205

FRC

3D_POWER_EN

100

3D

R210

/3D_FPGA_RESET

100

3D

R213

4.7uF

C268

4.7uF

C272

5.6uH

L205

CM2012F5R6KT

5.6uH

L203

CM2012F5R6KT

MODEL_OPT_6

1K

LCD

R215

1K

OLED

R214

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX & MS10

A_RXCP

F1

A_RXCN

F2

A_RX0P

G2

A_RX0N

G3

A_RX1P

H3

A_RX1N

G1

A_RX2P

H1

A_RX2N

H2

DDCDA_DA/GPIO24

F5

DDCDA_CK/GPIO23

F4

HOTPLUGA/GPIO19

E6

B_RXCP

D3

B_RXCN

C1

B_RX0P

D1

B_RX0N

D2

B_RX1P

E2

B_RX1N

E3

B_RX2P

F3

B_RX2N

E1

DDCDB_DA/GPIO26

D4

DDCDB_CK/GPIO25

E4

HOTPLUGB/GPIO20

D5

C_RXCP

AA2

C_RXCN

AA1

C_RX0P

AB1

C_RX0N

AA3

C_RX1P

AB3

C_RX1N

AB2

C_RX2P

AC2

C_RX2N

AC1

DDCDC_DA/GPIO28

AB4

DDCDC_CK/GPIO27

AA4

HOTPLUGC/GPIO21

AC3

D_RXCP

A2

D_RXCN

A3

D_RX0P

B3

D_RX0N

A1

D_RX1P

B1

D_RX1N

B2

D_RX2P

C2

D_RX2N

C3

DDCDD_DA/GPIO30

B4

DDCDD_CK/GPIO29

C4

HOTPLUGD/GPIO22

E5

CEC/GPIO5

D6

HSYNC0

G5

VSYNC0

G6

RIN0P

K1

RIN0M

L3

GIN0P

K3

GIN0M

K2

BIN0P

J 3

BIN0M

J 2

SOGIN0

J 1

HSYNC1

G4

VSYNC1

H6

RIN1P

K5

RIN1M

K4

GIN1P

J 4

GIN1M

K6

BIN1P

H4

BIN1M

J 6

SOGIN1

J 5

HSYNC2

H5

RIN2P

N3

RIN2M

N2

GIN2P

M2

GIN2M

M1

BIN2P

L2

BIN2M

L1

SOGIN2

M3

CVBS0P

N4

CVBS1P

N6

CVBS2P

L4

CVBS3P

L5

CVBS4P

L6

CVBS5P

M4

CVBS6P

M5

CVBS7P

K7

CVBS_OUT1

M6

CVBS_OUT2

M7

VCOM0

N5

VIFP

W2

VIFM

W1

I P

V2

IM

V1

S S I F / S I F P

Y2

SSIF/SIFM

Y1

QP

U3

QM

V3

IFAGC

Y5

RF_TAGC

Y4

TGPIO0/UPGAIN

U1

TGPIO1/DNGAIN

U2

TGPIO2/I2C_CLK

R3

TGPIO3/I2C_SDA

T3

XTALIN

T2

XTALOUT

T1

SPDIF_IN/GPIO177

G14

SPDIF_OUT/GPIO178

G13

DM_P0

B7

DP_P0

A7

DM_P1

AF17

DP_P1

AE17

I2S_IN_BCK/GPIO175

F14

I2S_IN_SD/GPIO176

F13

I2S_IN_WS/GPIO174

F15

I2S_OUT_BCK/GPIO181

D20

I2S_OUT_MCK/GPIO179

E20

I2S_OUT_SD/GPIO182

D19

I2S_OUT_SD1/GPIO183

F18

I2S_OUT_SD2/GPIO184

E18

I2S_OUT_SD3/GPIO185

D18

I2S_OUT_WS/GPIO180

E19

LINE_IN_0L

N1

LINE_IN_0R

P3

LINE_IN_1L

P1

LINE_IN_1R

P2

LINE_IN_2L

P4

LINE_IN_2R

P5

LINE_IN_3L

R6

LINE_IN_3R

T6

LINE_IN_4L

U5

LINE_IN_4R

V5

LINE_IN_5L

U6

LINE_IN_5R

V6

LINE_OUT_0L

U4

LINE_OUT_2L

W3

LINE_OUT_3L

W4

LINE_OUT_0R

V4

LINE_OUT_2R

Y3

LINE_OUT_3R

W5

MIC_DET_IN

R4

MICCM

T5

MICIN

R5

AUCOM

T4

VRM

P7

VAG

R7

VRP

P6

HP_OUT_1L

R1

HP_OUT_1R

R2

ET_RXD0

E21

ET_TXD0

E22

ET_RXD1

D21

ET_TXD1

F21

ET_REFCLK

E23

ET_TX_EN

D22

ET_MDC

F22

ET_MDIO

D23

ET_CRS

F23

AVLINK

F8

IRINT

G8

TESTPIN

K8

RESET

A4

U3_RESET

Y17

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX & MS10

VDDC_1

H11

VDDC_2

H12

VDDC_3

H13

VDDC_4

H14

VDDC_5

H15

VDDC_6

J 1 2

VDDC_7

J 1 3

VDDC_8

J 1 4

VDDC_9

J 1 5

VDDC_10

J 1 6

VDDC_11

L18

A_DVDD

H16

B_DVDD

K19

FRC_VDDC_0

L19

FRC_VDDC_1

M18

FRC_VDDC_2

M19

FRC_VDDC_3

N18

FRC_VDDC_4

N19

FRC_VDDC_5

N20

FRC_VDDC_6

P18

FRC_VDDC_7

P19

FRC_VDDC_8

P20

U3_DVDD_DDR

Y12

AVDD1P2

J 1 1

DVDD_NODIE

L7

AVDD2P5_ADC_1

H7

AVDD2P5_ADC_2

J 7

AVDD25_REF

J 8

AVDD_AU25

L8

PVDD_1

W15

PVDD_2

Y15

AVDD25_PGA

U8

AVDD_NODIE

M8

AVDD_DVI_1

N9

AVDD_DVI_2

P9

AVDD3P3_CVBS

N8

AVDD_DMPLL

P8

AVDD_AU33

T7

AVDD_EAR33

U7

AVDD33_T

T9

VDDP_1

R8

VDDP_2

R9

VDDP_3

T8

FRC_VD33_2_1

V20

FRC_VD33_2_2

W20

FRC_AVDD_RSDS_1

U19

FRC_AVDD_RSDS_2

U20

FRC_AVDD_RSDS_3

V19

FRC_AVDD

W19

FRC_AVDD_LPLL

U18

FRC_AVDD_MPLL

T20

FRC_VDD33_DDR

Y14

AVDD_MEMPLL

R19

FRC_AVDD_MEMPLL

W14

AVDD_DDR0_D_1

D15

AVDD_DDR0_D_2

D16

AVDD_DDR0_D_3

E15

AVDD_DDR0_D_4

E16

AVDD_DDR0_C

E17

AVDD_DDR1_D_1

F16

AVDD_DDR1_D_2

F17

AVDD_DDR1_D_3

G16

AVDD_DDR1_D_4

G17

AVDD_DDR1_C

H17

FRC_AVDD_DDR_D_1

AB11

FRC_AVDD_DDR_D_2

AB12

FRC_AVDD_DDR_D_3

AC11

FRC_AVDD_DDR_D_4

AC12

FRC_AVDD_DDR_C

AA12

MVREF

G15

NC_1

Y7

NC_2

Y8

GND_1

G18

GND_2

H9

GND_3

H10

GND_4

H18

GND_5

H19

GND_6

J 1 0

GND_7

J 1 7

GND_8

J 1 8

GND_9

J 1 9

GND_10

K9

GND_11

K10

GND_12

K11

GND_13

K12

GND_14

K13

GND_15

K14

GND_16

K15

GND_17

K16

GND_18

K17

GND_19

K18

GND_20

L9

GND_21

L10

GND_22

L11

GND_23

L12

GND_24

L13

GND_25

L14

GND_26

L15

GND_27

L16

GND_28

L17

GND_29

M9

GND_30

M10

GND_31

M11

GND_32

M12

GND_33

M13

GND_34

M14

GND_35

M15

GND_36

M16

GND_37

M17

GND_38

N10

GND_39

N11

GND_40

N12

GND_41

N13

GND_42

N14

GND_43

N15

GND_44

N16

GND_45

N17

GND_46

P10

GND_47

P11

GND_48

P12

GND_49

P13

GND_50

P14

GND_51

P15

GND_52

P16

GND_53

P17

GND_54

R10

GND_55

R11

GND_56

R12

GND_57

R13

GND_58

R14

GND_59

R15

GND_60

R16

GND_61

R17

GND_62

R18

GND_63

T10

GND_64

T11

GND_65

T12

GND_66

T13

GND_67

T14

GND_68

T15

GND_69

T16

GND_70

T17

GND_71

T18

GND_72

T19

GND_73

U10

GND_74

U11

GND_75

U12

GND_76

U13

GND_77

U14

GND_78

U15

GND_79

U16

GND_80

U17

GND_81

V7

GND_82

V8

GND_83

V9

GND_84

V10

GND_85

V11

GND_86

V12

GND_87

V13

GND_88

V14

GND_89

V15

GND_90

V16

GND_91

V17

GND_92

V18

GND_93

W7

GND_94

W8

GND_95

W9

GND_96

W10

GND_97

W11

GND_98

W12

GND_99

W13

GND_100

W16

GND_101

W17

GND_102

W18

GND_103

Y13

GND_104

Y18

GND_105

AA13

GND_106

AB13

GND_107

AC13

GND_FU

J 9

PGA_VCOM

U9

GND_108

D17

GND_109

H23

GND_110

AF13

GP2_Saturn7M

MAIN_2

ANALOG SIF

RMII For Ethernet

RSDS Power OPT

FRC

I2S_I/F

PIN NAME

DSUB

N o r m a l 2 . 5 V

Close to MSTAR

MODEL OPTION

FRC_LPLL:13mA

N o r m a l P o w e r 3 . 3 V

DTV_IF

AVDD_DMPLL/AVDD_NODIE:7.362mA

FRC_MPLL:4mA

AU25:10mA

Close to MSTAR

AVDD_MEMPLL:24mA

F7

VDD33_DVI:163mA

FHD

SCART1_RGB/COMP1

G19

AVDD2P5/ADC2P5:162mA

MODEL_OPT_3

AVDD25_PGA:13mA

C5

VDDC : 2026mA

AVDD_DDR0:55mA

H/P OUT

VDDC 1.26V

PIN NO.

NO FRC

MODEL_OPT_0

CVBS In/OUT

AUDIO OUT

TU/DEMOD_I2C

FRC_AVDD:60mA

HD

AUDIO IN

VDD_RSDS:88mA

MODEL_OPT_1

FRC_VDD33_DDR:50mA

COMP2

DDR_512MB

Close to MSTAR

SIDE USB

DDR3 1.5V

VDD33_T/VDDP/U3_VD33_2:47mA

B6

MODEL OPTION

HDMI

AVDD_DDR_FRC:55mA

LOW

AU33:31mA

DDR_256MB

HIGH

MODEL_OPT_2

B/T USB

Close to MSTAR

RSDS Power OPT

AVDD_DDR1:55mA

V e r . 1 . 4

2

MINI LVDS

LVDS

MODEL_OPT_4

MODEL_OPT_5

100/120Hz LVDS

E18

GIP

NON_GIP

D18

50/60Hz LVDS

MODEL_OPT_6

F9

LCD

OLED

N O _ F R C : L O W L O W

U 3 _ I N T E R N A L : H I G H L O W

U 3 _ E X T E R N A L : H I G H H I G H

PWIZ TCON with LG FRC : HIGH HIGH

OPT_0 OPT_4

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

RXD3-

RXA4+

C-MODT

RXB4+

C-TMA12

C-TMBA2

RXC4+

C-TMODT

C-TMDQU7

0.1uF

C319

C-MA6

C-MDQU5

C-TMCK

C-MA9

C-MA3

C-MDQSU

820

R317

0.1uF

C322

0.1uF

C313

C-MDQU1

C-TMA4

C-MA12

C-TMA3

C-MDQSUB

C-TMA6

FRC_CONF1

10uF

10V

10V

C324

C-TMDQU4

C-TMA1

VCC1.5V_U3_DDR

RXA0-

TP301

0.1uF

C323

C-TMDQL4

RXACK+

C-MA1

C-MA12

RXA0+

C-MCK

UART_FRC_RX

C-TMBA2

RXCCK-

1K

R323

0.1uF

C310

C-MDQL1

UART_FRC_TX

0.1uF

C306

C-TMDQL7

0.1uF

C317

C-MDQU4

C-TMCKB

C-MDMU

C-MCKE

0.1uF

C320

RXB0+

C-MA8

C-TMA6

RXB1+

150

OPT

R306

C-TMA4

0.1uF

C302

C-MDQL1

C-TMCKE

C-MDQSL

C-MA10

RXC3+

FRC_PWM0

C-TMODT

C-TMDML

C-MDQSLB

C-TMDQSLB

C-MA11

C-TMDMU

240

1%

R303

C-TMCASB

FRC_CONF0

RXD2-

C-TMA12

C-TMA7

C-TMCKB

C-MA6

VCC1.5V_U3_DDR

C-TMDQSLB

C-TMA1

0.1uF

C318

RXD1+

RXBCK-

GVDD_EVEN

0

R300

OPT

C-TMBA1

FRC_PWM1

C-TMDQU3

C-TMDQL4

RXCCK+

TP302

0.1uF

C316

RXC1-

C-TMA0

C-MDQL7

RXB2-

C-TMDQU3

C-MRASB

+3.3V_Normal

C-MDMU

C-MBA0

C-MDQU7

C-TMWEB

C-MDQU2

GCLK2

C-MCKB

C-TMA11

1K

1

%

R305

1K

1

%

R301

C-TMA2

C-TMDQU7

C-TMDQL2

GCLK4

I2C_SDA

C-MDQU2

RXA3-

C-TMDQU6

C-TMA5

C-MA10

0 . 1 u F

16V

16V

C325

RXC3-

RXA1+

RXB1-

C-TMCKE

C-MDQSU

C-MA7

C-TMRESETB

C-MBA0

C-MVREFDQ

C-MCKB

RXB4-

C-MDQL0

C-TMDQU2

C-TMDQL3

1K

OPT

R322

C-TMBA1

C-TMDQSUB

1K

R318

C-MDQU3

C-MA3

C-MA0

C-TMDQSU

C-TMDQSU

C-TMA0

C-MRESETB

C-MDQU4

C-MDQL5

1000pF

C314

C-TMDML

RXC2+

RXC1+

C-TMDQL1

C-MRASB

C-TMDQL7

RXD3+

RXD4+

C-TMA2

1K

1

%

R302

C-TMRASB

C-MDQL3

0.1uF

C305

C-TMCASB

C-MDQU6

C-MDQSUB

C-TMDQU5

C-MCASB

C-MDQU1

C-MA5

RXB3+

RXDCK-

RXD0+

C-TMA7

RXC4-

C-TMDQL1

C-MVREFCA

1K

OPT

R319

RXC2-

C-MDQSL

C-TMCK

C-MDQL6

C-TMDQL6

RXBCK+

RXB2+

C-MDQL4

C-MDQL4

C-TMDQL0

C-MDQU6

C-TMRASB

C-MA0

VCC1.5V_U3_DDR

C-TMA9

C-MA2

C-MVREFCA

C-TMDQU5

C-MA11

C-TMDQU4

C-TMRESETB

RXD0-

VCC1.5V_U3_DDR

0.1uF

C311

C-MODT

C-MDQU5

0.1uF

C315

C-MA4

C-MDQL5

C-TMDQL2

RXA2-

C-TMDQL5

C-MBA1

C-TMDQU0

C-TMA9

1K

1

%

R304

C-TMDQU2

C-MDQU0

RXDCK+

C-MDQU3

DPM_A

C-MDQSLB

C-TMA10

C-MA1

C-MBA2

C-MDQL2

C-MDQL6

0.1uF

C309

RXB0-

RXA4-

C-MA4

C-TMDQL3

C-MA2

0.1uF

C321

C-MBA2

C-TMBA0

RXA2+

C-TMA11

C-TMA8

+1.5V_FRC_DDR

RXD2+

RXD4-

C-MA7

0.1uF

C303

C-MA8

FRC_CONF0

C-MDQL3

C-MWEB

RXC0+

C-TMWEB

0.1uF

C312

RXA1-

RXC0-

C-MCASB

C-MDQU7

FRC_CONF1

C-TMA8

10uF

C301

1000pF

C304

C-MDQL0

C-TMA10

C-MVREFDQ

RXA3+

C-MDQL2

L301

C-MA5

C-TMDQU0

C-MCK

C-MDQU0

C-TMDQL0

1K

R320

C-MA9

RXD1-

RXB3-

C-MCKE

C-TMDQU1

1K

OPT

R321

C-TMDQL6

FRC_PWM1

C-TMBA0

RXACK-

C-MDML

GVDD_ODD

I2C_SCL

C-TMA3

C-MRESETB

0.1uF

C307

C-TMDQSL

C-TMDQU1

C-TMDQL5

C-TMA5

C-TMDQU6

C-TMDMU

1K

OPT

R324

1K

R325

C-TMDQSL

C-MBA1

C-TMDQSUB

VCC1.5V_U3_DDR

FRC_PWM0

C-MWEB

C-MDML

C-MDQL7

0.1uF

C308

V_SYNC

0

R332

VCC1.5V_U3_DDR

10K

R333

10

R314

10

R313

10

R310

10

R308

10

R315

10

R311

10

R316

10

R307

10

R312

10

R309

10

AR302

10

AR309

10

AR303

10

AR306

10

AR305

10

AR301

10

AR307

10

AR308

10

AR304

FRC_SDA

22

R335

OPT

22

R334

OPT

FRC_SCL

0

MINI_LVDS

R336

22

R326

FRC

22

R331

FRC

H5TQ1G63BFR-12C

IC301

FRC_DDR_1600

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

0

R327

0

R328

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX & MS10

FRC_DDR3_A0/DDR2_NC

AE1

FRC_DDR3_A1/DDR2_A6

AF16

FRC_DDR3_A2/DDR2_A7

AF1

FRC_DDR3_A3/DDR2_A1

AE3

FRC_DDR3_A4/DDR2_CASZ

AD14

FRC_DDR3_A5/DDR2_A10

AD3

FRC_DDR3_A6/DDR2_A0

AF15

FRC_DDR3_A7/DDR2_A5

AF2

FRC_DDR3_A8/DDR2_A2

AE15

FRC_DDR3_A9/DDR2_A9

AD2

FRC_DDR3_A10/DDR2_A11

AD16

FRC_DDR3_A11/DDR2_A4

AD15

FRC_DDR3_A12/DDR2_A8

AE16

FRC_DDR3_BA0/DDR2_BA2

AF3

FRC_DDR3_BA1/DDR2_ODT

AF14

FRC_DDR3_BA2/DDR2_A12

AD1

FRC_DDR3_MCLK/DDR2_MCLK

AD13

FRC_DDR3_CKE/DDR2_RASZ

AE14

FRC_DDR3_MCLKZ/DDR2_MCLKZ

AE13

FRC_DDR3_ODT/DDR2_BA1

AE4

FRC_DDR3_RASZ/DDR2_WEZ

AD5

FRC_DDR3_CASZ/DDR2_CKE

AF4

FRC_DDR3_WEZ/DDR2_BA0

AD4

FRC_DDR3_RESETB/DDR2_A3

AE2

FRC_DDR3_DQSL/DDR2_DQS0

AF8

FRC_DDR3_DQSLB/DDR2_DQSB0

AD9

FRC_DDR3_DQSU/DDR2_DQS1

AE9

FRC_DDR3_DQSUB/DDR2_DQSB1

AF9

FRC_DDR3_DML/DDR2_DQ7

AE11

FRC_DDR3_DMU/DDR2_DQ11

AF6

FRC_DDR3_DQL0/DDR2_DQ6

AE6

FRC_DDR3_DQL1/DDR2_DQ0

AF11

FRC_DDR3_DQL2/DDR2_DQ1

AD6

FRC_DDR3_DQL3/DDR2_DQ2

AD12

FRC_DDR3_DQL4/DDR2_DQ4

AE5

FRC_DDR3_DQL5/DDR2_NC

AF12

FRC_DDR3_DQL6/DDR2_DQ3

AF5

FRC_DDR3_DQL7/DDR2_DQ5

AE12

FRC_DDR3_DQU0/DDR2_DQ8

AE10

FRC_DDR3_DQU1/DDR2_DQ14

AF7

FRC_DDR3_DQU2/DDR2_DQ13

AD11

FRC_DDR3_DQU3/DDR2_DQ12

AD7

FRC_DDR3_DQU4/DDR2_DQ15

AD10

FRC_DDR3_DQU5/DDR2_DQ9

AE7

FRC_DDR3_DQU6/DDR2_DQ10

AF10

FRC_DDR3_DQU7/DDR2_DQM1

AD8

FRC_DDR3_NC/DDR2_DQM0

AE8

FRC_REXT

Y11

FRC_TESTPIN

Y19

ACKP/RLV3P/RED[3]

W26

ACKM/RLV3N/RED[2]

W25

A0P/RLV0P/RED[9]

U26

A0M/RLV0N/RED[8]

U25

A1P/RLV1P/RED[7]

U24

A1M/RLV1N/RED[6]

V26

A2P/RLV2P/RED[5]

V25

A2M/RLV2N/RED[4]

V24

A3P/RLV4P/RED[1]

W24

A3M/RLV4N/RED[0]

Y26

A4P/RLV5P/GREEN[9]

Y25

A4M/RLV5N/GREEN[8]

Y24

BCKP/TCON13/GREEN[1]

AC26

BCKM/TCON12/GREEN[0]

AC25

B0P/RLV6P/GREEN[7]

AA26

B0M/RLV6N/GREEN[6]

AA25

B1P/RLV7P/GREEN[5]

AA24

B1M/RLV7N/GREEN[4]

AB26

B2P/RLV8P/GREEN[3]

AB25

B2M/RLV8N/GREEN[2]

AB24

B3P/TCON11/BLUE[9]

AC24

B3M/TCON10/BLUE[8]

AD26

B4P/TCON9/BLUE[7]

AD25

B4M/TCON8/BLUE[6]

AD24

CCKP/LLV3P

AD23

CCKM/LLV3N

AE23

C0P/LLV0P/BLUE[5]

AE26

C0M/LLV0N/BLUE[4]

AE25

C1P/LLV1P/BLUE[3]

AF26

C1M/LLV1N/BLUE[2]

AF25

C2P/LLV2P/BLUE[1]

AE24

C2M/LLV2N/BLUE[0]

AF24

C3P/LLV4P

AF23

C3M/LLV4N

AD22

C4P/LLV5P

AE22

C4M/LLV5N

AF22

DCKP/TCON5

AD19

DCKM/TCON4

AE19

D0P/LLV6P

AD21

D0M/LLV6N

AE21

D1P/LLV7P

AF21

D1M/LLV7N

AD20

D2P/LLV8P

AE20

D2M/LLV8N

AF20

D3P/TCON3

AF19

D3M/TCON2

AD18

D4P/TCON1

AE18

D4M/TCON0

AF18

GPIO0/TCON15/HSYNC/VDD_ODD

AB22

GPIO1/TCON14/VSYNC/VDD_EVEN

AB23

GPIO2/TCON7/LDE/GCLK4

AC23

GPIO3/TCON6/LCK/GCLK2

AC22

FRC_GPIO0/UART_RX

AB16

FRC_GPIO1

AA14

FRC_GPIO3

AC15

FRC_GPIO8

Y16

FRC_GPIO9/UART_TX

AC16

FRC_GPIO10

AC14

FRC_I2CM_DA

AA16

FRC_I2CM_CK

AA15

FRC_I2CS_DA

Y10

FRC_I2CS_CK

AA11

FRC_PWM0

AB15

FRC_PWM1

AB14

H5TQ1G63BFR-H9C

IC301-*1

FRC_DDR_1333_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

K4B1G1646E-HCH9000

IC301-*2

FRC_DDR_1333_SS

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

NT5CB64M16AP-CG

IC301-*3

FRC_DDR_1333_NY

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12

N7

NC_6

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_7

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

DDR3(FRC)

GP2_Saturn7M

V e r . 1 . 4

3 ’ d 5 : b o o t f r o m i n t e r n a l S R A M

3 ’ d 6 : b o o t f r o m E E P R O M

3 ’ d 7 : b o o t f o r m S P I f l a s h

CLose to Saturn7M IC

HIGH : I2C ADR = B8

LOW : I2C ADR = B4

LOW : I2C ADR = B4

(FRC_CONF1,FRC_PWM1, FRC_PWM0)

DDR3 1.5V By CAP - Place these Caps near Memory

CLose to DDR3

<U3 CHIP Config>

Close to DDR Power Pin

(FRC_CONF0)

3

Click on the first or last page to see other 32LD460B (CHASSIS:LJ01Z) service manuals if exist.